什么是SEU現象

由于高能粒子的撞擊,器件的存儲單元內容有可能受到干擾,甚至出現翻轉。這種單個存儲單元的翻轉現象(原有內容為0的變成1;或者原有為1的變成了0)就稱為SEU (Single Event Upset)。

正常情況下,SEU現象不會導致器件的永久性損壞,并且通過重新配置器件即可糾正。但是如果錯誤位置位于設計的核心區域,或者錯誤隨邏輯構建的功能模塊逐級傳遞出去,均會導致設計異常

Xilinx設計的SEM Core

幸運的是,由于SEU現象發生的概率極低,絕大多數普通設計應用并不需要考慮這一問題。但是在航空、航天等高可靠性需求環境下,或者在一些高海拔地區,發生SEU的概率會相應增加。為了及時糾正這種SEU引發功能異常,進一步提高FPGA器件的可靠性,Xilinx開發了Soft Error MitigationCore,簡稱SEM IP。

FPGA內部的存儲單元主要分為4大類:Configuration RAM (CRAM), Block RAM (BRAM), Distributed RAM (DRAM) 以及Flip-Flops(FF)。CRAM用于存儲FPGA的配置數據,也是占比最大的存儲單元模塊。剩下三種的占比依次減少,均可以被用戶邏輯使用。

SEM IP可以通過不間斷地循環掃描FPGA的CRAM,快速檢測出其中是否有存儲單元內容和初始值不一致,并且可以把已經被翻轉的存儲單元的值修復為原來的值。該IP占用資源少,使用方便靈活,可以及時地糾正大多數SEU錯誤,從而避免了重新配置FPGA的麻煩。

需要注意的是,SEM IP并不會掃描監測剩余三種存儲單元。BRAM雖然也是數量較多的存儲單元模塊,但Xilinx的BRAM可以開啟自帶的ECC校驗功能,糾正SEU或者其他問題導致的數據錯誤。另外,DRAM和FF的數量相對來說比較少,疊加考慮SEU現象發生的極低概率,這兩部分的SEU問題一般可以安全忽略。

入門案例簡介

下面我們就基于KCU116開發板,介紹一下如何在設計中加入一個最基本功能的SEM IP,從而開啟芯片的SEU檢測功能。

1.IP生成

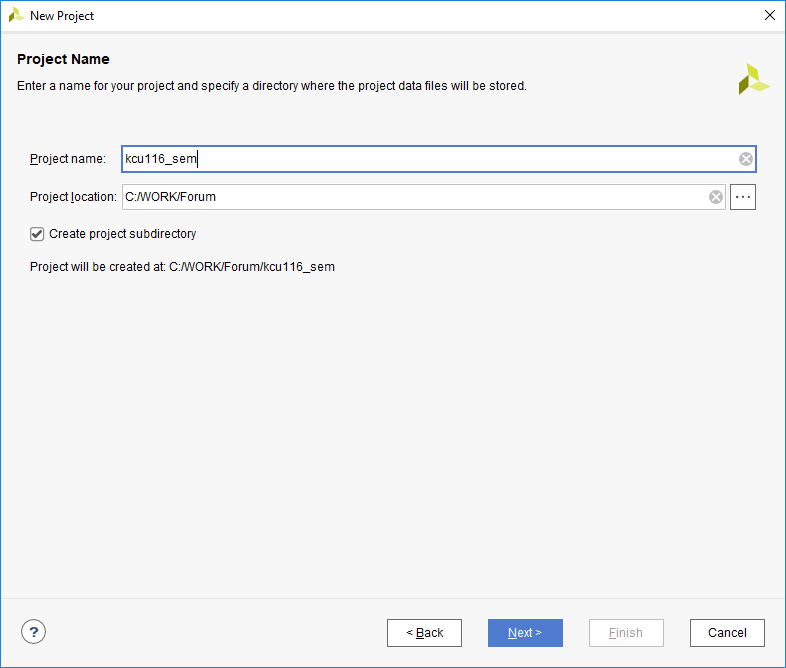

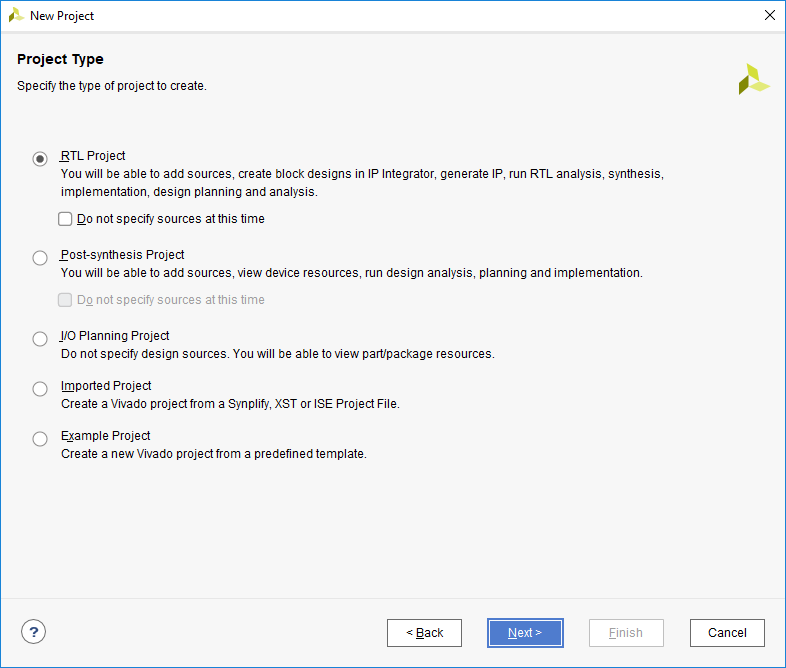

a. 打開Vivado, 基于KCU116建立一個新的空白RTL工程;

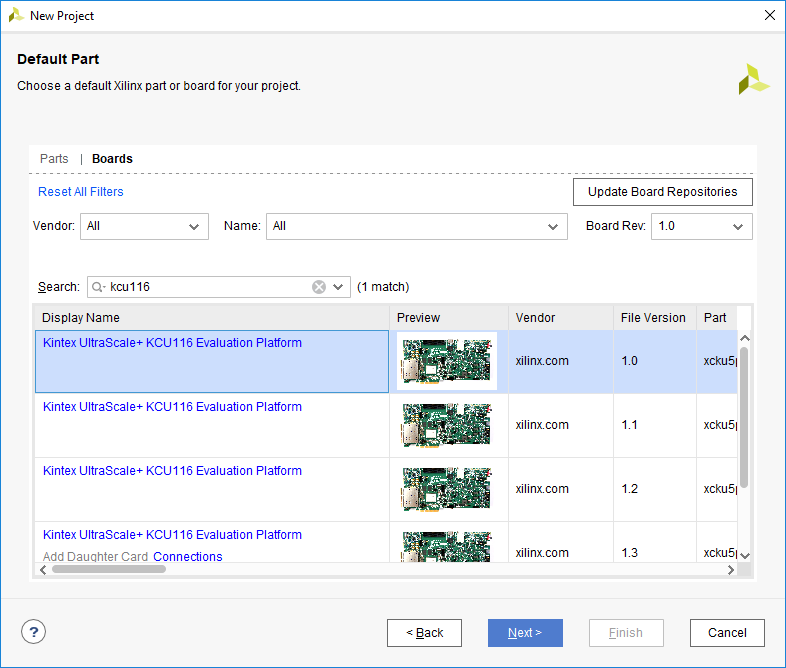

b. 選擇所使用的FPGA的型號,或者選擇所開發板的型號。這里我們選擇KCU116,Rev 1.0.

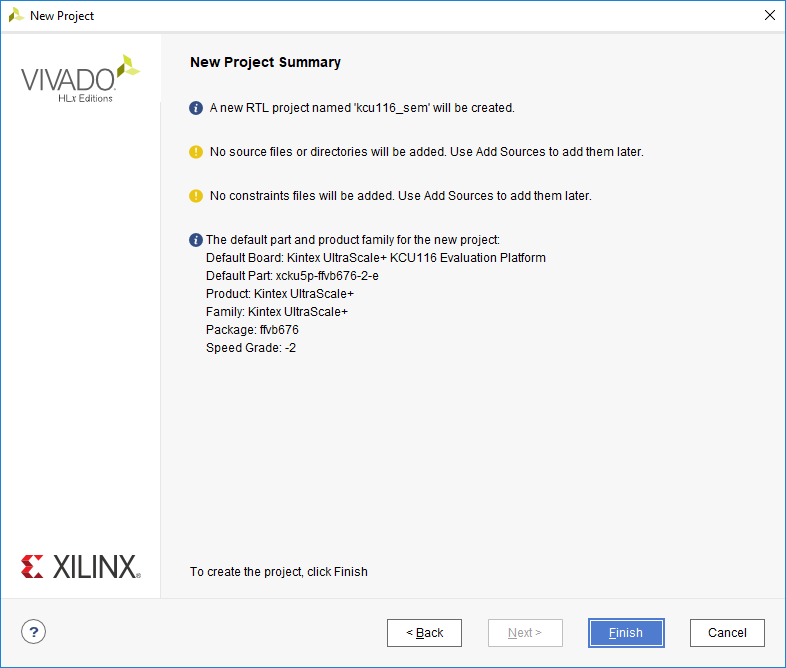

c. 確認器件信息,生成新的工程。

d. 在PROJECT MANAGER的IP Catalog中,選擇FPGA Features andDesign-> Soft Error Mitigation -> UltraScale Soft Error Mitigation, 雙擊打開。

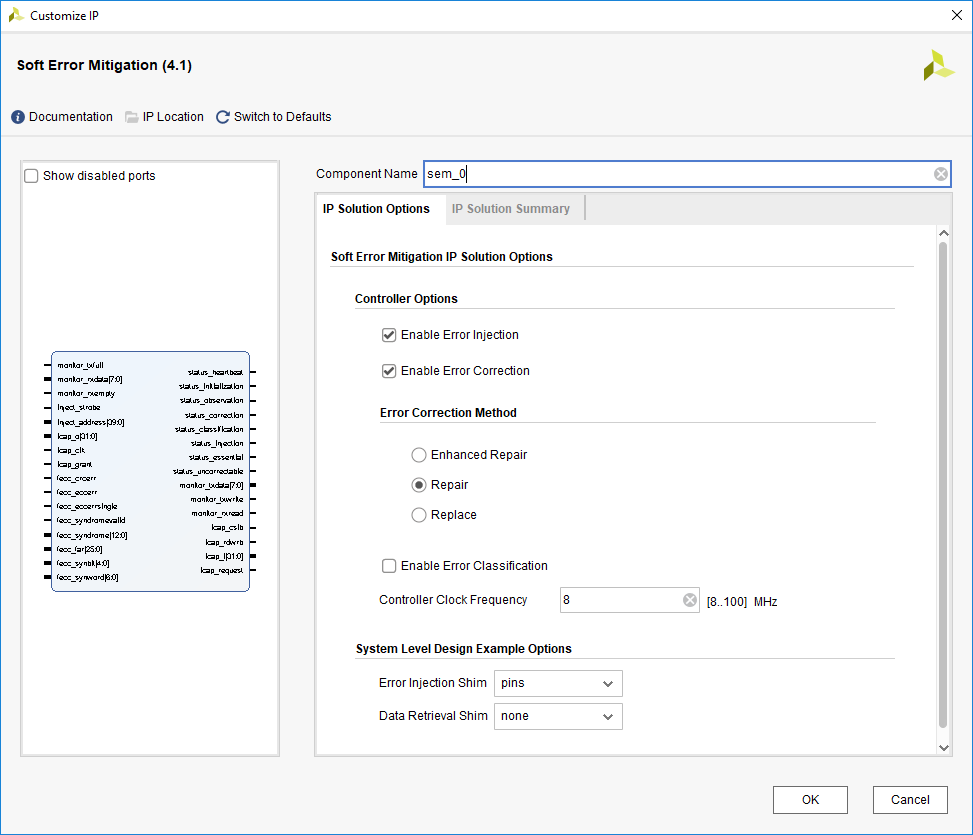

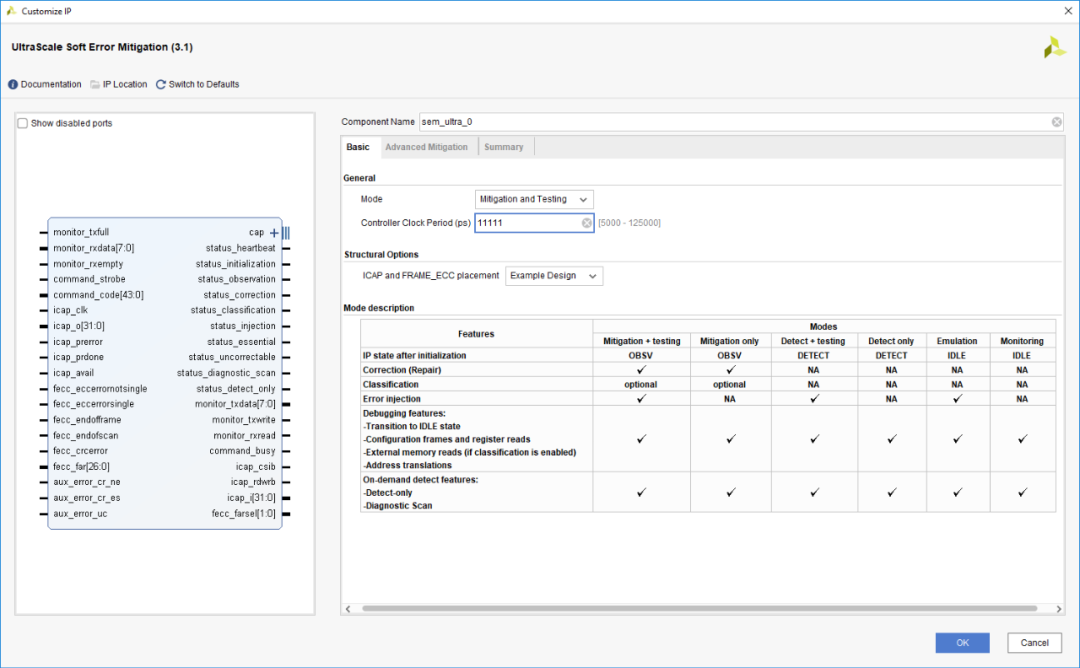

KCU116開發板上是一塊XCKU5P-2FFVB676E,對應的IP名稱為UltraScale Soft Error Mitigation(3.1)。如果你使用的是其他芯片,那么SEM IP的名稱會有所不同,比如7系列的芯片就是Soft Error Mitigation (4.1). 界面和功能會略有不同:

IP的基本默認設置如下圖所示:

SEM IP有多種工作模式,設計里面最常用的就是 ‘Mitigationand Testing’。這個模式和其他模式包含的功能如頁面中表格所示。Mitigation andTesting 包含了最基本的糾錯功能,和驗證IP能否正常工作,模擬SEU事件的Error injection功能。此外還支持一些有用的調試命令,比如說讀取一些寄存器等等。這里我們就選擇這種模式。

Controller Clock Period (ps),是以ps為周期的單位來選擇SEM IP工作的時鐘。時鐘頻率越高,糾正錯誤的速度越快。UltraScale+系列根據型號不同,支持的最高頻率可以高達200MHz。考慮KCU116開發板有自帶的90MHz的時鐘,這里我們選擇11111ps。

注意,SEM IP一般要求有獨立時鐘,即它的工作時鐘最好不要同時用來驅動其他邏輯。

其他設置使用默認設置。生成IP。

2. 生成Example Design

SEM IP與其他IP不太一樣的地方,是我們建議你完整地把SEM IP的整個參考設計并入用戶設計中,而不是僅僅添加一個xci核。參考設計正確地建立了與底層核心硬核ICAP和FRAME_ECC的連接,并且加入了非常有用的一些調試手段,比如VIO,可以觀測IP的實時工作狀態;比如串口模塊,可以方便地實現和IP的交互以及調試。在入門應用或者對于資源沒有非常緊張的應用中,直接使用參考設計是最保險的做法。當然,產品中可以把主要針對調試的串口模塊去掉。

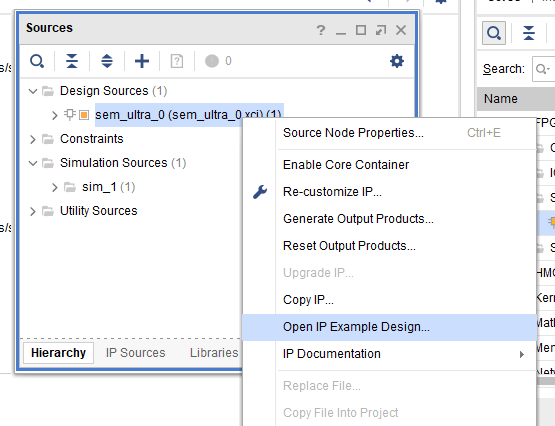

a.這里選擇右鍵單擊xci文件,選擇‘Open IP Example Design

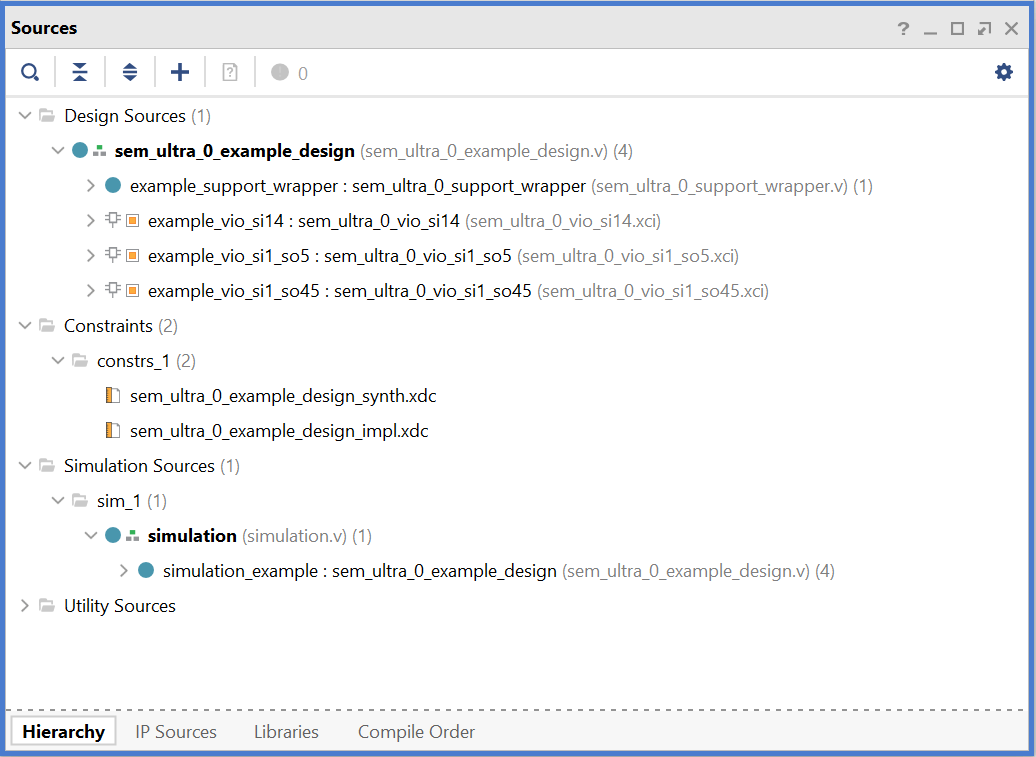

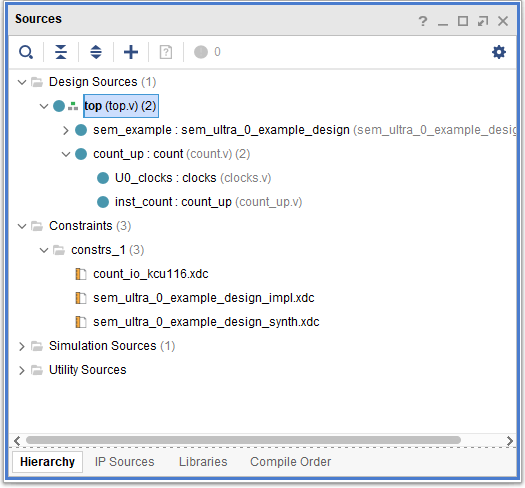

b. 觀察Example Design,其包含了IP 的頂層wrapper文件,一些輔助模塊(串口,VIO等),以及約束文件以及仿真文件。

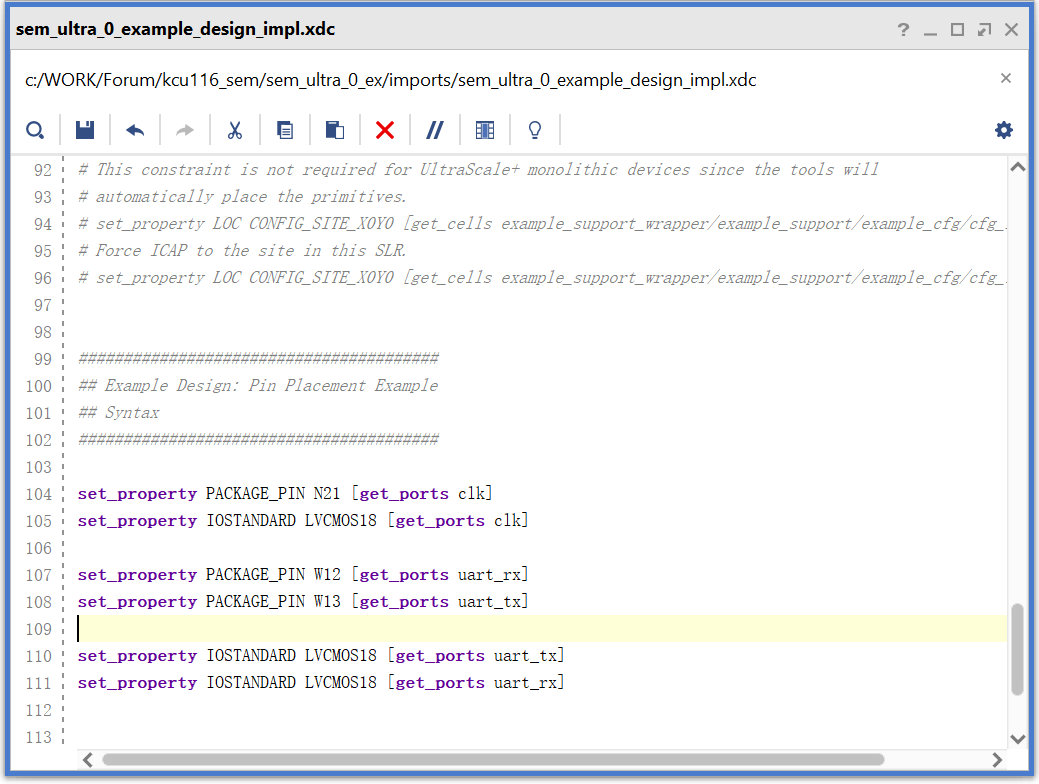

c. 為了保證timing的正確,注意保持所有原有的位置以及timing等約束。根據自己PCB的設置,分配一下sem_ultra_0_example_design_impl.xdc里面時鐘和串口的管腳。

d. 編譯工程,生成用于下載的bit文件。

3.下載測試

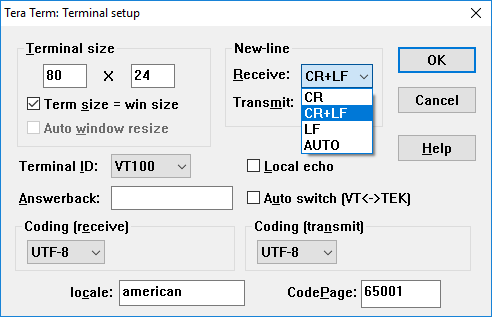

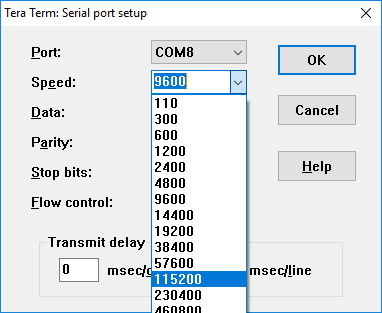

a. 使用micro-USB下載線連接PC和KCU116的JTAG接口,這是為了通過JTAG接口下載配置bit文件。同時使用另外一根micro-USB連接PC和KCU116的USB-UART接口,打開PC上的Tera Term軟件,連接Standard COM Port并做如下設置:

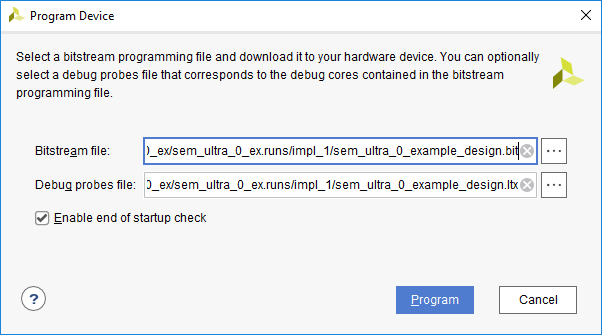

b. 通過HW Manager掃描到VU5P器件,下載bit文件。

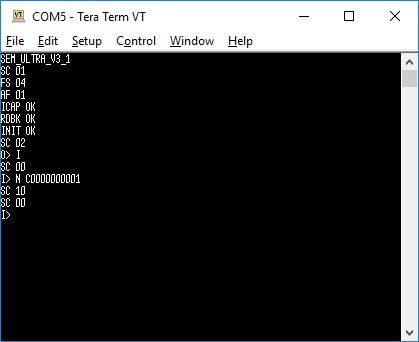

c. 下載成功后,首先可以看到Tera Term上出現了SEM正確初始化的信息:

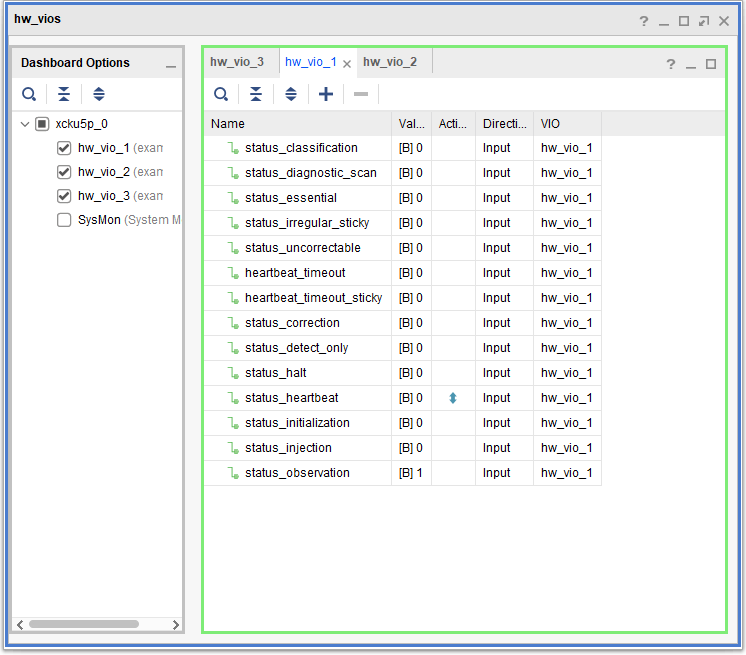

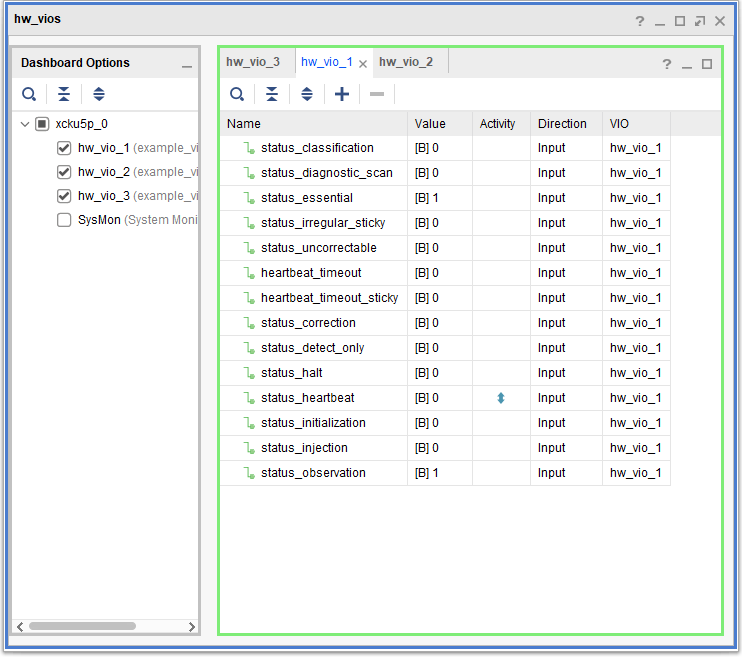

d. Vivado的Dashboard中,共出現了三個hw_vio_x界面。選中其中的+號,把預先定義好的信號添加進去。

這個界面顯示的是IP當前的狀態。IP在初始化過程結束后,其status_initialization信號會從高變低,隨之進入工作狀態status_observation,該信號由低變高。此狀態正常應該情況下會看到status_heartbeat信號是一個不斷toggle的狀態。

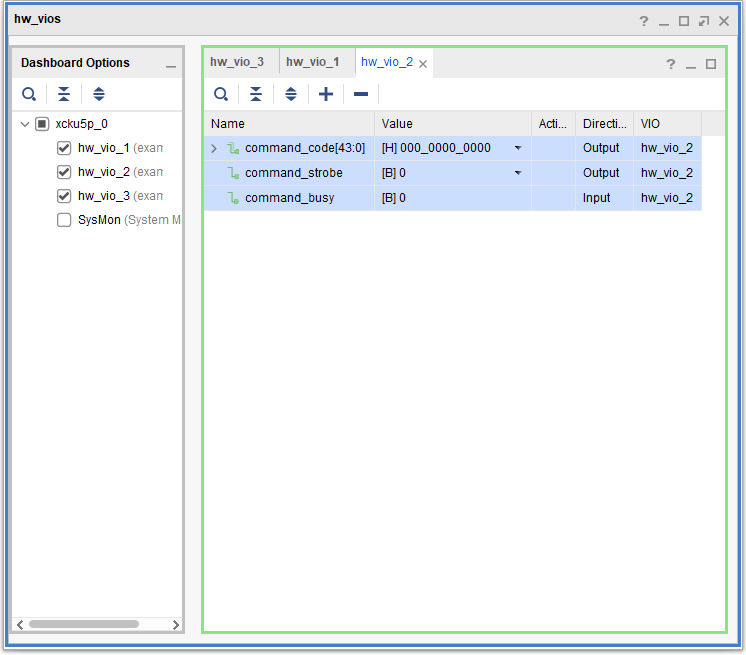

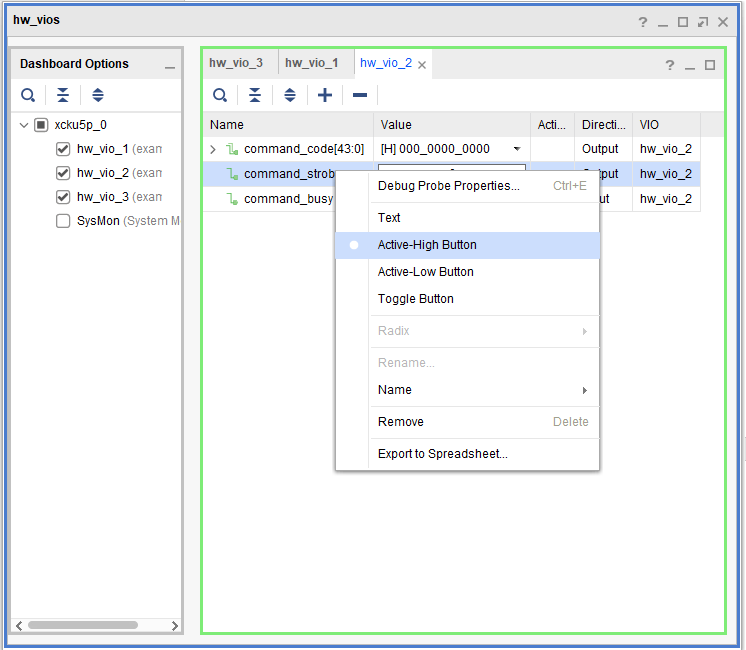

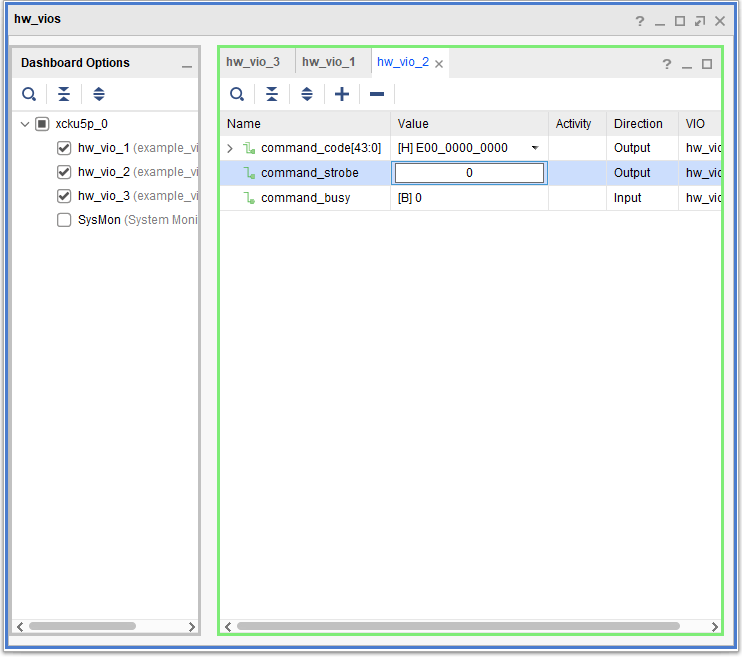

這個界面提供了和IP交互的命令行界面。我們這里為了方便,一般把command_strobe,即命令使能信號,做成一個高有效按鈕。

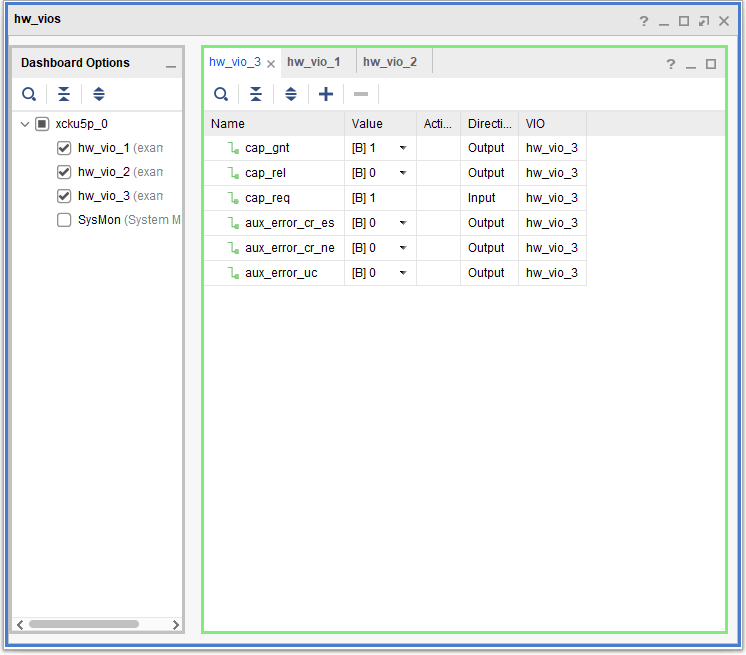

一般我們用hw_vio1和hw_vio2就足夠了。hw_vio3是用于IP和其他控制邏輯分配資源等的一些控制信號,這里不會用到。

此時的IP已經在正常工作,監測設計的SEU狀態了。IP位于哪個狀態,那么狀態信號status_*就會相應的拉高。

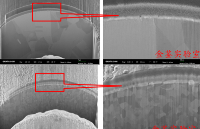

4. 糾錯功能驗證

如果芯片遭受到了高能粒子轟擊并且存儲單元出現了內容反轉,IP會從observation狀態退出,表現為status_observation拉低,status_correction被拉高開始糾錯工作。如果糾錯成功,IP會重新進入status_observation狀態繼續工作。由于我們并未開啟高級的錯誤分類功能,所有位置的錯誤都會被IP認定為是關鍵位置。因此status_essential信號會被置高并保持不變。

由于真實的SEU事件及其稀少,我們如何能斷定IP是否已經正常工作,并且能及時糾正錯誤呢?SEMIP提供了一個模擬錯誤注入功能,即Error Injection。下面我們來進行一次單bit注入測試。

a.打開hw_vio2, 由于模擬錯誤注入需要先把IP切換到IDLE狀態,我們需要先在command_code輸入E00_0000_0000,然后按一下command_strobe按鈕。

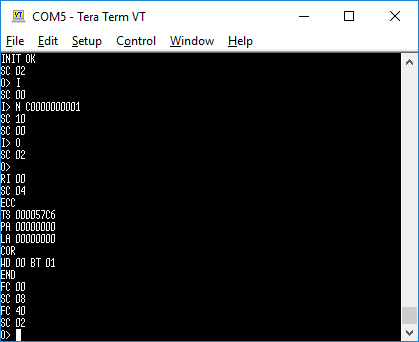

b. 在串口輸出上,可以觀測到這一過程,IP已經從觀測狀態O,進入了IDLE狀態I:

等待command_busy上面顯示的箭頭消失后,說明該命令已經執行完畢,可以輸入下一條命令了。

c. command_code輸入 C00_0000_0001,這是IP的插錯指令,表示在存儲單元address 0x1上,進行內容的反轉。除了第一個hex字符表示插錯指令,后面10個hex字符用于填寫插錯的地址。按一下command_strobe按鈕;此時對應串口的顯示。

d.由于IP只有在Observation狀態才能檢測錯誤并且糾正錯誤,所以我們還需要使用指令A00_0000_0000,使IP回到正常工作狀態:

e. 觀測IP的狀態信號,如下:

可以看到status_heartbeat又恢復了跳動;status_observation再次拉高;status_essential信號由于沒有開啟高級的錯誤分類功能,因此被置為高。

相應的串口也有詳細的報告報出,包括錯誤的具體地址:

至此,基本的SEM IP的功能均以得到驗證。

5. 合入原有設計

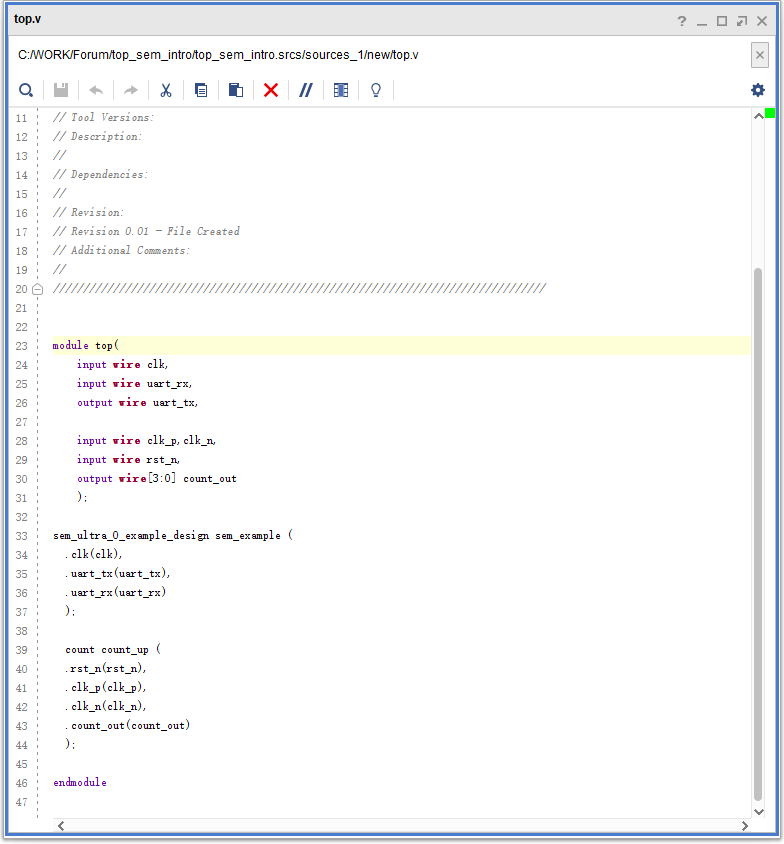

現在只要把這個SEM IPexample完整合入你原來的工程了。這里提供一個簡單的demo設計,本身的功能是按一定次序循環點亮開發板上的LED燈。只要給這個設計再添加一個頂層top文件,把原有LED點亮的設計和SEM IP example調用合入即可。如下圖:

重新編譯,開啟了SEU保護的整個設計就完成了。

結 語

本文介紹了如何把一個具有最基本檢錯糾錯功能的SEM IP合入到你的設計當中去。觀測SEMIP的狀態輸出信號,或者查看串口打印的報告,你就已經可以知道設計當前是否正常運行,還是已經出現了SEU錯誤,并且相應做出正確決策了。

對于絕大多數設計來說,這一基本功能就已經完全夠用。你的設計已經開啟了SEU保護,可以應對90%以上的SEU事件了。

-

Xilinx

+關注

關注

73文章

2201瀏覽量

131202

原文標題:開發者分享 | 如何開啟FPGA中的最基本的SEU檢錯糾錯功能

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【飛凌嵌入式RV1126B開發板】+基本功能測試篇(2)

【飛凌嵌入式RV1126B開發板】+基本功能測試篇(1)

單片機基本功能

FIB-SEM雙束系統:微納尺度的一體化解決方案

lwip如何實現運行中修改ip地址并使新的地址生效?

AMD Vivado IP integrator的基本功能特性

調用sys_sem_free()時異常的原因?

FIB-SEM雙束系統的工作原理與應用

FIB - SEM 技術在半導體芯片領域的實踐應用

SEM IP在MPSoC器件上的使用指南

SEM與TEM該如何選擇?

鴻蒙地圖功能開發【1. 開發準備】##地圖開發##

案例展示||FIB-SEM在材料科學領域的應用

如何在設計中加入一個最基本功能的SEM IP

如何在設計中加入一個最基本功能的SEM IP

評論