CMOS電路因其在在功耗、抗干擾能力方面具有不可替代的優勢,以及在設計及制造方面具有簡單易集成的優點而得到廣泛應用。如今,在大規模、超大規模集成電路特別是數字電路中早已普遍采用CMOS工藝來來進行設計與制造。

一、CMOS門電路設計規則

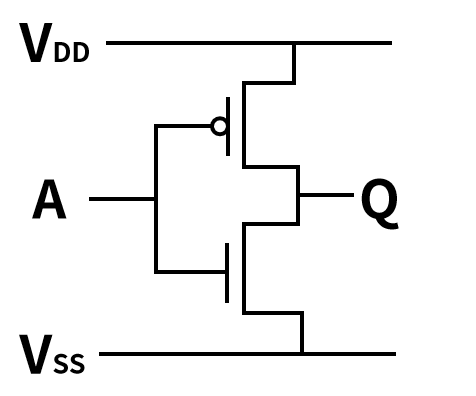

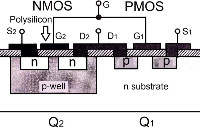

靜態的CMOS電路的設計有著一定的規則,而正是這些規則使得其電路的設計變得非常簡單。如圖所示,COMS電路中最主要的部分是上拉網絡PUN(Pull Up Net)和下拉網絡PDN(Pull Down Net),這兩個網絡內部結構是對稱互補的,或者說是對偶的。所謂的對稱互補,即是指下拉網絡中全是NMOS,而上拉網絡中全是PMOS,兩者數量相同;并且,下拉網絡中組成“與”邏輯的MOS管,在上拉網絡中對應的為“或”邏輯,在下拉網絡中組成“或”邏輯的MOS管,在上拉網絡中對應的為“與”邏輯。由于互補,上拉網絡與下拉網絡不會同時導通。

由于結構是互補對稱的,CMOS電路的功能可以由下拉網絡或者上拉網絡單獨來確定。對于下拉網絡,先根據各個NMOS的串并聯關系列出表達式,最后整體取反一下(取反是因為下拉網絡為真時輸出是低電平0);對于上拉網絡,先將各個輸入取反,再根據各個PMOS的串并聯關系寫出表達式。其中,串聯為與,并聯為或。

設計的過程則剛好反過來,先根據功能確定邏輯表達式,再選擇下拉網絡或者上拉網絡中的一個作為切入點,根據與或關系確定MOS管的串并聯,將其中一個網絡畫出來,最后根據互補關系畫出另外一個網絡。

二、CMOS異或門的設計舉例

下面以異或門為例,討論一下CMOS異或門的設計方法以及其中的一些技巧。

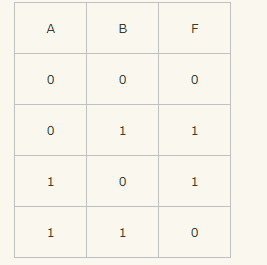

(1)確定功能。可以根據真值表、時序圖等來確定。下表為異或門的真值表,當兩輸入信號相同時,輸出為低電平;輸入不同時,輸出為高電平。

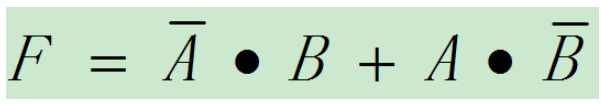

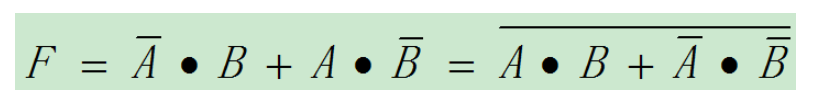

(2)確定邏輯表達式。異或門的邏輯表達式 :

(3)畫出下拉或上拉網絡。以下拉網絡為切入點,這時要先對表達式處理一下,變為某個式子的非的形式,因為下拉網絡算出來的表達式最后要取反一下:

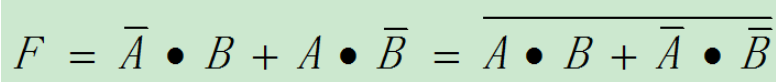

這樣,就可以根據大非號下面的式子來搭建PDN電路:

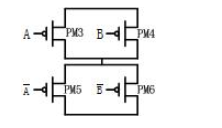

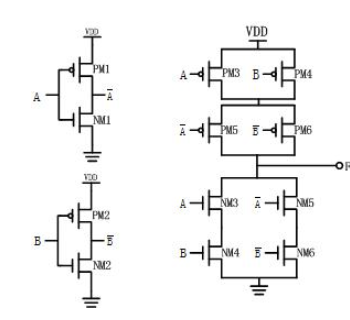

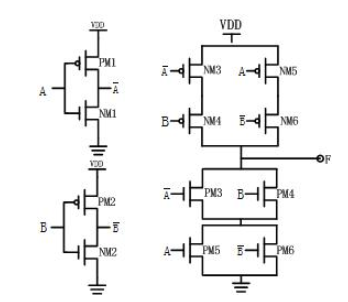

如圖所示,由于A和B是與的關系,所以連接A和B的MOS管NM3和NM4要串聯,和也是如此。由于與是或的關系,所以由NM3、NM4組成的串聯和NM5和NM6組成的串聯最后要并聯在一起。至此下拉網絡設計完成。

(4)根據互補關系確定另外一個網絡。

這一步就比較簡單了,在PDN中A和B對應的MOS管是串聯的,那么在PUN中就變成并聯的,即PM3和PM4;和同樣;最終將兩個并聯組合串聯起來。

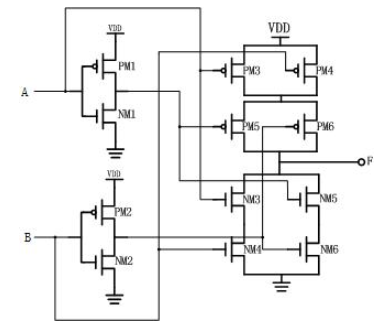

(5)將PDN和PUN組合起來,加上電源和地,如圖:

圖中左側是兩個反相器,用于產生非信號。

為了便于分析,圖中的連線都是用標號代替的,下圖是一個完整的電路:

至此,一個完整的CMOS異或門電路設計完成。當然,后續還會有MOS管寬長比、摻雜等方面的設計,這些不在這里討論。

三、另一種設計思路

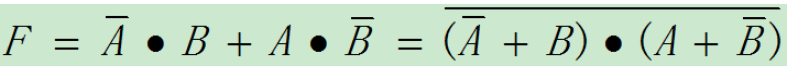

以上是根據表達式:

來進行設計的,對上式進行變換可以得到:

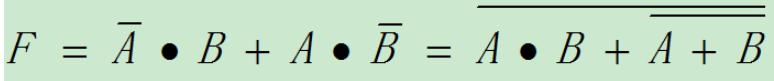

根據這個式子可以設計出與上例不同的電路:

該電路與前一種電路實現相同功能,只是在結構上PUN和PDN與前一種電路互換了一下,沒有本質上的區別。

四、優化設計

下面介紹一種優化設計方法。

繼續對異或門的邏輯表達式進行變換,得到:

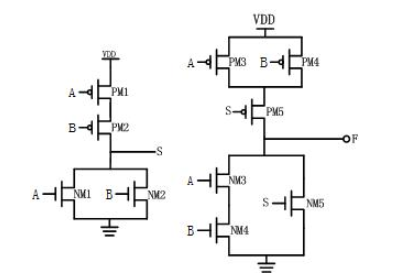

這里,將A與B的非作為一個整體,用一個獨立的與非門來實現,電路圖如圖所示:

可以看到,前面兩種電路都用了12個MOS管,而這個電路只用了10個MOS管就實現了異或門的功能。可別小看減下來的這兩個MOS管,在大規模集成電路設計中,這種門電路的使用是非常普遍的,若是一個系統中能有百十個這樣的門電路,那這種優化在減小芯片面積和降低成本方面將會為產品帶來非常大的優勢。

下面分析一下這樣優化的原理。前兩種電路中,邏輯表達式都包含了A、B、A非、B非四種信號,但是電路的原始輸入只有A和B兩種,因此要搭建產生A非和B非的電路,也就是搭建兩個非門。而每個非門需要兩個MOS管,所以產生A非和B非需要額外的四個MOS管。加上實現邏輯表達式功能的8個MOS管,一共12個。

而在第三種電路中,變化邏輯表達式消去了A非和B非,用A與B的非來代替,只需額外設計一個與非門,4個MOS管。由于A與B的非作為一個信號進行運算,相當于邏輯表達式中只有三個輸入,一共需要6個管子,加起來一共10個。

也就是說,在邏輯表達式中,若果能夠將信號合并使得輸入端出現盡可能少的信號種類,那么就有可能減少整個門電路的MOS管個數。

-

CMOS

+關注

關注

58文章

6217瀏覽量

242891 -

反相器

+關注

關注

6文章

332瀏覽量

45197 -

數字電路

+關注

關注

193文章

1651瀏覽量

83360

發布評論請先 登錄

集成電路制造工藝中的刻蝕技術介紹

數字電路中CMOS工藝進行設計與制造技術

數字電路中CMOS工藝進行設計與制造技術

評論