DDS信號發生器采用直接數字頻率合成(Direct Digital Synthesis,簡稱DDS)技術,把信號發生器的頻率穩定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內進行精細的頻率調節。采用這種方法設計的信號源可工作于調制狀態,可對輸出電平進行調節,也可輸出各種波形。

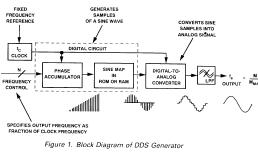

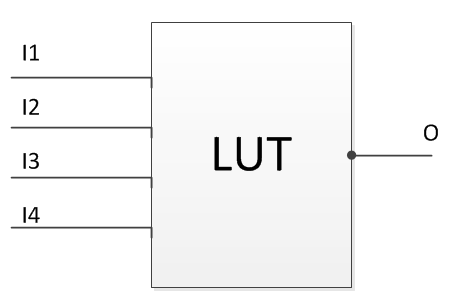

DDS(Direct Digital Synthesis)直接數字頻率合成技術由USA J.Tierncy首先提出。它是一種以數字信號處理理論為基礎,從相位概念出發直接合成所需波形的一種新的全數字技術的頻率合成方法。DDS主要出現在數字混頻系統中。在數字混頻中,通過DDS產生正交的本地振蕩信號即正、余弦信號與輸入信號相乘實現頻譜搬移,如通信系統的調制、解調。目前FPGA實現DDS有三種途徑:基于IIR濾波器的實現方法、基于查找表LUT的實現方法以及基于CORDIC算法的實現方法。其中采用LUT的方法較為通用且比較容易實現。

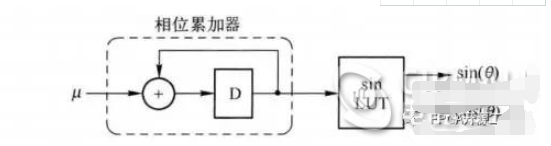

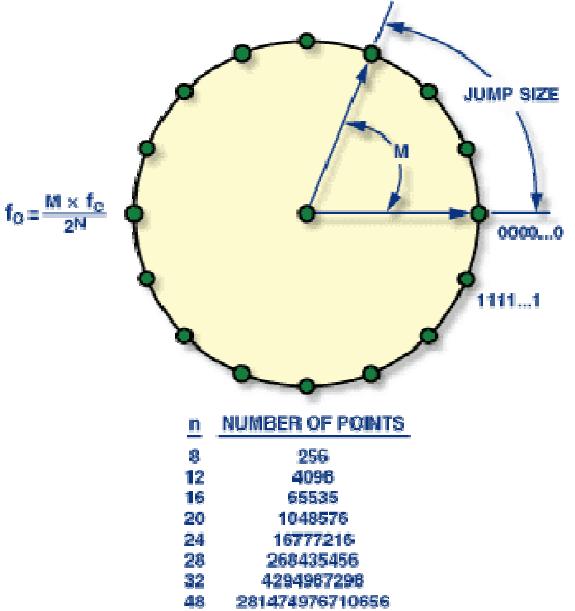

一個典型的基于LUT的DDS系統由相位累加器和波形存儲器兩部分構成,如圖1所示。圖中相位累加器的位寬為nbit,步進值為μ,LUT的深度N為2n,寬度為Lbit。LUT中依相位順序存儲一個周期的波形數據。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

DDS

+關注

關注

22文章

684瀏覽量

156583 -

LUT

+關注

關注

0文章

52瀏覽量

13142

發布評論請先 登錄

相關推薦

熱點推薦

初識FPGA CLB之LUT實現邏輯函數

LUT中文名字叫查找表。以7系列的FPGA為例,每一個Slice里面有四個LUT。FPGA就是通過LUT實現大量的組合邏輯,以及SLICEM里面的LUT還可以構成RAM,Shift R

使用的LUT觸發器對的數量與Slice Register和Slice LUT的關系是什么?

想要了解以下術語的確切含義:“使用的LUT觸發器對的數量”“帶有未使用的觸發器的號碼”“帶有未使用LUT的數字”“最常用的LUT-FF對的數量”“獨特控制集的數量”什么是7系列的“LUT

發表于 10-23 10:21

如何使用DDS IP核生成任意波形?

一個DDS應用,我想使用Xilinx DDS IP內核生成任意波形,但我看到的是DDS只能生成正弦或余弦波形數據。你知道如何用其他數據替換正弦波形LUT嗎?如果可以修改該

發表于 02-12 08:07

LUT名字的數字含義是什么?

嗨,我是FPGA設計數字系統的初學者。我對合成的結果有疑問。當我設計一個簡單的15位2輸入加法器或11位3輸入加法器時,合成結果示意圖有LUT6,LUT2,CARRY4嵌段。我知道LUT

發表于 05-25 09:22

DDS,什么是DDS,DDS的結構

DDS,什么是DDS,DDS的結構

DDS概述

直接數字式頻率綜合器DDS(Direct Digital Synthesizer),

發表于 09-03 08:42

?5054次閱讀

DDS是什么意思,DDS結構,DDS原理是什么

DDS是什么意思,DDS結構,DDS原理是什么

什么叫DDS

直接數字式頻率合成器DDS(Direct Digital Synthesi

發表于 03-08 16:56

?4.8w次閱讀

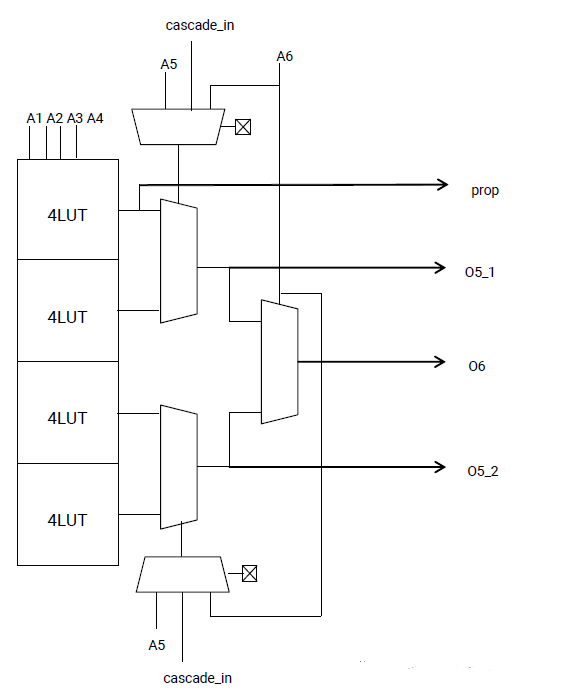

LUT如何構成邏輯函數

LUT如何如何構成邏輯函數;2個LUT通過互連可以構成7bit輸入,單bit輸出的邏輯。實現方式為兩個LUT的輸入信號A1,A2,A3,A4,A5,A6接到一起,輸出信號經過選擇器選擇輸出,選擇器的選擇信號也是邏輯函數的一個輸入

物理可級聯的LUT的優勢在哪?

在Versal ACAP中,同一個CLB內同一列的LUT是可以級聯的,這是與前一代FPGA UltraScale+系列的一個顯著不同點。這里我們先看看Versal中LUT的結構,如下圖所示(圖片來源

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

因為當輸入數據的位數遠大于一個LUT的輸入時,就需要用多個LUT級聯來實現邏輯,那么級聯產生的延時也就不可避免了,這樣就會制約系統的運行頻率。那么為了避免級聯數過于多,就采用插入寄存器的方法來實現

MAX6828LUT+T PMIC - 監控器

電子發燒友網為你提供Maxim(Maxim)MAX6828LUT+T相關產品參數、數據手冊,更有MAX6828LUT+T的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MAX6828LUT+T真值表,MAX6828

發表于 12-21 23:30

基于LUT的DDS系統設計原理

基于LUT的DDS系統設計原理

評論