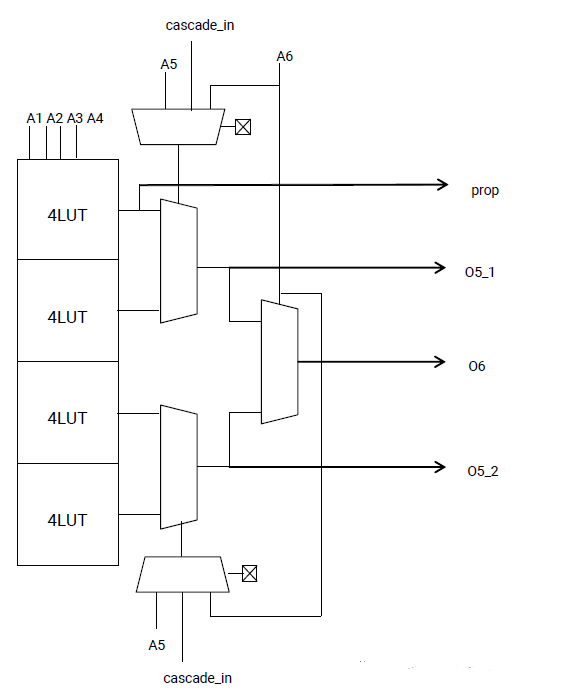

在Versal ACAP中,同一個CLB內同一列的LUT是可以級聯(lián)的,這是與前一代FPGA UltraScale+系列的一個顯著不同點。這里我們先看看Versal中LUT的結構,如下圖所示(圖片來源:Figure4, am005)。

可以看到,一個LUT6(6輸入LUT)是由4個LUT4(4輸入LUT)外加一些MUX(數(shù)據(jù)選擇器)共同構成。同時,LUT6有4個輸出端口。其中,prop端口只有在LUT用作進位邏輯時使用,且在CLB外部不可見。用做6個輸入的邏輯函數(shù)發(fā)生器時,輸出在O6端口;雙LUT5模式時,輸出在O5_1和O5_2端口。同時還可以注意到,多了一個級聯(lián)端口cascade_in,該端口用于與前一級LUT的O6輸出相連接。級聯(lián)端口不需要手工連接,工具會自動判斷是否使用該端口。

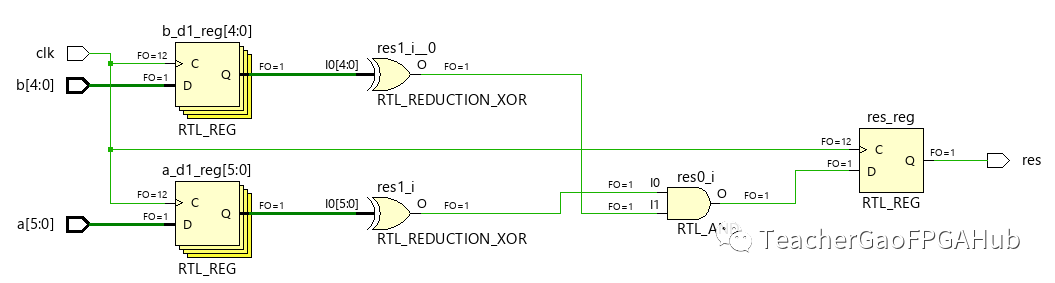

我們看一個具體的案例,如下圖所示。輸入a為6bits,b為5bits,a/b分別執(zhí)行異或位縮減運算(^a,^b),然后再將兩者結果執(zhí)行邏輯與。顯然a的異或位縮減運算會占用一個LUT6,b的異或位縮減運算與后續(xù)的與門共同消耗一個LUT6。

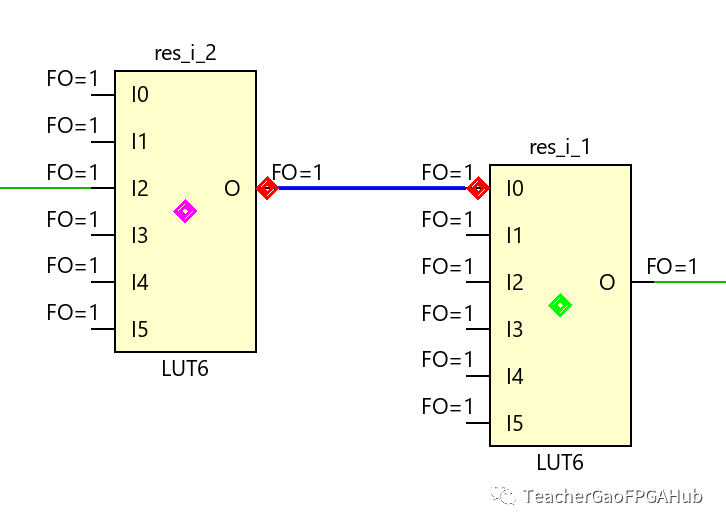

上述電路圖布線后打開Schematic視圖,鎖定其中的兩個LUT6,如下圖所示。

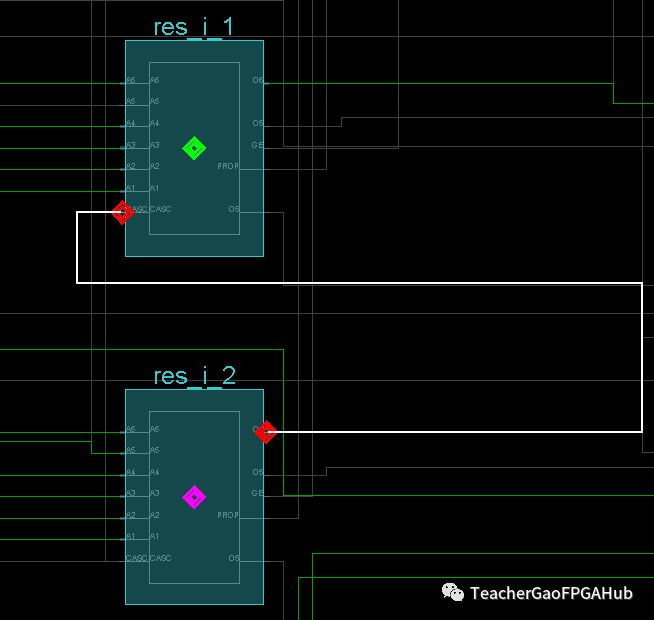

進一步在Device視圖中可以看到具體的物理連接方式,如下圖所示。可以看到圖片下方的LUT由O6輸出,并連接到上方LUT的級聯(lián)端口。

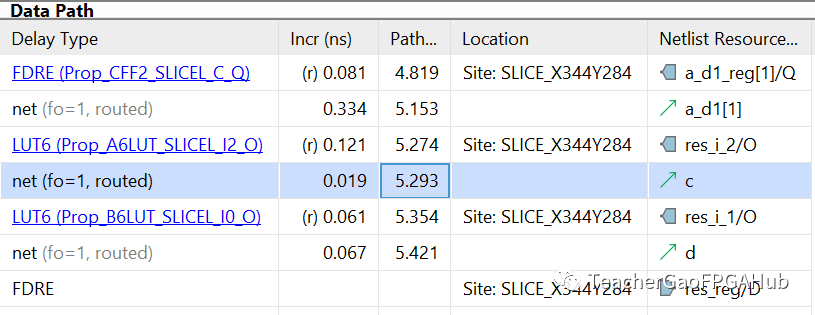

再從時序角度看,這里我們設定時鐘頻率為600M,在時序報告中,可以看到這部分的延遲(兩個LUT之間的布線延遲)為0.019ns。整個設計的WNS為0.923ns。

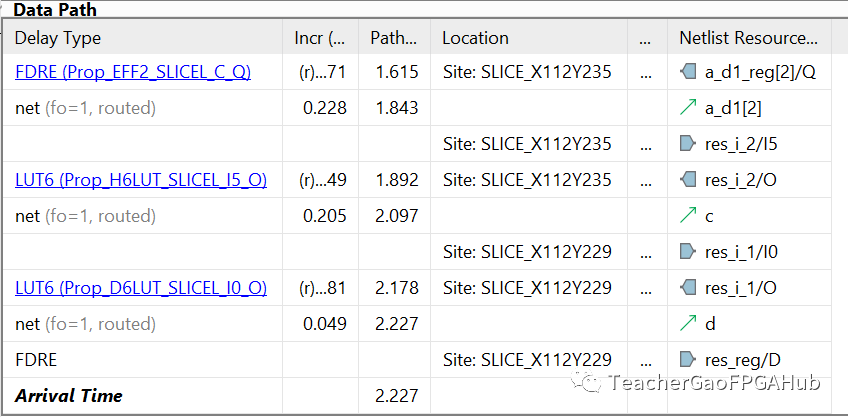

同樣的設計,如果在UltraScale+中執(zhí)行,結果如下圖所示,可以看到兩個LUT相距很遠,因為UltraScale+中的LUT是不支持級聯(lián)的,這就要消耗CLB外部的布線資源。

從時序角度看,這部分的延遲為0.205ns,顯然大了很多。

綜上所示,我們可以得出如下結論:

LUT的級聯(lián)可以有效降低關鍵路徑上的延遲,同時減少CLB外部布線資源的消耗。這對于緩解布線擁塞非常有利。還要注意的是這種級聯(lián)僅限于同一個CLB中的同一列LUT,且級聯(lián)方向由下至上,這意味著級聯(lián)所用到的布線資源都在CLB內部,而不會消耗CLB外部布線資源。

編輯:jq

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638513 -

LUT

+關注

關注

0文章

52瀏覽量

13192 -

CLB

+關注

關注

0文章

30瀏覽量

6372

原文標題:物理可級聯(lián)的LUT到底有什么優(yōu)勢?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

MAX11040K/MAX11060:24/16位、4通道、同時采樣、可級聯(lián)Sigma - Delta ADC深度解析

K-1000C LED控制系統(tǒng)無線級聯(lián)改造 ——基于 LoRa611II 的級聯(lián)通信替代方案

K-1000C LED控制系統(tǒng)無線級聯(lián)改造 ——基于思為無線的級聯(lián)通信替代方案

ADM1266:可級聯(lián)超級定序器的全面解析

探索 MAX4821:8 通道可級聯(lián)繼電器驅動器的卓越性能

MAX4820:8通道可級聯(lián)繼電器驅動器的技術剖析

解析MAX4820/MAX4821:8通道可級聯(lián)繼電器驅動器

MAX4820/MAX4821:8通道可級聯(lián)繼電器驅動器的卓越之選

A2CP14216級聯(lián)放大器Teledyne防務電子

基于級聯(lián)分類器的人臉檢測基本原理

AES和SM4算法的可重構分析

InGaP 級聯(lián)放大器 0.1–3 GHz skyworksinc

InGaP 級聯(lián)放大器 0.1–6 GHz skyworksinc

0.1 -7 GHz InGaP 級聯(lián)放大器 skyworksinc

Simcenter STAR-CCM+電磁學:多物理場環(huán)境下快速、可擴展的電磁分析工具

物理可級聯(lián)的LUT的優(yōu)勢在哪?

物理可級聯(lián)的LUT的優(yōu)勢在哪?

評論