清華大學基于多個憶阻器陣列的全硬件完整存算一體系統,能夠高效的運行卷積神經網絡算法,證明了存算一體架構全硬件實現的可行性,對今后AI算力瓶頸的突破有著極大意義。

集微網消息,近日來,清華大學微電子學研究所、未來芯片技術高精尖創新中心的錢鶴、吳華強教授團隊與合作者在《自然》在線發表了題為“Fully hardware-implemented memristor convolutional neural network”的研究論文,報道了基于憶阻器陣列芯片卷積網絡的完整硬件實現。該成果所研發的基于多個憶阻器陣列的存算一體系統,在處理卷積神經網絡時的能效遠高于GPU,大幅提升了計算設備的算力,成功實現了以更小的功耗和更低的硬件成本完成復雜的計算。

隨著以人工智能為代表的信息技術革命興起,基于各種深度神經網絡的算法可以實現圖像識別與分割、物體探測以及完成對語音和文本的翻譯、生成等處理。然而深度神經網絡算法是一類以數據為中心的計算,實現該算法的硬件平臺需要具有高性能、低功耗的處理能力,這就對集成電路芯片技術提出了的更高要求。目前傳統實現該算法的硬件平臺是基于存儲和計算分離的馮諾依曼架構,這種架構在計算時需要將數據在存儲器件和計算器件之間來回搬移,因此在包含大量參數的深度神經網絡的計算過程中,該架構的能效較低。為此,開發一種新型計算硬件來運行深度神經網絡算法成為當前亟需解決的問題。

基于這種情況,清華大學團隊于2019年11月7日提出一項名為“基于憶阻器的神經網絡的并行加速方法及處理器、裝置”的發明專利(申請號:201911082236.3),申請人為清華大學。此專利針對復雜神經網絡的運算,提供了一種基于憶阻器的存算一體化架構和并行加速方法,并在該系統架構上高效運行了卷積神經網絡。

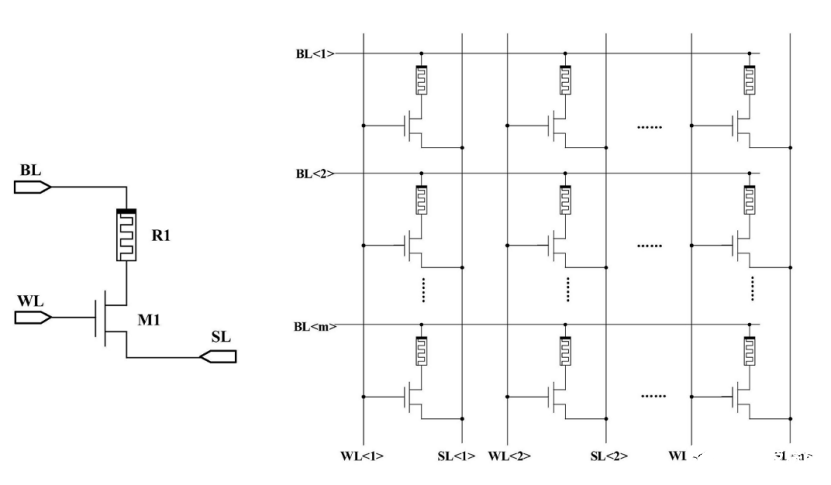

圖1 憶阻器單元及陣列示意圖

圖一展示了憶阻器單元及陣列,是此專利所用的核心硬件結構。憶阻器是一種可以通過施加外部激勵,調節其電導狀態的非易失型器件。由憶阻器構成的陣列可以并行的完成乘累加計算,并同時進行計算和存儲,因此基于這種特性可以對大量數據實現存算一體計算。由于乘累加是運行神經網絡需要的核心計算任務。將憶阻器的的電導表示為權重值,可以實現高能效的神經網絡運算,圖1右側展示的憶阻器陣列即為一個m行n列的神經網絡權重矩陣。

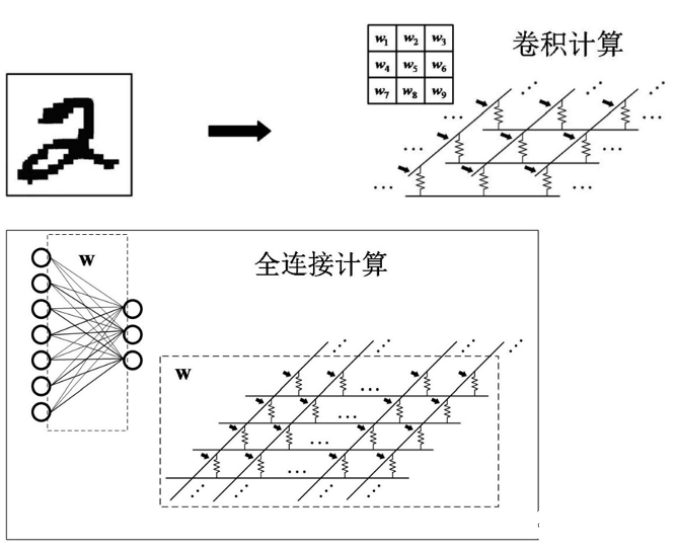

圖2 基于憶阻器陣列的卷積神經網絡卷積計算與全連接計算示意圖

卷積神經網絡包括卷積層、下采樣層、池化層和全連接層,每一層都需要做模塊化的功能處理。在卷積層中,通過卷積核替代標量的權重,加上偏置量,并在每一層添加非線性激活函數,通過多個卷積層來解決較為復雜的問題。圖2展示了基于憶阻器陣列的卷積計算和全連接計算示意圖,用一個憶阻器陣列來實現一個卷積層的卷積計算,如對輸入圖像 “ 2”進行卷積處理,同時該卷積層包括多個卷積核,每個卷積核對應憶阻器陣列的一行,且每行的多個憶阻器分別用于表示一個卷積核的各個元素的值。而對于全連接型的計算,該憶阻器陣列的每一列用于接收全連接層的輸入,各行用于提供全連接層的輸出,每一行的多個憶阻器分別用于表示該行的輸出對應的各個權重。

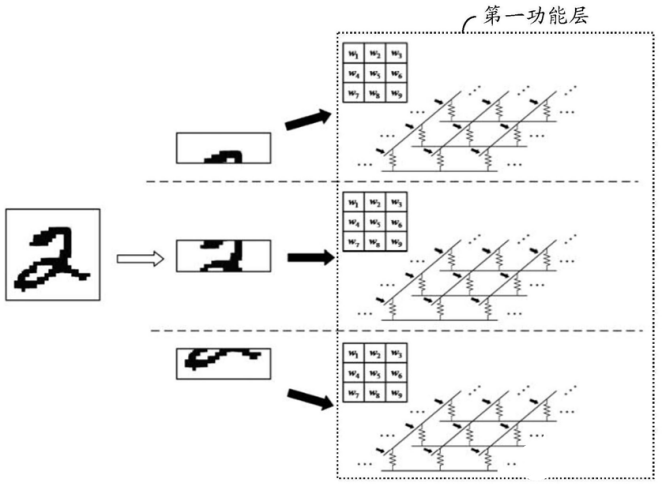

圖3 基于憶阻器的神經網絡并行加速示意圖

基于憶阻器的神經網絡并行加速示意圖如圖3所示,主要將多個第一憶阻器陣列并行地執行卷積層的操作,并將結果輸出至第二功能層。通常卷積層需要多個子輸入數據,可以按照任意順序分別提供給多個第一憶阻器陣列,由于各子輸入數據由憶阻器陣列進行卷積處理需要耗用的時間基本相同,因此加快卷積層的處理速度,即加快神經網絡的處理速度,利用并行處理方式可以大大縮短處理時間。

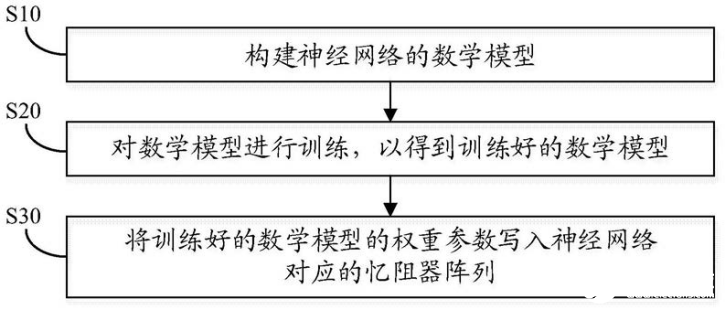

圖4 神經網絡片外訓練方法

圖4展示了基于憶阻器陣列的神經網絡片外訓練方法,首先利用數學軟件構建神經網絡的數學模型,進而基于處理器和存儲器等運行及訓練上述數學模型,最后將訓練好的數學模型的權重參數寫入神經網絡對應的憶阻器陣列,此時則可執行并行加速的計算過程,并同時對數據進行存儲,實現存算一體加速。

隨著計算存儲一體化的發展趨勢,基于憶阻器在硬件架構方面的革新,將數據存儲單元和計算單元融合為一體,能顯著減少數據搬運,極大提高計算并行度和能效。清華大學的錢鶴、吳華強教授團隊搭建的這一基于多個憶阻器陣列的全硬件完整存算一體系統,并能夠高效的運行卷積神經網絡算法,并驗證了圖像識別功能,證明了存算一體架構全硬件實現的可行性,對今后AI算力瓶頸的突破有著極大意義。

-

神經網絡

+關注

關注

42文章

4839瀏覽量

108038 -

憶阻器

+關注

關注

8文章

76瀏覽量

20866 -

存算一體

+關注

關注

1文章

121瀏覽量

5183

發布評論請先 登錄

華為AI WAN解決方案使能算網一體化新服務

在TR組件優化與存算一體架構中構建技術話語權

一體化超聲波清洗機是否真的比傳統清洗方法更高效?

緩解高性能存算一體芯片IR-drop問題的軟硬件協同設計

清華大學TOP EE+項目參訪美光上海

國際首創新突破!中國團隊以存算一體排序架構攻克智能硬件加速難題

從清華大學到鎵未來科技,張大江先生在半導體功率器件十八年的堅守!

清華大學攜手華為打造業內首個園區網絡智能體

蘋芯科技 N300 存算一體 NPU,開啟端側 AI 新征程

清華大學的存算一體化架構和并行加速方法專利

清華大學的存算一體化架構和并行加速方法專利

評論