2018年10月16日,FPGA大廠賽靈思(Xilinx)在北京的“Xilinx開發者大會 ”(XDF)上,發布了全球首款自適應計算加速平臺(ACAP)芯片系列Versal,并發布了AI Core系列和Prime系列。去年,這兩個系列產品也已經成功推向了市場。

今天(3月11日),賽靈思舉行線上發布會,正式推出了Versal ACAP產品組合的第三大產品系列—— Versal Premium。

賽靈思認為,隨著來自多元化應用和工作負載(比如智能設備、視頻流、物聯網、企業等)的數據爆炸性增長,這也使得核心網正面臨巨大的壓力。

數據顯示,2019年區域流量容量提升了100倍,帶寬年復合增長率達到了51%。

隨著數據的爆炸性增長,對于整個網絡基礎設施提出了更高的要求,這也加速驅動了網絡轉型。而在這個轉型過程當中,我們可以看到三個趨勢:

1、下一代核心網絡加速擴展。

根據ABI Research數據顯示,2020年-2024年5G核心網年復合增長率預計為313%。

2、安全已成為網絡運營商最高優先級的問題。

ISH Markit的研究顯示,對于網絡運營商來說,過去性能、擴展性、成本一直是運營商主要關注的問題,而現在,安全性已經成為了網絡運營商最為關注的問題。

3、隨著數據的增長,對于計算能力與帶寬的需求越來越高。

我們可以看到,現在網絡的帶寬的增長非常的迅速,但是,隨著摩爾定律的放緩甚至是趨于消亡,芯片的計算能力越來越跟不上了。根據賽靈思的估算,2018年之時,服務器端口速度的增長已經超過了摩爾定律對于服務器CPU性能所帶來的增長,并且差距正在進一步擴大。

在此背景之下,為了加速運營商的網絡轉型,賽靈思推出了Versal Premium ACAP系列產品,其具備了高度集成且功耗優化的網絡硬核,是業界帶寬最高、計算密度最高的自適應平臺。專為在散熱條件和空間受限的環境下運行最高帶寬網絡,以及需要可擴展、靈活應變應用加速的云提供商而設計。

Versal Premium ACAP系列詳解

我們都知道,2018年賽靈思推出的Versal系列是業界首款自適應計算加速平臺( ACAP ),是一個功能遠超常規芯片架構的革命性全新異構計算器件類別。而據賽靈思介紹,其去年就已經向客戶交付的Versal AI Core系列和Versal Prime系列,已經獲得了幾百家客戶的采用,反響很好,目前正在加速生產。

而此次賽靈思推出的全新Versal Premium則是Versal Prime系列的升級款版,是針對網絡基礎設施推出的旗艦級產品,采用臺積電7nm工藝制程打造而成,融軟件可編程能力與動態可配置硬件加速、預制連接和安全功能為一體,為加快產品上市進程提供了強大引擎。

作為 Versal ACAP 的最新產品系列, Versal Premium 系列可提供比當前FPGA高達三倍的吞吐量,且擁有高度集成的軟件/硬件平臺,內置了以太網接口、Interlaken和加密引擎,以打造快速、安全的網絡。該系列還提供了當前部署主流 FPGA 兩倍的計算密度,同時還面向持續擴展的多元化且不斷演進的云工作負載及網絡工作負載,提供了靈活應變的能力。

Versal Prime系列

具體來說,與之前的Versal Prime系列相比,Versal Premium系列在其原有的靈活多變的平臺(集成了Arm應用處理器內核和實時處理器內核、自適應硬件、DSP引擎、高速片上可編程網絡等等)上,突破性地集成了功耗優化的網絡硬核(ASIC),包括:400G高速加密引擎、600G Interlaken硬核、600G以太網硬核、112G PAM4收發器、帶有DMA的PCIe 5.0、CCIX。

Versal Premium系列

據賽靈思介紹,Versal Premium系列所提供的網絡IP集成,提供了等效22個16nm FPGA的邏輯密度,極大縮減了開發者在設計基礎架構與連接上的投入,可以使得開發者將更多的精力專注于差異化。

同時,這也使得Versal Premium系列能夠超越摩爾定律的局限,實現新一代的帶寬與處理能力,并且能夠顯著降低資本支出與運營成本。

前面提到,Versal Premium系列所集成的一系列功耗優化的網絡硬核,提供了等效22個16nm FPGA的邏輯密度,這也意味著Versal Premium系列可以釋放更多的邏輯用于個性化定制。

根據賽靈思公布的資料顯示,其Virtex UltraScale+ VU9P內部的20萬個LUT被用于了控制器、存儲器、PCIe接口等基礎設施(包括4個存儲器、4個控制器和一個PCIe+DMA),而相比之下,Versal Premium系列直接將這些作成了網絡硬核,使得其基礎設施對于內部的LUT的消耗為0。可以幫助客戶降低異構成本,更好的專注于差異化。

另外,在易用性方面,賽靈思面向各種類型的開發人員提供了豐富的軟硬件集成平臺,可以讓他們使用自己熟悉的框架和工具來進行開發。

對于數據科學家來說,可以通過TensorFlow、Caffe、PyTorch等同用框架來利用Versal Premium系列;軟件開發者也可通過賽靈思去年推出的Vitis統一開發平臺來使用Versal Premium系列;而硬件開發者則可以通過VIVADO平臺來使用Versal Premium系列。

賽靈思表示,下一代基礎設施需要更大的帶寬密度,且方案受限于現有的外形尺寸、功耗和材料,另外,數據中心的占地面積也是有限的。這就要求,下一代的基礎設施需要功耗優化的高吞吐量與計算量。

Versal Premium系列所集成的112G PAM4收發器、400G高速加密引擎、600G Interlaken硬核、600G以太網硬核、帶有DMA的PCIe Gen5&CCIX等硬核IP,不僅能夠提供功能優化的高帶寬密度,提供自適應硬件的靈活應變性,還可適合AI和ML,可以幫助客戶系統適應不斷變化的算法和安全威脅。

隨著 5G 網絡投入運營,網絡流量大幅增長,導致現有空間和功耗范圍內功耗優化吞吐量與計算密度的需求不斷提高。為支持業界應對這一挑戰,Versal Premium 系列提供了高達 9Tb/s 的可擴展、自適應串行帶寬。具體方法是將 112G PAM4 收發器與集成的網絡功能模塊用于核心網、城域網和數據中心互聯( DCI )基礎設施,將每端口帶寬密度提高兩倍,并降低時延高達 50%。

另外,在當前400G網絡的發展與部署上,58Gb/s的PAM4收發器就足以應對,而Versal Premium系列所集成的112Gb/s PAM4收發器則可在向下兼容的基礎上,同時可面向未來的單通道100G光通信和800G網絡基礎設施的發展需求。并且可兼容更具挑戰性的銅纜線和基板。

Versal Premium系列的通道化以太網硬核能夠以最小占板空間提供高達5Tb/s的可擴展以太網吞吐量,可適用于下一代核心網400G和800G基礎設施,支持多速率、多標準;支持1.8Tb/s現有的Interlaken協議下的芯片間的互聯通信;支持1.6TB/s加密線路速率吞吐量(擁有硬化的400G加密引擎),并支持 AES-GCM-256/128、MACsec 和 IPsec 。

Versal Premium系列是全球邏輯密度最高的7nm可編程邏輯平臺,支持硬件差異化、標準演進以及AI/ML。為開發者提供了很大的差異化設計且與未來兼容:如帶內網絡遙測、vRAN,且適應各種標準與協議;擁有網絡異常檢測AI:支持入侵檢測、惡意軟件識別,應對新興威脅的自適應AI算法,賽靈思隨機森林算法IP;配置與網絡性能AI:自動檢測與性能瓶頸糾正,自動配置,最大限度延長正常運行時間。

根據賽靈思提供的數據顯示,Versal Premium系列擁有業界領先的多太比特吞吐量,相比賽靈思Virtex UltraScale+(VU13P)提升了5倍以上。

在能效方面,Versal Premium系列可以低于100瓦的功耗提供單芯片800G DCI(數據中心互聯)吞吐量,與前代的Virtex UltraScale+相比,功耗降低了60%。在數據中心的應用當中,Versal Premium與前代的FPGA相比,可以提供2倍的帶寬密度,這也意味著,在帶寬相同的情況下,Versal Premium的機柜空間占用只有前代FPGA的一半。

與此同時,Versal Premium系列還支持以嵌入式方式將預制連接與硬核集成到現有云基礎設施中。從基因組學、數據分析和視頻轉碼,到針對語音和圖像識別的 AI 推斷,Versal Premium 提供了高度集成的云就緒平臺,為多元化的工作負載提供突破性能。

具體到AI性能方面,Versal Premium系列在NeatNet50(224 x 224)圖像分類模型下的性能是英偉達Tesla V100的1.6倍,是英偉達Tesla T4的2.3倍;在Yolov2(608×608)對象檢測模型下,性能分別是英偉達V100和T4的4.6倍和7.7倍;在異常檢測AI方面(隨機森林算法),性能是英特爾Xeon的65倍。

另外,存儲器也是計算加速的一個重要瓶頸。Versal Premium系列不僅擁有1Gb的緊密耦合的存儲器,可以改善性能,降低功耗和延時,同時內部還集成了LUTRAM、塊RAM、UltraRAM,以及高速片上網絡、硬化的內存控制器,可以提供高達123TB/s的片上存儲器帶寬,分別是英偉達Tesla V100和T4 GPU的9倍和25倍。而將超過123TB/s 的片上存儲器帶寬與可定制存儲器層級相結合,能夠減少數據移動從而消除相應的關鍵瓶頸。

賽靈思表示,Versal Premium ACAP解鎖了GPU無法企及的性能。

產品與供貨

賽靈思Versal Premium系列提供了7款產品,系統邏輯單元從最小160萬個到最高740萬個;自適應引擎LUT數量從最低72萬個到最高340萬個。

據介紹,Versal Premium 系列將于 2021 年上半年開始為早期用戶提供樣品。目前已提供文檔,客戶可立即使用 Versal Prime 評估套件開始原型設計。Versal Prime 器件與 Versal Premium 器件擁有眾多相同的架構模塊,支持引腳遷移至 Versal Premium。

責任編輯:wv

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636322 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435

發布評論請先 登錄

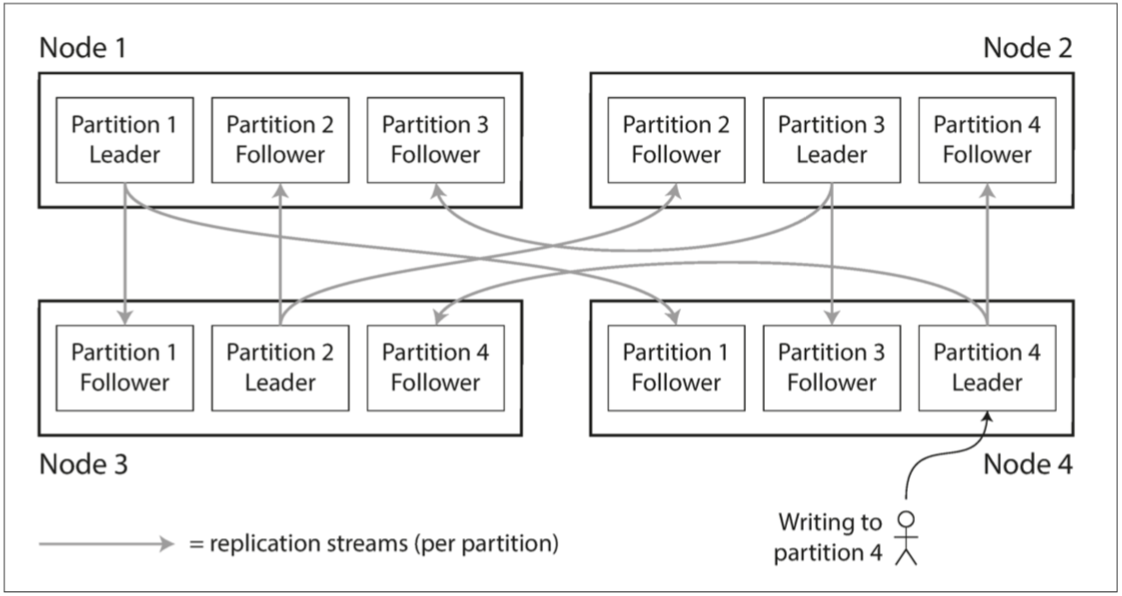

用“分區”來面對超大數據集和超大吞吐量

NVIDIA 推出 Nemotron 3 系列開放模型

5W超低功耗 + 14.4GB/s吞吐量!慧榮推出新一代PCIe 5.0 SSD主控SM8388

5W超低功耗 + 14.4GB/s吞吐量!慧榮推出新一代PCIe 5.0 SSD主控SM8388

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

使用羅德與施瓦茨CMX500的吞吐量應用層測試方案

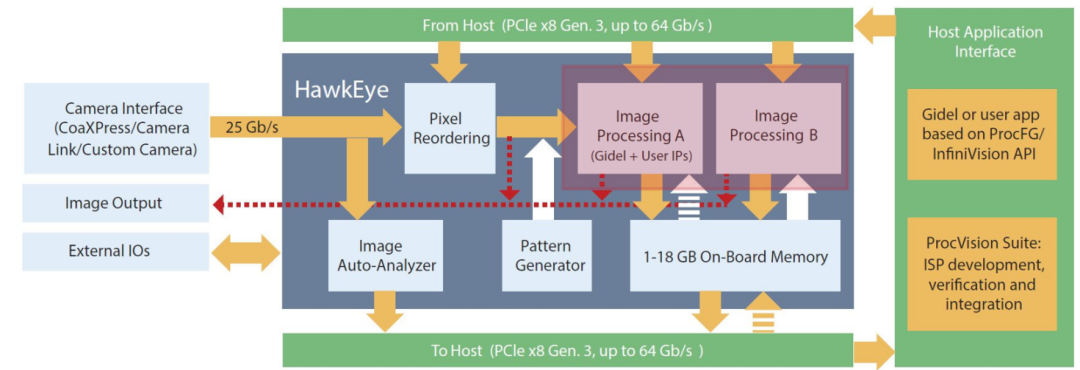

友思特方案 | FPGA 加持,友思特圖像采集卡高速預處理助力視覺系統運行提速增效

CY7C65211 作為 SPI 從機模式工作時每秒的最大吞吐量是多少?

如何在Visual Studio 2022中運行FX3吞吐量基準測試工具?

FX3進行讀或寫操作時CS信號拉低,在讀或寫完成后CS置高,對吞吐量有沒有影響?

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

賽靈思正式推出Versal Premium 可提供比當前FPGA高達三倍的吞吐量

賽靈思正式推出Versal Premium 可提供比當前FPGA高達三倍的吞吐量

評論