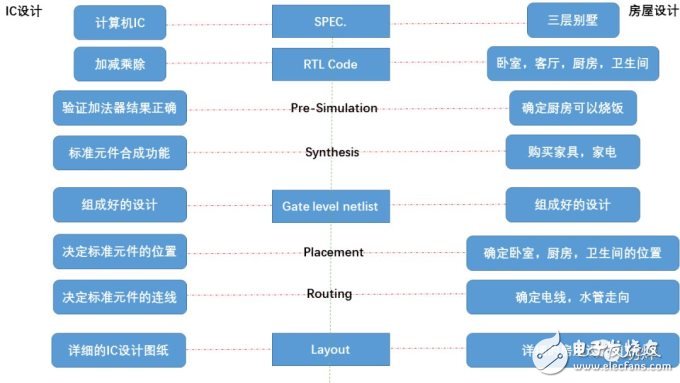

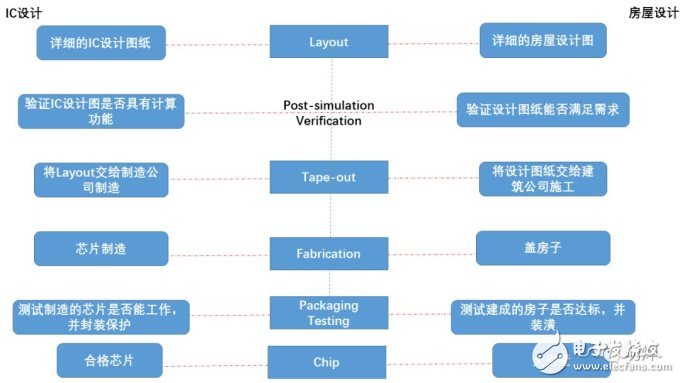

集成電路設(shè)計(jì)和房屋設(shè)計(jì)原理上是相似的。假設(shè)你要設(shè)計(jì)房屋,假設(shè)你要設(shè)計(jì)IC((integrated circuit)芯片,第一步要做什么?,第一步要想,你要做什么?這就是所謂的SPEC.,SPEC.告訴你要做一個(gè)計(jì)算機(jī)IC芯片,對(duì)應(yīng)設(shè)計(jì)房屋,例如你要設(shè)計(jì)一座大別墅。

SPEC.告訴你要設(shè)計(jì)什么芯片,接下來(lái)就是RTL(Register-Transfer-Level) Code,你要設(shè)計(jì)的計(jì)算機(jī)芯片主要有什么功能呢?比如最起碼能實(shí)現(xiàn)四則運(yùn)算,加減乘除,RTL Code要設(shè)計(jì)加法器,減法器,乘法器,除法器等;對(duì)應(yīng)你的別墅設(shè)計(jì)要三層樓,五個(gè)臥室,三間廁所,兩個(gè)客廳,一個(gè)廚房等等。

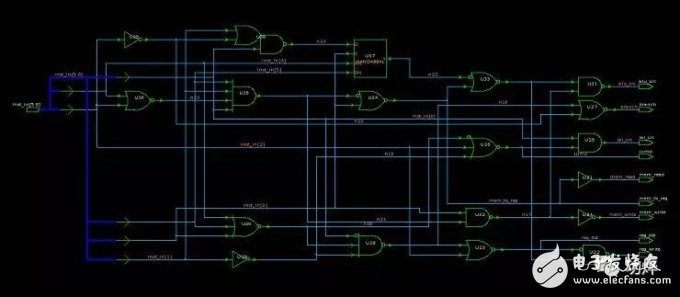

RTL Code完成后需要做Pre-Simulation,也就是模擬,你寫(xiě)的加法器,是否能正確運(yùn)算,1+1=2,不能算出來(lái)等于3吧,減法器也是如此,你寫(xiě)的每個(gè)元件都要進(jìn)行Pre-Simulation,確定能實(shí)現(xiàn)相對(duì)的功能;Pre-Simulation在別墅設(shè)計(jì)中對(duì)應(yīng)的是,你設(shè)計(jì)的廚房要可以燒飯,廁所是不能燒飯的吧,臥室可以睡覺(jué),客廳可以接待客人等等。模擬完以后進(jìn)行Synthesis合成,所謂的合成,在IC設(shè)計(jì)過(guò)程中,標(biāo)準(zhǔn)庫(kù)里有一些元件可以直接拿來(lái)用,用來(lái)實(shí)現(xiàn)你想要的功能;Synthesis在別墅設(shè)計(jì)中對(duì)應(yīng)的就是去商店買家具,比如客廳需要沙發(fā),臥室需要床,廁所需要馬桶,你不用自己設(shè)計(jì)制作,可以直接去宜家購(gòu)買。Synthesis的目標(biāo)是用最少的標(biāo)準(zhǔn)元件實(shí)現(xiàn)功能,你的芯片性能就越好,這就好像在別墅設(shè)計(jì)中,有的設(shè)計(jì)師能力不行,廁所設(shè)計(jì)了三個(gè)馬桶,這就不合理,資源浪費(fèi),別墅設(shè)計(jì)的目標(biāo)就是用最少的家具材料實(shí)現(xiàn)最完善的功能。

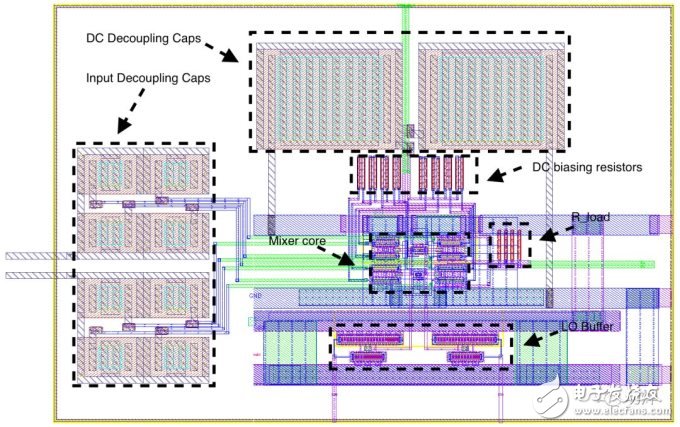

合成完以后就可以把RTL Code轉(zhuǎn)換成Gate level Netlist,這時(shí)候還是抽象的標(biāo)準(zhǔn)元件,具體擺放位置,如何連線還不知道;對(duì)應(yīng)別墅設(shè)計(jì)中,你只知道需要多少?gòu)埓玻嗌亳R桶,電視,柜子數(shù)量等等,但是具體擺放位置還不知道。接下來(lái)就是Placement,確定標(biāo)準(zhǔn)元件在芯片上的具體位置;對(duì)應(yīng)別墅設(shè)計(jì)中客廳在幾樓,廁所在幾樓,臥室在哪里。標(biāo)準(zhǔn)元件擺放位置影響芯片性能,例如你把廁所放在別墅四樓,那你每次都要爬到四樓上廁所,這顯然不好,廁所位置放在每層樓靠近窗戶位置肯定最合理,如果放在中間位置,那肯定臭死了,Placement同理,每個(gè)標(biāo)準(zhǔn)元件擺放位置一定要合理。Placement結(jié)束后是Routing的步驟,決定標(biāo)準(zhǔn)元件在芯片中的連線,對(duì)應(yīng)別墅中,水管如何鋪設(shè),電線如何走向等等。

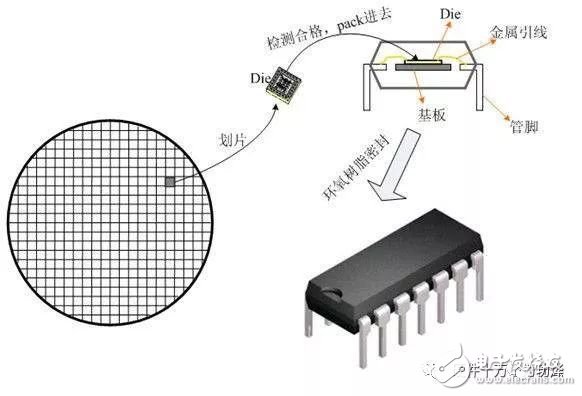

接下來(lái)就是Layout,是一份具體的,詳細(xì)的IC設(shè)計(jì)圖紙,所有元件的位置,以及布局走線的方向等等;對(duì)應(yīng)別墅的詳細(xì)設(shè)計(jì)圖紙。有了詳細(xì)設(shè)計(jì)圖紙,然后就是Post-Simulation&Verification,其作用就是驗(yàn)證這張IC設(shè)計(jì)圖紙真的能實(shí)現(xiàn)計(jì)算機(jī)的功能,可能乘法運(yùn)算有問(wèn)題,這就需要修改;對(duì)應(yīng)別墅設(shè)計(jì)中,你需要確定每個(gè)房間,每個(gè)設(shè)計(jì)是否滿足你的要求,比如你需要臥室要有陽(yáng)臺(tái)等等。驗(yàn)證沒(méi)有問(wèn)題接下來(lái)就是Tape-out,將Layout給IC制造公司,請(qǐng)他們幫忙制造,別墅設(shè)計(jì)中接下來(lái)就是將設(shè)計(jì)圖紙交給建筑商,請(qǐng)他們幫忙施工。Fabrication就是芯片制造;對(duì)應(yīng)就是打地基,砌磚,蓋房子。

制造完以后是Packaging & Testing,先測(cè)試制造的芯片有沒(méi)有問(wèn)題,然后在封裝保護(hù)芯片;房子蓋好以后,需要進(jìn)行測(cè)試,比如抗震測(cè)試,漏電測(cè)試,水管是否連通等等。

最后就是成品Chip,對(duì)應(yīng)就是房子蓋好咯。

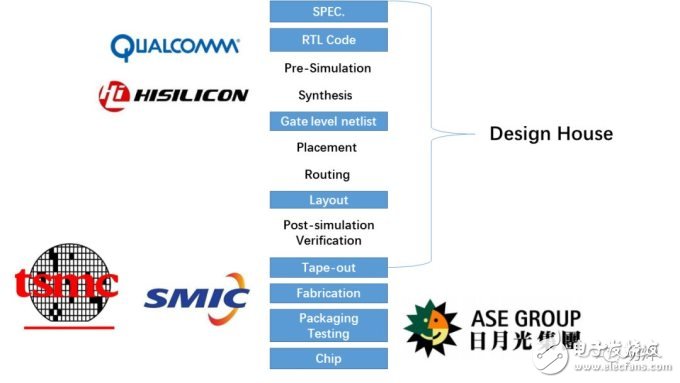

以上簡(jiǎn)單介紹IC芯片從設(shè)計(jì)到制造完成的過(guò)程,實(shí)際過(guò)程遠(yuǎn)比這復(fù)雜,每個(gè)步驟都有相應(yīng)的公司,目前還沒(méi)有一家可以從頭到尾完成。接下來(lái)給大家講一下各個(gè)流程每家公司扮演的角色。

在Tape-out之前,都是在設(shè)計(jì)階段,IC設(shè)計(jì)公司被稱為Design House,著名的公司有高通,海思,聯(lián)發(fā)科,展訊等等,為什么有這么多design house呢?很好理解,就像房屋設(shè)計(jì),有的設(shè)計(jì)公司擅長(zhǎng)居民樓設(shè)計(jì),有的擅長(zhǎng)商場(chǎng)設(shè)計(jì),有的擅長(zhǎng)工廠廠房設(shè)計(jì)等等。Design House里面還有一類公司叫EDA company,它是提供所有IC 設(shè)計(jì)過(guò)程中 的軟件 ,有Cadence,Synopsys,SIEMENS等,就像在你設(shè)計(jì)蓋房子的時(shí)候,不可能拿出紙筆進(jìn)行手繪吧,現(xiàn)在都是用AUTO-CAD,用軟件輔助設(shè)計(jì),EDA軟件可以理解為AUTO-CAD軟件。

Tape-out之后就是fabrication,芯片制造公司就是所謂 的Foundry,制造工廠稱為Fab,著名的公司有TSMC,GF(不是女票,是global foundry),SMIC,HHgrace等等。

制造完之后是封裝測(cè)試,Assembly & Test,著名的公司有日月光 ASE(沒(méi)錯(cuò),就是那個(gè)徐匯日月光商場(chǎng),其實(shí)它的主營(yíng)業(yè)務(wù)是半導(dǎo)體封測(cè)),矽品SPLI(學(xué)中文的妹子知道,矽是硅元素的舊稱,***地區(qū)把硅元素稱為矽)。

半導(dǎo)體集成電路產(chǎn)業(yè)極其復(fù)雜,分工合作非常重要,國(guó)內(nèi)半導(dǎo)體公司,海思是設(shè)計(jì)龍頭,中芯國(guó)際是制造龍頭 ,長(zhǎng)電是封測(cè)龍頭,各公司與國(guó)際公司還有差距,仍需繼續(xù)努力。

-

集成電路

+關(guān)注

關(guān)注

5452文章

12571瀏覽量

374520 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30725瀏覽量

264040 -

SPEC

+關(guān)注

關(guān)注

0文章

34瀏覽量

16479

發(fā)布評(píng)論請(qǐng)先 登錄

廣州規(guī)劃:聚焦半導(dǎo)體,2035鑄集成電路重鎮(zhèn)#廣州#半導(dǎo)體#集成電路

集成電路制造中薄膜刻蝕的概念和工藝流程

PDK在集成電路領(lǐng)域的定義、組成和作用

一文看懂芯片的設(shè)計(jì)流程

新思科技攜手深圳大學(xué)助力數(shù)字集成電路人才培養(yǎng)

CMOS超大規(guī)模集成電路制造工藝流程的基礎(chǔ)知識(shí)

電機(jī)驅(qū)動(dòng)與控制專用集成電路及應(yīng)用

電機(jī)控制專用集成電路PDF版

中國(guó)集成電路大全 接口集成電路

集成電路和光子集成技術(shù)的發(fā)展歷程

集成電路產(chǎn)業(yè)新地標(biāo) 集成電路設(shè)計(jì)園二期推動(dòng)產(chǎn)業(yè)創(chuàng)新能級(jí)提升

科研分享|智能芯片與異構(gòu)集成電路電磁兼容問(wèn)題

一文看懂集成電路的設(shè)計(jì)流程

一文看懂集成電路的設(shè)計(jì)流程

評(píng)論