半導(dǎo)體制造業(yè)的進步是主要原因因為FPGA越來越受歡迎。只要工程師只使用PLD或FPGA來實現(xiàn)相對簡單的膠合邏輯電路,使用提供更大靈活性和更低成本成本的ASIC器件就是在IC上實現(xiàn)特定功能的唯一解決方案。 FPGA供應(yīng)商現(xiàn)在正在制造130納米和90納米半間距尺寸的器件。這些器件不僅使設(shè)計人員能夠?qū)崿F(xiàn)需要超過一百萬個邏輯門的電路,而且還提供豐富的IP(知識產(chǎn)權(quán))內(nèi)核庫存,從而減少開發(fā)時間和成本。同時,采用相同的130和90納米技術(shù)制造的ASIC器件的NRE(非重復(fù)工程)成本也大幅上升。需要一套新掩碼的錯誤很容易花費25萬到100萬美元,具體取決于錯誤的嚴重程度。

因此,管理人員經(jīng)常選擇使用FPGA設(shè)備,無論是產(chǎn)品的整個生命周期,如果應(yīng)用程序只需要幾萬個設(shè)備,或者用于原型設(shè)計和數(shù)量增加。一旦批量生產(chǎn)表明設(shè)計穩(wěn)定,工程師就可以將設(shè)計移植到ASIC設(shè)備上。移植通常很容易,因為在大多數(shù)應(yīng)用中,工程師不會利用器件的現(xiàn)場可編程性,這是將這些器件與PLD區(qū)分開來的主要特征。 FPGA器件很有吸引力,因為修改實現(xiàn)的成本實際上等于工程開發(fā)成本。因此,它們允許工程師使用有吸引力的調(diào)試方法,尤其是在嵌入式系統(tǒng)中,其中硬件和軟件的集成需要盡可能早的開發(fā)周期中的硬件原型。 FPGA架構(gòu)中缺少標準微處理器內(nèi)核嚴重阻礙了工程師將這些器件用于嵌入式軟件應(yīng)用。但是,從130納米工藝節(jié)點開始,Altera和Xilinx都提供了微處理器內(nèi)核,而ARM也在為FPGA量身定制的庫中提供了許多標準微處理器內(nèi)核。設(shè)計人員還需要一個協(xié)處理器和外設(shè)IP核庫,以使用FPGA器件實現(xiàn)真正的SOC(片上系統(tǒng))產(chǎn)品(參見附文“嵌入式軟件和FPGA:黃金時段的合作伙伴關(guān)系”)。

來自FPGA供應(yīng)商的今天產(chǎn)品的密度和速度使IP供應(yīng)商確信將其產(chǎn)品移植到FPGA。 DSP核心和圖形顯示核心正在變得可用。當(dāng)然,內(nèi)核和專有邏輯塊必須在設(shè)備內(nèi)相互通信,而工程師直到最近才使用總線實現(xiàn)此任務(wù)。所有三種流行的微處理器內(nèi)核 - 來自Altera的Nios和ARM922T(通過與ARM的許可協(xié)議)和來自Xilinx的PowerPC(通過與IBM的許可協(xié)議) - 使用標準總線。但是,在核心之間傳輸數(shù)據(jù)和控制信息所需的速度激發(fā)了Nallatech為FPGA開發(fā)更快的通信方法。

系統(tǒng)通信可能消耗多達80%的應(yīng)用程序根據(jù)Nallatech的系統(tǒng)應(yīng)用工程師Craig Sanderson的說法,開發(fā)時間。用于FPGA計算應(yīng)用的Dimetalk通信開發(fā)工具使開發(fā)人員能夠部署基于分組的網(wǎng)絡(luò),該網(wǎng)絡(luò)可以跨越使用多個FPGA的系統(tǒng)。設(shè)計人員可以在網(wǎng)絡(luò)中的任何位置部署接口節(jié)點,也可以插入塊以與外部接口進行通信。

廣泛使用FPGA進行系統(tǒng)設(shè)計的最大障礙是他們的單位成本。即使是大批量生產(chǎn),一個FPGA器件的成本也高于ASIC或結(jié)構(gòu)化ASIC技術(shù)中實現(xiàn)的相同設(shè)計的成本。但越來越多的是,制造過程中零件的單位成本在整體產(chǎn)品成本方程中失去意義,因為與每種新的可用工藝技術(shù)相關(guān)的開發(fā)成本和與失去的市場機會相關(guān)的成本至少升級了一個數(shù)量級。與此同時,ASIC和FPGA之間器件單位成本的差異正在變小。

供應(yīng)商提供的工具

自6月以來,Actel, Altera,Lattice和Xilinx都推出了新版本的軟件。所有FPGA供應(yīng)商都在其產(chǎn)品中捆綁第三方軟件。 EDA供應(yīng)商為FPGA供應(yīng)商提供定制版本的產(chǎn)品,這些產(chǎn)品通常不提供原始工具的所有功能和功能,因為FPGA供應(yīng)商以更低的價格提供他們的工具。

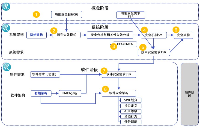

Actel的理念是將資源集中在布局和布線的后端流程上,這需要對架構(gòu)有深入,清晰的理解。 Actel是1994年引入FPGA靜態(tài)時序分析的領(lǐng)導(dǎo)者,幫助設(shè)計人員在將設(shè)計提交到芯片之前實現(xiàn)時序收斂。該公司與傳統(tǒng)的EDA供應(yīng)商合作,提供前端工具,如Mentor Graphics的ModelSim邏輯模擬器,Synplicity的邏輯綜合Synplify和用于物理綜合的Magma's Palace。它集成了Libero IDE(集成設(shè)計環(huán)境)中的工具,根據(jù)客戶需求提供三種配置,售價為595美元至2595美元。 FPGA開發(fā)的設(shè)計流程變得復(fù)雜(圖1)。對于喜歡使用自己的EDA工具的設(shè)計師,Actel的Designer包括布局布線工具以及靜態(tài)時序分析產(chǎn)品。

Altera通過CD和基于Web的產(chǎn)品為其客戶提供Quartus II軟件。 Web產(chǎn)品為用戶提供150天后過期的許可證,并且不支持所有Altera設(shè)備。 Altera自成立以來投入了大量資金開發(fā)和支持自己的設(shè)計工具。它內(nèi)部開發(fā)了FPGA開發(fā)流程中的幾乎所有工具,包括邏輯和物理綜合工具。它認為,當(dāng)FPGA供應(yīng)商為新產(chǎn)品開發(fā)架構(gòu)和綜合工具時,與沒有合成技術(shù)知識相比,它可以更好地了解優(yōu)化器件結(jié)構(gòu)的最佳方法。邏輯仿真是Altera專門使用第三方產(chǎn)品的唯一領(lǐng)域。 Quartus II提供了Altera版本的Mentor Graphics的ModelSim,但也支持Cadence的Incisive仿真平臺。您還可以使用Synplicity和Synopsys中的工具以及Quartus II中提供的工具。最新版本的Quartus II引入了時序和資源優(yōu)化功能,以指導(dǎo)用戶在設(shè)計周期中使用。在使用嵌入式邏輯分析儀查看器SignalTap II進行調(diào)試時,工程師也會獲得幫助。 Quartus II軟件可以獲得2000美元的年度訂購許可。

萊迪思半導(dǎo)體發(fā)布了ispLever設(shè)計工具套件4.1版。它包括將可編程邏輯設(shè)計從概念到實現(xiàn)的所有工具。它包括用于設(shè)計輸入,項目管理,設(shè)計擬合,布局布線,布局規(guī)劃,器件編程和片上邏輯分析的工具。工程師可以選擇Synplicity或Mentor的合成產(chǎn)品,也可以獲得針對基于萊迪思的設(shè)計定制的ModelSim版本。萊迪思還提供自己的功能模擬器。 ispLever的定價從995美元開始。

Xilinx是另一家在EDA工具開發(fā)方面投入了大量資金的FPGA供應(yīng)商;設(shè)計人員可以從ISE設(shè)計工具的五種配置中進行選擇。該公司最近使用6.3i版更新了其ISE開發(fā)環(huán)境,該版本支持FPGA用戶完整的前端到后端流程。在前端,ISE包括Pace和ISE Floorplanner布局規(guī)劃工具。 Xilinx還收購了Hier Design,現(xiàn)在提供RTL平面圖Plan Ahead作為ISE客戶的獨立可購買選項。工程師可以使用ModelSim或Synopsys Verilog模擬器和ISE。 Project Navigator是ISE的主要任務(wù)管理器,它允許用戶配置和驅(qū)動設(shè)計實現(xiàn)。 ISE提供了Xilinx內(nèi)部開發(fā)的綜合工具,但Synplicity,Mentor和Synopsys也提供了工程師可以與ISE結(jié)合使用的綜合工具。 ISE的五種配置價格從免費的Web可下載軟件包到ISE Foundation,價格為2495美元。

第三方工具

多年來,可編程設(shè)備非常簡單,以至于EDA供應(yīng)商發(fā)現(xiàn)他們無法充分利用這些工具來證明進入市場的合理性。大多數(shù)使用FPGA和PLD設(shè)備的工程師都是印刷電路板開發(fā)人員,他們無法使用針對IC設(shè)計的EDA工具。 FPGA供應(yīng)商開發(fā)了自己的基于原理圖的工具,因為即使在今天,印制電路板設(shè)計人員也使用原理圖將設(shè)計納入開發(fā)流程。供應(yīng)商要么為批量客戶提供免費的FPGA工具,要么以低于1000美元的價格出售。隨著設(shè)備變得越來越復(fù)雜,工程師開始希望在面板上實現(xiàn)設(shè)計之前驗證設(shè)計,因為使用示波器或邏輯分析儀調(diào)試電路變得非常耗時。 Model Technology現(xiàn)已成為Mentor Graphics的一部分,很快進入市場,現(xiàn)在在FPGA驗證方面處于領(lǐng)先地位,盡管其他一些EDA供應(yīng)商也在這個市場上占有一席之地。

今天,工程師還需要強大的綜合工具來開發(fā)FPGA設(shè)計,大多數(shù)支持ASIC綜合的EDA供應(yīng)商也為FPGA提供工具。其他供應(yīng)商,如Altium和Aldec,其主要市場是印刷電路板開發(fā),也已經(jīng)認識到設(shè)計人員必須采用系統(tǒng)方法進行產(chǎn)品開發(fā)。工程師不能再將FPGA視為單獨的系統(tǒng),而不會影響電路板的其他部分。 EDA公司正在提供與后端,特定于供應(yīng)商的FPGA工具無縫集成的流程。雖然這些工具的成本通常高于FPGA供應(yīng)商的工具,但它們提供了更多功能,并允許設(shè)計人員獨立于FPGA供應(yīng)商工作。除了可以簡化FPGA器件和印刷電路板集成的產(chǎn)品外,傳統(tǒng)的EDA供應(yīng)商還將測試和綜合作為最適合第三方支持的兩個細分市場。

設(shè)計驗證數(shù)據(jù)是開發(fā)IC的最大成本,并且隨著設(shè)備的復(fù)雜性和尺寸隨著可用設(shè)備的復(fù)雜性而增長,它正在成為FPGA設(shè)計中的重要費用。隨著越來越多接受ASIC開發(fā)培訓(xùn)的工程師轉(zhuǎn)向FPGA器件,他們傾向于使用他們熟悉的硬件描述語言。曾經(jīng)幾乎不存在于FPGA市場中的Verilog正在獲得市場份額。 Bluespec和Mentor Graphics支持最新版本的Verilog SystemVerilog。 Mentor Graphics的ModelSim仍然是FPGA市場上最流行的邏輯模擬器。它支持設(shè)計人員現(xiàn)在可用的所有硬件描述語言。 Cadence的Incisive仿真平臺和Synopsys的VCS主要出現(xiàn)在將FPGA設(shè)計融入傳統(tǒng)ASIC設(shè)計的設(shè)計流程中。

工程師也開始使用支持更高級別的設(shè)計語言抽象,例如C及其面向硬件的方言,以及MathWorks的Matlab。 Mentor推出Catapult C產(chǎn)品,該產(chǎn)品允許設(shè)計人員合成在不定時C中描述的設(shè)計,而Catalytic提供的產(chǎn)品允許設(shè)計人員使用Matlab將浮點DSP算法轉(zhuǎn)換為定點算法。使用可用于FPGA器件的任何DSP內(nèi)核的工程師需要定點算法,而Catalytic使他們能夠驗證兩種實現(xiàn)在Matlab環(huán)境中是否相同。 FPGA的在線調(diào)試帶來了一些挑戰(zhàn)。例如,時鐘速度可以超過200 MHz,并且設(shè)計可以有多個電路以不同的時鐘速度運行。安捷倫科技公司推出了16900系列邏輯分析儀,用于解決諸如與被測設(shè)備的連接,動態(tài)探測以及以各種格式查看和分析系統(tǒng)行為等問題。

綜合

隨著設(shè)備復(fù)雜性的增加,設(shè)計人員需要更復(fù)雜的綜合工具。雖然您仍然可以僅使用邏輯綜合開發(fā)功能正確的FPGA,但最復(fù)雜的設(shè)計要求工程師也使用物理綜合來滿足時序要求。物理綜合與邏輯綜合不同,因為它在執(zhí)行電路優(yōu)化時需要考慮最終的芯片布局。物理綜合可以通過嘗試各種芯片布局方法來找到最符合要求的拓撲,從而處理更復(fù)雜的時序要求。除第三方工具外,Altera和Xilinx都提供自己的邏輯綜合產(chǎn)品; Actel和Lattice更愿意只提供第三方工具。

EDA供應(yīng)商Mentor和Synplicity在FPGA邏輯和物理綜合市場占據(jù)主導(dǎo)地位。直到最近,Synplicity才專注于FPGA市場;僅在最近幾年才擴大了對結(jié)構(gòu)化和傳統(tǒng)ASIC器件的興趣。它提供了Synplify,一種邏輯綜合工具; Synplify Pro,Synplify的更強大版本;和Amplify,為Synplify Pro增加了物理綜合功能。 Mentor Graphics多年來一直在FPGA開發(fā)工具市場占有一席之地,但在提供有競爭力的合成產(chǎn)品方面卻很晚。通過其精確綜合工具,該公司已經(jīng)重新獲得了Synplicity失去的一些基礎(chǔ)。

Dataquest 2003年市場趨勢報告顯示,Synplicity在FPGA綜合市場的份額為44%,而Mentor的份額為43%。 Synopsys是ASIC市場中無可爭議的邏輯和物理綜合領(lǐng)導(dǎo)者,在FPGA領(lǐng)域遙遙領(lǐng)先。只要ASIC和FPGA器件的功能差異很大,供應(yīng)商就會將不同的設(shè)計團隊分配給涉及這兩種器件的開發(fā)。雖然Synopsys之前曾兩次嘗試進入FPGA市場,但它并未成功,最終放棄了努力。但隨著FPGA供應(yīng)商開始使用130納米和90納米工藝,F(xiàn)PGA的性能證明了它們在早期生產(chǎn)運行中用于ASIC原型設(shè)計和ASIC替代品的合理性。因此,F(xiàn)PGA設(shè)計人員也常常致力于ASIC設(shè)計。 Synplicity和Mentor都擴展了他們的FPGA工具,以滿足一些ASIC市場的需求。因此,Synopsys再一次提供FPGA綜合工具是有意義的。 DC FPGA與流行且成功的設(shè)計編譯器綜合產(chǎn)品共享前端,并針對參與FPGA開發(fā)的ASIC設(shè)計人員。 Magma還與Palace進入了FPGA物理綜合市場,這是Actel提供的第三方工具套件的一部分。 Bluespec推出了一種綜合產(chǎn)品,支持SystemVerilog,這是Verilog市場上最新提出的標準。

FPGA對某些DSP功能非常有效,尤其是利用并行操作的算法。許多DSP設(shè)計人員不熟悉EDA工具。相反,他們使用The MathWorks的Matlab和Simulink開始算法開發(fā),然后將他們的設(shè)計轉(zhuǎn)換為使用DSP和一些嵌入式軟件的硬件實現(xiàn)。兩年前,Accelchip推出了一款產(chǎn)品,允許工程師使用Matlab和Simulink開發(fā)和驗證算法,然后在FPGA中實現(xiàn)電路,而無需在VHDL或Verilog中手動重新實現(xiàn)設(shè)計。最近,Synplicity推出了Synplify DSP,它還允許設(shè)計人員使用Matlab和Simulink開始DSP的算法開發(fā),然后生成可以輸入到綜合工具中的RTL代碼。 Altera客戶可以使用公司內(nèi)部開發(fā)的DSP Builder將他們的Matlab和Simulink設(shè)計鏈接到Quartus II環(huán)境。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636312

發(fā)布評論請先 登錄

技術(shù)破局,黑馬突圍!GPMI技術(shù)重構(gòu)投影行業(yè)格局

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】跟著本書來看EDA的奧秘和EDA發(fā)展

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】--EDA了解與發(fā)展概況

中科億海微牽頭構(gòu)建國產(chǎn)化FPGA/EDA生態(tài) 以協(xié)同創(chuàng)新破解“卡脖子”難題

行芯科技GloryEX入選國產(chǎn)EDA工具口碑榜

【書籍評測活動NO.69】解碼中國”芯“基石,洞見EDA突圍路《芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望》

智多晶EDA工具HqFpga軟件的主要重大進展

醫(yī)療PCB供應(yīng)鏈復(fù)雜性與風(fēng)險管控

Wisim DC電源完整性EDA物理驗證仿真工具介紹

西門子推出用于EDA設(shè)計流程的AI增強型工具集

EDA是什么,有哪些方面

MBSE工具+架構(gòu)建模:從效率提升到質(zhì)量賦能

作為硬件工程師,你用那款PCB 設(shè)計軟件?超全EDA工具整理!

多層PCB復(fù)雜設(shè)計怎么破?三款主流EDA工具深度解析

Marvell展示2納米芯片3D堆疊技術(shù),應(yīng)對設(shè)計復(fù)雜性挑戰(zhàn)!

用于FPGA的EDA工具打破了復(fù)雜性的僵局

用于FPGA的EDA工具打破了復(fù)雜性的僵局

評論