為了解決多千兆赫(multi-GHz)PCB設(shè)計中信號路徑不連續(xù)性的延遲效應(yīng),Cadence Design Systems Inc.發(fā)布了Allegro PCB SI 630,這是一種針對散射參數(shù)優(yōu)化的新工具(S-基于參數(shù))的互連特性和串行鏈路的高容量仿真。

Allegro PCB SI 630是一個集成的設(shè)計和分析環(huán)境,用于設(shè)計具有多GHz信號的復(fù)雜數(shù)字PCB系統(tǒng),支持PCI Express, XAUI,串行ATA II,Infiniband以及其他接口標(biāo)準(zhǔn),其工作速率等于或高于2.5Gbits/sec。

隨著數(shù)據(jù)傳輸速率的提高,信號路徑中的不連續(xù)性影響可能會持續(xù)很多次傳輸,并且必須是詳細(xì)研究以確保滿足時序和電壓余量。 Allegro PCB SI 630工具旨在通過高容量仿真(通道分析),對電路板上,數(shù)字電路板上以及硅封裝板和第一批商用產(chǎn)品上的數(shù)百萬次數(shù)據(jù)傳輸進(jìn)行詳細(xì)分析這可以在幾秒鐘內(nèi)模擬10,000位。

IBM表示,它與Cadence密切合作,定義和開發(fā)解決方案,允許客戶對其基于高速SERDES的設(shè)計進(jìn)行建模。

“直到現(xiàn)在,由于SERDES供應(yīng)商需要開發(fā)專有的定制工具,因此這種模擬實際上是不可能的,“IBM系統(tǒng)和技術(shù)集團(tuán)ASIC業(yè)務(wù)部門主管Richard Busch在一份聲明中表示。”這個新的千兆赫茲信號設(shè)計技術(shù)是面向系統(tǒng)設(shè)計人員,IC供應(yīng)商和整個行業(yè)的通用信號完整性分析工具邁出的一大步。“

Allegro PCB SI 630具有完全集成的S參數(shù)支持和高容量模擬意味著縮短具有多GHz信號的設(shè)計的設(shè)計周期時間。該工具還旨在允許用戶在設(shè)計周期的每個階段探索和解決與電氣性能相關(guān)的問題,并確保在虛擬原型設(shè)計環(huán)境中滿足多GHz信號的時序和電壓余量。 Cadence表示,通過先進(jìn)的仿真技術(shù),大大減少了在實驗室中進(jìn)行多項資格認(rèn)證的需求,使工程師能夠避免一次或多次PCB原型迭代。

Cadence Allegro PCB SI 630現(xiàn)已上市。

-

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424292 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44639

發(fā)布評論請先 登錄

Cadence 推出 ChipStack? AI Super Agent,開辟芯片設(shè)計與驗證新紀(jì)元

Cadence推出全新完整小芯片生態(tài)系統(tǒng)

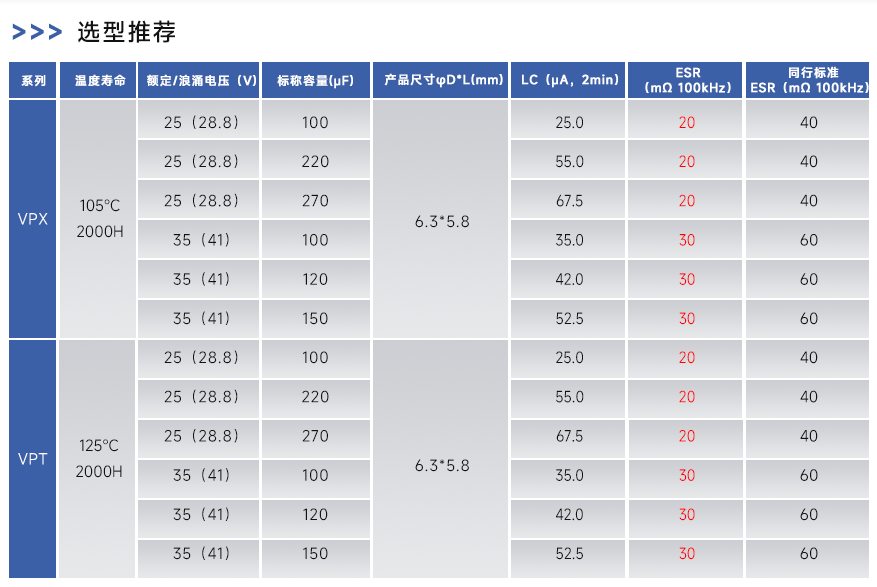

【轉(zhuǎn)】永銘高容量密度固態(tài)電容解決方案:以四大核心優(yōu)勢,破解智能數(shù)碼電源設(shè)計困境

永銘高容量密度固態(tài)電容解決方案:以四大核心優(yōu)勢,破解智能數(shù)碼電源設(shè)計困境

永銘高容量密度固態(tài)電容解決方案:以四大核心優(yōu)勢,破解智能數(shù)碼電源設(shè)計困境

松下PhotoMOS HF SSOP 1 Form A高容量產(chǎn)品深度解析

FICT如何解決PCB三大痛點

Cadence電子設(shè)計仿真工具標(biāo)準(zhǔn)搭載村田制作所的產(chǎn)品數(shù)據(jù)

2025 Cadence 中國技術(shù)巡回研討會即將開啟 ——系統(tǒng)設(shè)計與分析專場研討會(上海站)

Cadence推出高容量PCB仿真如何解決

Cadence推出高容量PCB仿真如何解決

評論