全球領先的200mm純晶圓代工廠——華虹半導體有限公司(“華虹半導體”或“公司”,連同其附屬公司,統(tǒng)稱“集團”,股份代號:1347.HK)今天宣布,公司針對8位微控制器(Microcontroller Unit, MCU)市場,最新推出95納米單絕緣柵非易失性嵌入式存儲器(95納米5V SG eNVM)工藝平臺。在保證產品穩(wěn)定性能的同時,95納米5V SG eNVM工藝平臺以其低功耗、低成本的優(yōu)勢,廣受客戶青睞。該平臺現(xiàn)已成功量產,產品性能優(yōu)異。

萬物互聯(lián)時代,8位MCU不斷推陳出新,出貨量也逐步攀升,在工業(yè)控制、物聯(lián)網、汽車電子、消費類電子等諸多領域均有廣泛應用。根據市調機構IHS預測,8位MCU市場持續(xù)增長,到2020年,全球8位MCU的市場規(guī)模將達61億美元,需求量將達到近170億顆,市場需求強勁。華虹半導體順勢推出95納米5V SG eNVM工藝平臺,為客戶提供高性價比的制造工藝,助力客戶在龐大的8位MCU應用市場提高競爭力。

華虹半導體的95納米5V SG eNVM工藝通過優(yōu)化單元的結構和IP的設計,令其具有較小的面積和較低的讀取功耗(50μA/MHz),器件靜態(tài)功耗Ioff也只有0.5pA。CPU內核的速度達到50MHz,完全滿足了8位MCU產品應用的需求。在設計上,該工藝還支持整合電可擦可編程只讀存儲器(EEPROM)和閃存(Flash)的單IP設計,把EEPROM的高性能和Flash的面積優(yōu)勢體現(xiàn)在一顆IP上,相比于兩個IP的設計,大大節(jié)約了面積成本。同時,采用具有競爭力的光罩層數(shù),三層金屬最少光罩層數(shù)只有19層。此外,在模擬面積比較大的芯片應用領域,華虹半導體的95納米單5V電壓工藝亦具有較大的成本優(yōu)勢。該平臺在保持良好性能的同時兼?zhèn)涓呖煽啃裕瑪?shù)據保存時間超過30年,重復擦寫次數(shù)超過50萬次。

華虹半導體執(zhí)行副總裁孔蔚然博士表示:“華虹半導體力爭保持在eNVM技術領域的全球競爭優(yōu)勢,近年來在智能卡、MCU市場取得很好的業(yè)績。此次推出的95納米5V SG eNVM技術,安全可靠兼顧成本優(yōu)勢,使其成為制勝8位MCU市場的首選制造工藝。”他進一步指出,“華虹半導體同時擁有多種MCU所需要的細分化eFlash/eEEPROM工藝平臺,可將我們領先的嵌入式存儲技術與CMOS射頻集成及/或高壓LDMOS技術結合,大大增加可用MCU解決方案的數(shù)量。華虹半導體將順應市場需求,持續(xù)進行技術創(chuàng)新,致力于為客戶提供更低功耗、更高性能、更安全可靠的高性價比MCU解決方案。”

-

半導體

+關注

關注

339文章

30729瀏覽量

264054 -

嵌入式

+關注

關注

5198文章

20443瀏覽量

333990 -

物聯(lián)網

+關注

關注

2945文章

47818瀏覽量

414840

發(fā)布評論請先 登錄

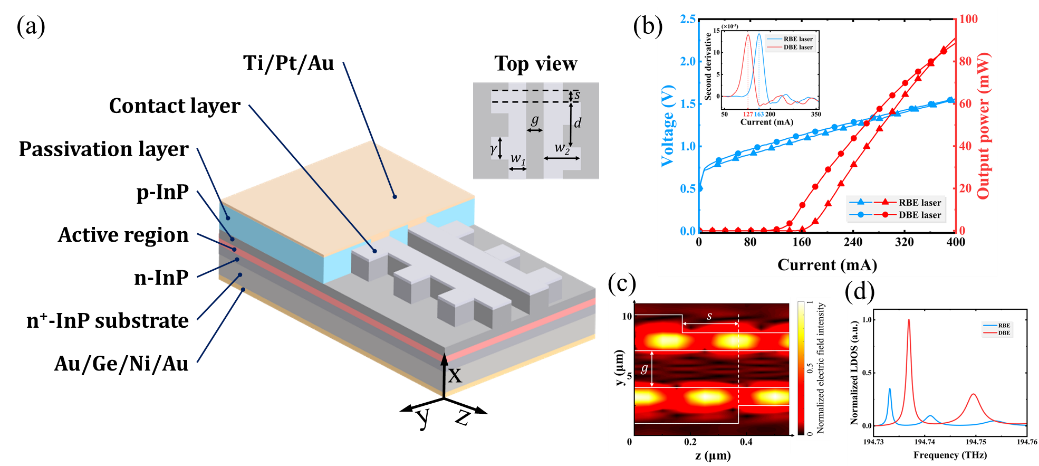

蘇州納米所納米加工平臺在InP基半導體激光器領域取得新進展

武漢芯源小容量存儲芯片EEPROM產品的特點

目前最先進的半導體工藝水平介紹

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

高精度半導體冷盤chiller在半導體工藝中的應用

功率半導體器件——理論及應用

半導體分層工藝的簡單介紹

意法半導體攜手華虹打造STM32全流程本地化供應鏈

半導體boe刻蝕技術介紹

半導體封裝中的裝片工藝介紹

關于華虹半導體力推95納米eNVM工藝平臺的介紹和研究

關于華虹半導體力推95納米eNVM工藝平臺的介紹和研究

評論