新思科技近日宣布MPW(多項目晶元)領先供應商MOSIS已選擇新思科技IC Validator工具進行物理驗證。IC Validator功能齊全的物理驗證解決方案,輔助以高度可擴展的引擎,助力MOSIS 大大提高物理驗證速度。MOSIS在FinFET工藝技術設計中為全芯片設計規則檢查(DRC)和版圖對照原理圖(LVS)signoff部署了IC Validator。

“MOSIS 提供MPW設計,為用戶加快生產速度并降低成本。我們需要一種高效的物理驗證解決方案,以確保設計流片的準時交付。IC Validator使我們的工程師具備滿足生產力和性能要求的各項功能,按時sign off。”

IC Validator是新思科技Fusion Design Platform?的關鍵組件。它是一個全面的物理驗證工具套件并可高度擴展,包括DRC、LVS、可編程電氣規則檢查(PERC)、虛擬金屬填充和可制造性設計(DFM)增強功能。IC Validator在架構時便秉持實現高性能和可擴展的宗旨,利用智能內存感知負載調度和平衡技術,讓主流硬件得到最大程度的利用。它可在多臺機器上同時使用多線程和分布式處理方法,利用可擴展性優勢,擴展到1000余個CPU。

“在先進的工藝技術中,由于制造復雜性的增強,按既定進度完成物理驗證成為新的挑戰。IC Validator滿足所有主要晶圓代工廠所提供的高性能、可擴展性和現成經優化的運行指令集(runset),為設計人員實現了生產芯片的最快途徑。”

-

新思科技

+關注

關注

5文章

957瀏覽量

52901 -

MOSIS

+關注

關注

0文章

2瀏覽量

2369

原文標題:MOSIS基于新思科技IC Validator進行FinFET芯片物理驗證

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

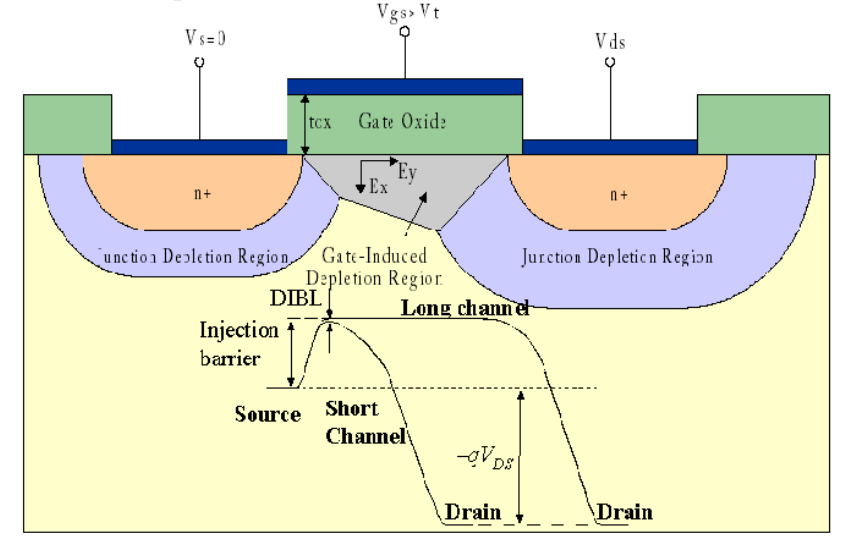

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

激光焊接技術在焊接馬蹄腳工藝中的應用

matlab的算法部署在simulink中

【產品介紹】L-Edit IC和L-Edit Advanced:模擬/混合信號 (AMS) 版圖

生成Bitstream的DRC LUTLP-1錯誤的解決辦法

華大九天Argus DRC技術詳解

霍爾IC在電動晾衣架中的應用與原理分析

霍爾IC在無刷電機中的應用與原理

體硅FinFET和SOI FinFET的差異

行芯科技揭示先進工藝3DIC Signoff破局之道

PPS注塑IC元件封裝中的應用優勢與工藝

Microchip通過設計內signoff DRC在成熟節點定制IC設計中實現顯著的生產率提升

MOSIS在領先的FinFET工藝設計中為DRC和LVS signoff部署IC Validator

MOSIS在領先的FinFET工藝設計中為DRC和LVS signoff部署IC Validator

評論