引言

UltraRAM 原語(也稱為 URAM)可在 Xilinx UltraScale +? 架構中使用,而且可用來高效地實現(xiàn)大容量深存儲器。

由于大小和性能方面的要求,通常這類存儲器不適合使用其他存儲器資源來實現(xiàn)。

URAM 原語具有實現(xiàn)高速內(nèi)存訪問所需的可配置流水線屬性和專用級聯(lián)連接。流水線階段和級聯(lián)連接是使用原語上的屬性來配置的。

本篇博文描述的是通過將 URAM 矩陣配置為使用流水線寄存器來實現(xiàn)最佳時序性能的方法。

注意:本文由 Pradip K Kar、Satyaprakash Pareek 和 Chaithanya Dudha 共同撰寫。

流水線需求:

通過在矩陣結構中連接多個 URAM,從可用的 URAM 原語實現(xiàn)大容量深存儲器。

矩陣由 URAM 的行和列組成。一列中的 URAM 使用內(nèi)置級聯(lián)電路級聯(lián),且多列 URAM 通過外部級聯(lián)電路互連,這被稱為水平級聯(lián)電路。

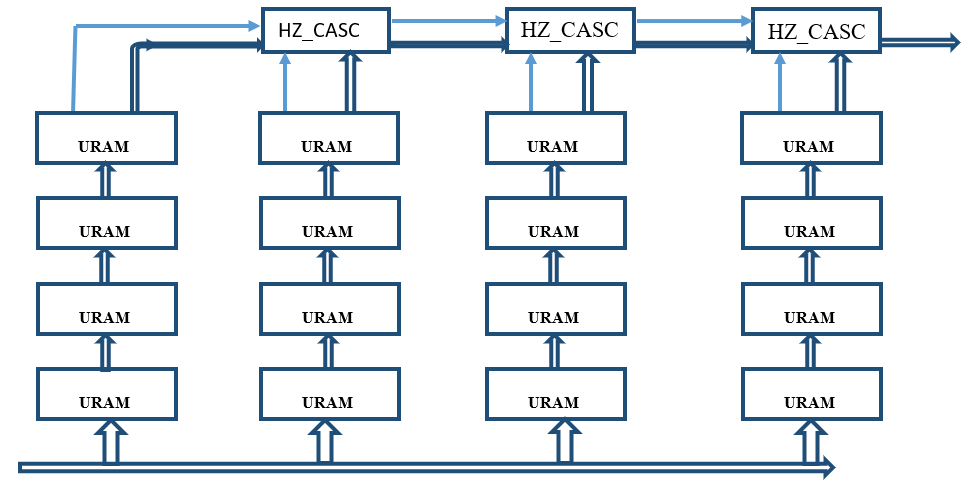

作為示例,圖 1 示出了針對 64K 深 x 72 位寬存儲器的 4x4 URAM 矩陣的矩陣分解。

圖 1:4 行 4 列的 URAM 矩陣(可實現(xiàn) 64K 深 72 位寬的存儲器)

在沒有流水線設計的情況下,深度聯(lián)結構會導致內(nèi)存訪問出現(xiàn)大的時鐘輸出延遲。例如,在默認情況下,上述 URAM 矩陣可以達到約 350 MHz。要以更快的速度訪問內(nèi)存,應插入流水線。如果在網(wǎng)表中指定了一定數(shù)量的輸出時延,Vivado Synthesis 即會自動實現(xiàn)此功能。

指定 RTL 設計中的流水線:

有兩種方法可以用來指定 RTL 設計中的流水線的用途,可以通過使用 XPM 流程,也可以通過行為 RTL 來推斷內(nèi)存。

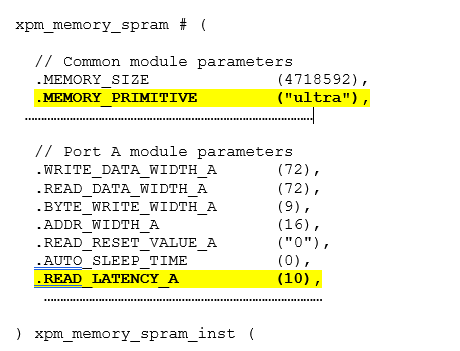

如果 RTL 設計通過 XPM 流程來創(chuàng)建 URAM 內(nèi)存,則用戶可以將對流水線的要求指定為 XPM 實例的參數(shù)。參數(shù)“READ_LATENCY_A/B”用于捕獲內(nèi)存的時延要求。

可用的流水線階段數(shù)是 LATENCY 值減去 2。例如,如果 Latency 設置為 10,則允許 8 個寄存器階段用于流水線操作。另外兩個寄存器可用來創(chuàng)建 URAM 本身。

圖 2:使用 XPM 設置流水線設計

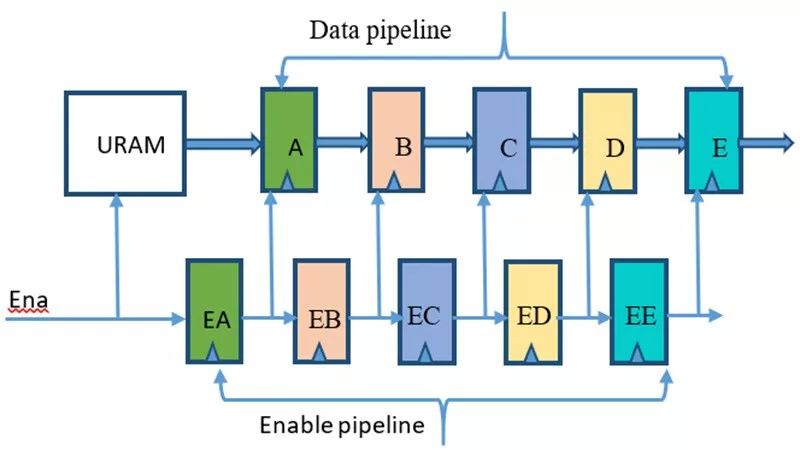

如果用戶使用 Vivado 用戶指南中提供的模板來編寫 RTL,并通過此方法來創(chuàng)建 URAM,那么,他們可以在 URAM 的輸出時創(chuàng)建盡可能多的寄存器階段。唯一的要求是,與數(shù)據(jù)一起,流水線寄存器的啟用也需要流水線化。

圖 3:URAM 塊輸出時的數(shù)據(jù)及流水線啟用規(guī)范

圖 3 顯示數(shù)據(jù)和流水線的啟用

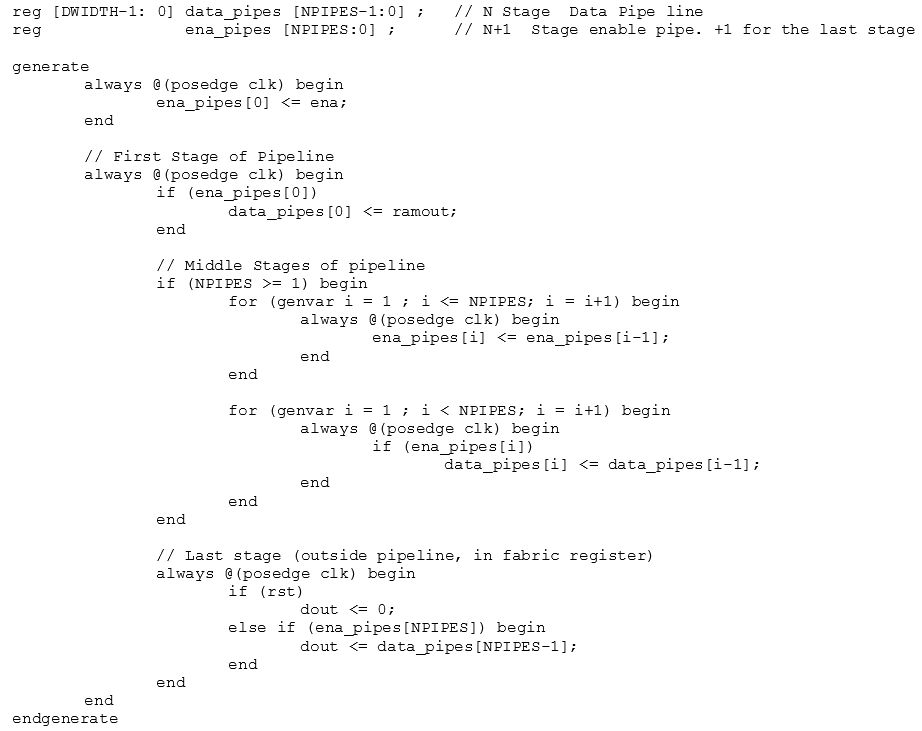

圖 4 示出了 RTL 級 RAM 流水線設計示例。

圖 4:用來指定數(shù)據(jù)和流水線啟用的 verilog 模板

分析日志文件:

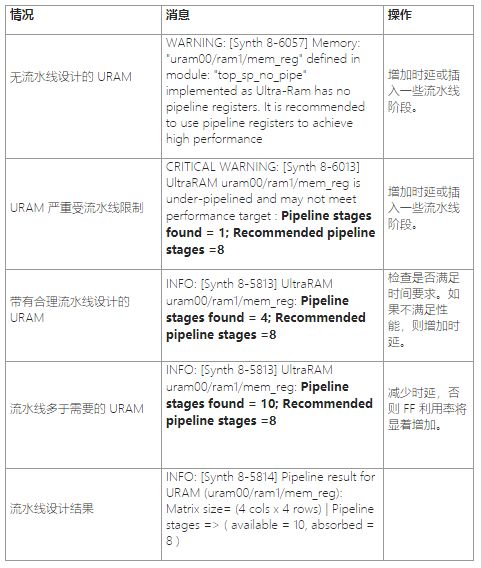

Vivado Synthesis 根據(jù)上下文環(huán)境和場景發(fā)布與 URAM 流水線相關的不同消息。下表說明要在 vivado.log文件中查找的一些消息和要采取的相應操作。

請注意,推薦的流水線階段基于可實現(xiàn)最高性能(800 MHz+)的完全流水線化的矩陣。此建議不受實際時序約束的限制。

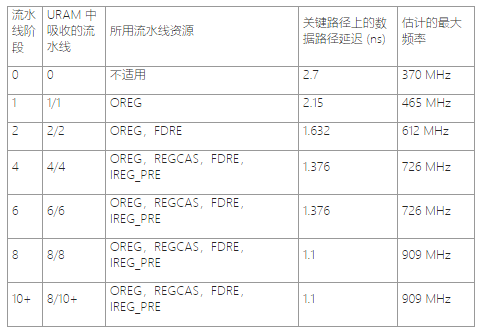

時間性能估計:

下表說明流水線寄存器的數(shù)量與可實現(xiàn)的最大估計頻率之間的關系。

請注意,實際的時間數(shù)仍將取決于最終地點和路線結果。

下列數(shù)字基于 speedgrade-2 Virtex? UltraScale+? 部件以及我們使用 4x4 矩陣實現(xiàn)的 64K x 72 URAM示例工程。

數(shù)據(jù)路徑延遲具有以下一個或多個組件。

Tco = 1.38 ns, Clk To CascadeOut on URAM

Tco = 0.82 ns, Clk To CascadeOut on URAM with OREG=true

Tco = 0.726 ns, Clk to Dataout on URAM with OREG=true, CASCADE_ORDER = LAST

URAM -> URAM級聯(lián)延遲= 0.2 ns

URAM -> LUT信號網(wǎng)絡延遲= 0.3 ns

LUT傳輸延遲= 0.125 ns

LUT -> LUT信號網(wǎng)絡延遲= 0.2 ns

LUT5 -> FF延遲= 0.05

結論:

URAM 原語是創(chuàng)建容量非常大的 RAM 結構的有效方法。它們被設置為易于級聯(lián)以便在您的設計中創(chuàng)建容量更大的 RAM。

但是,太多這類結構級聯(lián)在一起可能會通過 RAM 產(chǎn)生很大的延遲。從長遠來看,花時間讓您的 RAM 完全流水線化會帶來很多好處。

URAM 原語是創(chuàng)建容量非常大的 RAM 結構的有效方法。它們被設置為易于級聯(lián)以便在您的設計中創(chuàng)建容量更大的 RAM。

但是,太多這類結構級聯(lián)在一起可能會通過 RAM 產(chǎn)生很大的延遲。從長遠來看,花時間讓您的 RAM 完全流水線化會帶來很多好處。

-

寄存器

+關注

關注

31文章

5608瀏覽量

129966 -

時序設計

+關注

關注

0文章

21瀏覽量

44132

原文標題:通過在 Vivado Synthesis 中使 URAM 矩陣自動流水線化來實現(xiàn)最佳時序性能

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

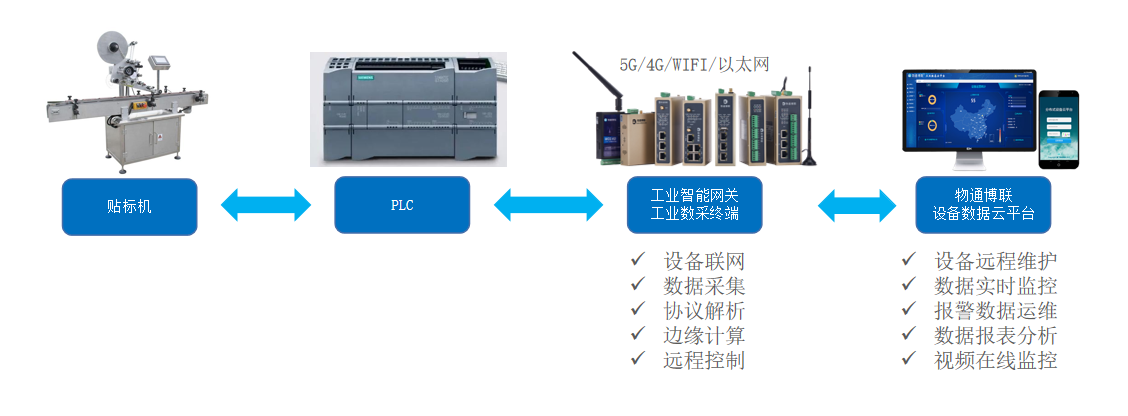

智造中樞:疆鴻智能DEVICENET轉(zhuǎn)MODBUS RTU網(wǎng)關在食品包裝流水線的融合之舞

流水線基本結構

如何更好地選擇工業(yè)流水線上用的條碼掃碼器?

常用硬件加速的方法

如何對蜂鳥e203內(nèi)核乘除法器進行優(yōu)化

流水線輸送帶數(shù)據(jù)采集物聯(lián)網(wǎng)解決方案

流水線掃碼升級選NVF230!工業(yè)二維碼讀碼器方案實測

自動化開裝封碼流水線數(shù)據(jù)采集解決方案

面包成型流水線數(shù)據(jù)采集遠程監(jiān)控系統(tǒng)

遠程io模塊在汽車流水線的應用

工業(yè)4.0時代,為什么你的流水線必須配備固定式掃碼器?

工業(yè)流水線上用的條碼掃碼器,如何選擇與使用?

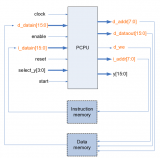

RISC-V五級流水線CPU設計

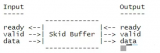

AXI握手時序優(yōu)化—pipeline緩沖器

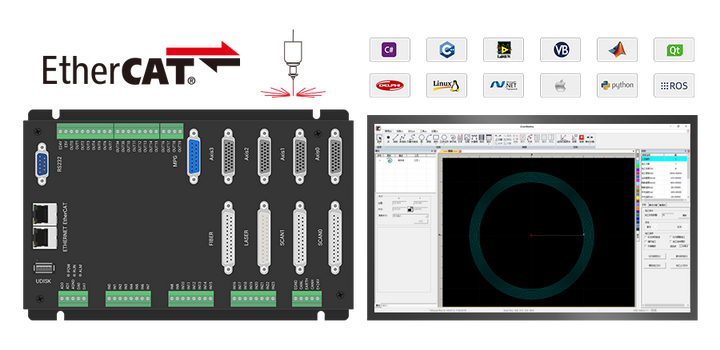

使用流水線寄存器實現(xiàn)最佳時序性能方案

使用流水線寄存器實現(xiàn)最佳時序性能方案

評論