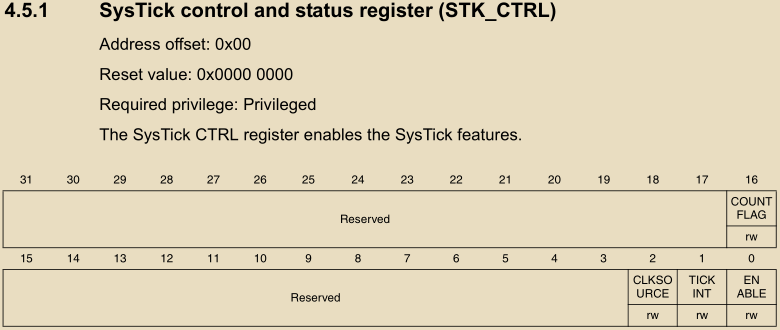

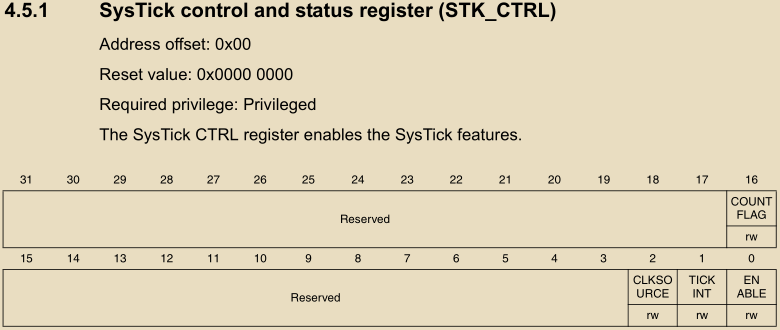

STM32處理器有一個24位的系統滴答定時器SysTick,它從重新加載值開始倒數到0,然后在下一個時鐘邊緣重新加載(包裝到)STK_LOAD寄存器中的值,然后在隨后的時鐘上倒數。

2023-07-21 17:47:18 2597

2597

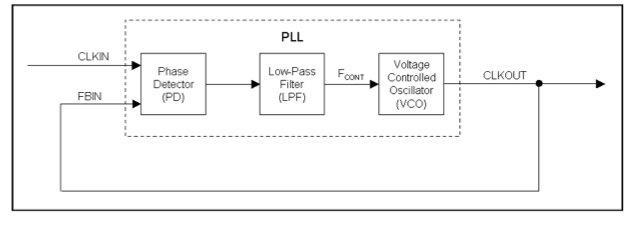

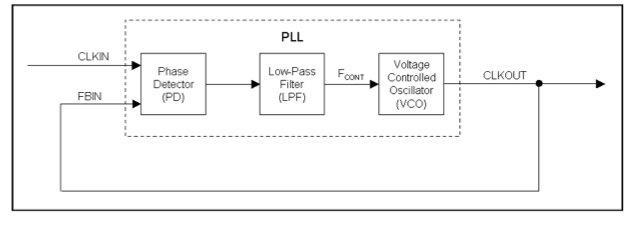

這里以鈦金的LVDS為例。 LVDS RX 時鐘選擇 LVDS時鐘的接收要連接名字為GPIOx_P_y_PLLINz名字的差分對,這樣的管腳直接驅動PLL,產生LVDS接收需要的fast_clk

2024-06-18 11:35:33 7247

7247

82C54含三個獨立的16位定時器,將T1和T2級聯使用時,將T1的out接到T2的CLK,使用方式2計數,但是問題在于當t1由2變的的clk時鐘下降沿時,out就輸出觸發T2減1,但是中斷觸發此時的數值,將會產生FFFF的差值,有什么好的解決辦法嗎

2015-06-08 14:47:25

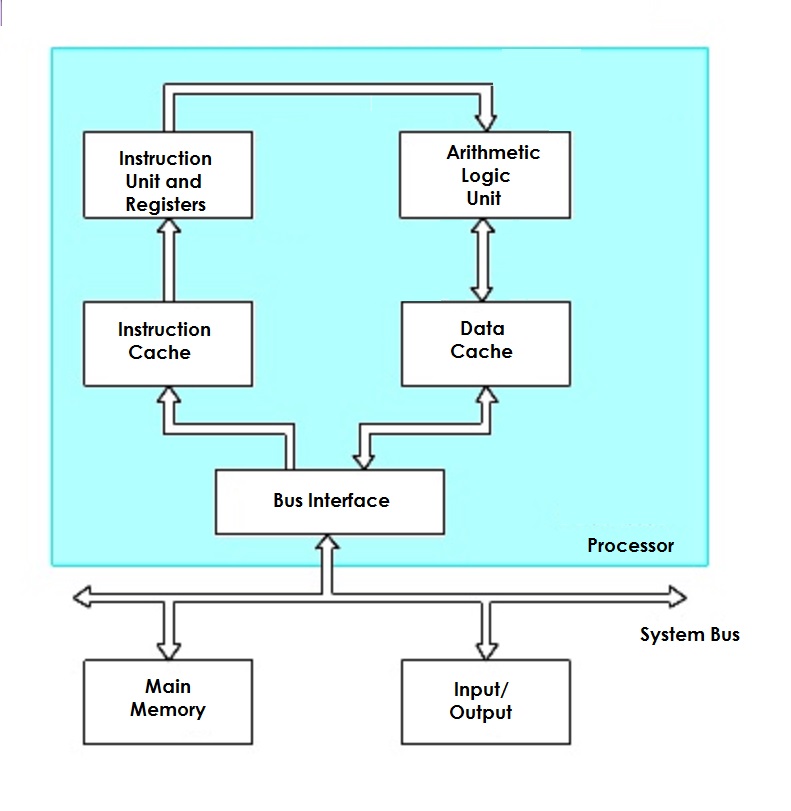

時鐘系統概述定義時鐘系統,它是由振蕩器(信號源)、定時喚醒器、分頻器等組成的電路。常用的信號源有晶體振蕩器和RC振蕩器。功能時鐘是嵌入式系統的脈搏,處理器內核在時鐘驅動下完成指令執行,狀態變換等動作

2021-08-02 08:32:49

1、STM32時鐘系統概述1.1 時鐘系統的概念與意義概念時鐘系統是由振蕩器(信號源)、定時喚醒器、分頻器等組成的電路。常用的信號源有晶體振蕩器和RC振蕩器。意義時鐘是嵌入式系統的脈搏,處理器內核在

2021-08-12 07:16:57

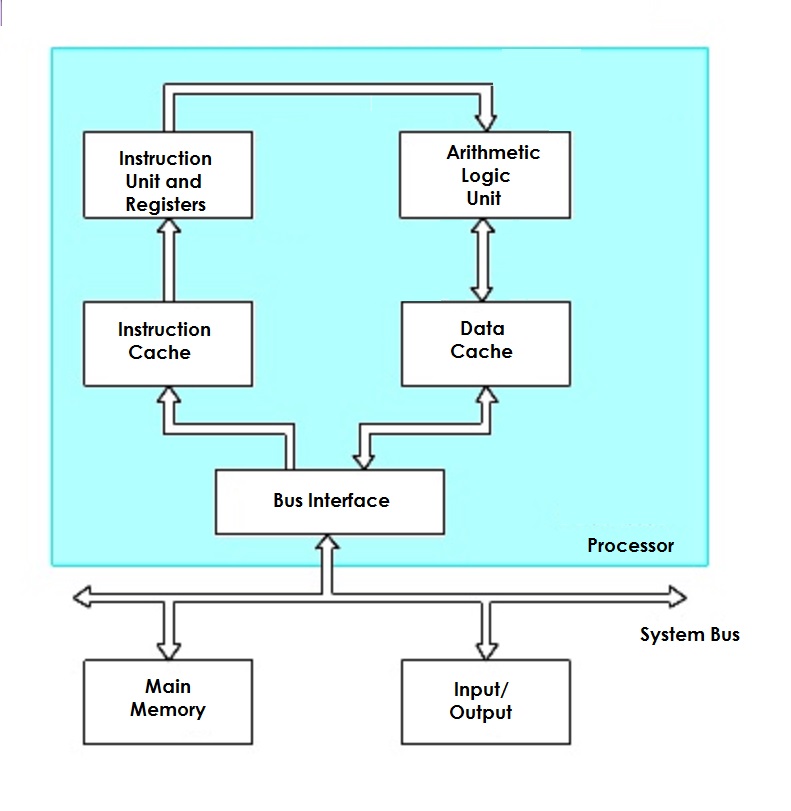

2.ARM微處理器的指令系統ARM微處理器的指令集是加載/存儲型的,即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。ARM

2021-12-20 06:54:28

所有使用Arm處理器的系統中都會包含一個標準化的通用定時器(Generic Timer)框架。這個通用定時器系統提供了一個系統計數器(System Counter)和一組定時器(Timer)。其結構

2022-04-22 10:23:43

噪聲條件或軟件錯誤而停止運行。如果配置為生成硬件重置,看門狗計時器將重置核心和處理器外圍設備。復位后,軟件可以通過詢問看門狗定時器控制寄存器中的狀態位來確定看門狗是否是硬件復位的源。計時器由系統時鐘

2020-10-09 17:03:34

你好,我使用的芯片是C6747,定時器采用32位非鏈式模式實現定時功能。請問,定時器選擇內部時鐘源時,這個內部時鐘源具體指的是PLL產生的哪一個系統時鐘?這個內部時鐘源指的是CPU時鐘嗎?謝謝

2018-08-01 09:39:51

成就更好的自己在吉林省電賽A題中用到了步進電機的控制,由于需要對步進電機的轉速和轉動角度都進行控制,因此博主想到了一種比較新奇的方法。目錄方法簡介與分析方法簡介優劣性CubeMX的定時器級聯配置內部級聯

2022-01-06 07:00:16

怎樣根據某些條件選擇DSP處理器的類型?比如:要求數據輸出時間間隔為1ms,速度數據類型為1個浮點型類型數據。急求大神指導!謝謝了!我對DSP處理器不太了解,暫時會用到這個技術。求指導!

2013-06-08 23:33:51

輸出功能FLASH存儲器通信類模塊定時器模塊最小系統參考設計更多信息咨詢請聯系angel.qi:***(微信與手機號碼同步)文末彩蛋最小系統參考設計注意事項晶體可以同時使用高速XTH和低速XTL,不使

2021-09-14 15:09:41

普遍認為開發多處理器系統軟件的難度要大于單處理器系統。但實際情況并非總是如此。我們這個在 TRW 汽車公司下屬的咨詢部 TRW Conekt 工作的設計團隊最近接管了一個項目,展示了如何根據手中的問題發揮硬件的功能,并通過使用許多個處理器開發出高效系統。

2019-10-23 08:00:03

只是一個很快的問題:我用Proteus VSM來模擬PIC18F2550,用MikroC編譯的HEX文件。MCU用4 MHz的外部晶體操縱。處理器運行在32兆赫(96兆赫PLL / 3)。現在我

2020-03-17 07:17:56

STM32定時器級聯功能怎么實現?

2021-11-24 06:40:04

和DMA使用的HCLK時鐘。②、通過8分頻后送給Cortex的系統定時器時鐘。③、直接送給Cortex的空閑運行時鐘FCLK。④、送給APB1分頻器。APB1分頻器可選擇1、2、4、8、16分頻,其輸出

2016-06-18 09:21:59

是嵌入式系統的脈搏,處理器內核在時鐘驅動下完成指令執行,狀態變化等動作,外設部件 在時鐘的驅動下完成各種工作,比如串口數據的發送,A/D轉換,定時器計數等等。因此時鐘對于計算機系統是至關重要的,通常時鐘系統出現問題也是致命的,比如振蕩器不起振、震蕩...

2021-08-12 07:16:05

??STM32最小系統主要由STM32F103RCT6微處理器、時鐘晶振電路、按鍵復位電路、電源穩壓電路以及BOOT電路等部分構成,該最小系統所使用的微處理器是一款32位的處理器,該處理器基于高性能

2021-08-13 07:36:34

電路在系統設計中JTAG的主要作用是將目標文件燒錄下載到處理器中。本次設計具體JTAG電路原理如圖所示:系統JTAG電路原理圖4.啟動模式電路BOOT0、BOOT1端口電平的不同設置,可以對三種不同啟動

2018-11-20 21:09:39

:HSI,HSE 和 PLL。在我們實際應用中,因為對時鐘速度要求都比較高我們才會選用 STM32F4 這種級別的處理器,所以一般情況下,都是采用 PLL 作為 SYSCLK時鐘源,而系統時鐘配置不正確就是PPL這里出了問題。先看一下主PPL在整個時鐘樹中間的位置。高速系統時鐘一般由PPL_P提供,一般配

2021-08-10 07:16:13

使用單個外部時鐘來獲得Clk和Clk / 1.001速率,但這需要一長串DCM和PLL。特別,27 MHz外部CLk- > DCM0- > DCM1- > PLL0產生74.25

2019-07-23 14:02:15

本文通過基于S3C44B0X處理器VxWorks嵌入式操作系統的BSP移植,詳細分析了VxWorks操作系統基于ARM處理器的中斷處理方法。

2021-04-27 06:28:03

我有一個設計,我使用2個時鐘域,用MMCM創建(我需要一個級聯來獲得我需要的確切頻率)。我已將'處理器系統復位'模塊連接到clk_out1和clk_out2時鐘輸出,因此每個域都會正確復位。我(想

2019-04-22 06:10:43

我怎么知道?我想做的網格接口PLL。我是否去FordSP33 EP256MU810系列?ISDSP33 EP256MU810是浮點型處理器。

2020-04-27 06:09:07

本實例系統是一個簡單的微處理器設計(你可以按照自己的需求配置處理器)。它包含以下內容:?單個Cortex-M3或Cortex-M4處理器。?內部程序存儲器。?SRAM數據存儲器。? Boot

2022-01-21 07:24:54

Teledyne e2v為系統設計師提供的定制方案處理器功耗的背景知識三種調整處理器系統功耗的方法

2021-01-01 06:04:09

一塊STM32處理器至少都有一個PLL,有的甚至有好幾個PLL。比如,F4有兩個PLL:F7有三個PLL:當然,每個MCU型號不同,其PLL數量,及功能也有差異,具體需要

2020-05-18 07:00:00

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

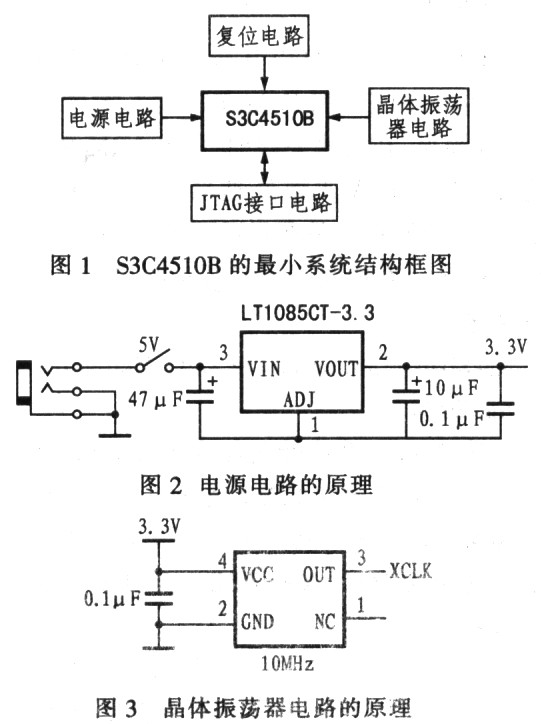

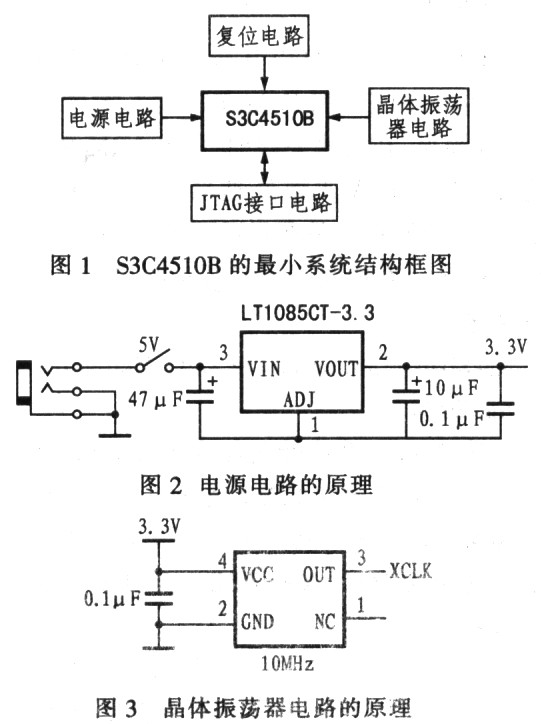

32位定時器;18個可編程I/O口;1個含有21個中斷源的中斷控制器和1個PLL電路。3 硬件設計3.1 最小系統設計最小系統是由保證微處理器可靠工作所必須的基本電路組成的。S3C4510B的最小系統

2011-11-25 10:03:34

基于微處理器的電池檢測系統設計

2021-03-11 06:09:12

低功率模式經常被忽視而沒有得到利用。有了現在的高性能嵌入式處理器,“開”或“關”不再是一個問題。新的處理器可有多個狀態,如運行、打盹、小睡、睡眠以及深度睡眠模式等,每種狀態下對處理器時鐘、PLL以及

2019-07-15 06:40:13

處理器。通過在兩個執行內核之間劃分任務,多核處理器可在特定的時鐘周期內執行更多任務。 多核技術能夠使服務器并行處理任務,多核系統更易于擴充,并且能夠在更纖巧的外形中融入更強大的處理性能,這種外形所用

2019-06-20 06:47:01

的各個領域。采用INMOS公司的IMS A100級聯型信號處理器為模板,以FIR濾波器設計為核心,用FPGA技術開發設計級聯型信號處理器,能夠應用于數字FIR濾波、高速自適應濾波、相關和卷積、離散

2019-07-30 07:22:48

針對汽車數字信號處理應用的各種處理器類型,有什么優缺點?如何選擇汽車電子系統中的處理器?

2021-05-14 06:59:41

基于特定的開發板上的時鐘策略:倍頻/分頻系數需要在使能 PLL 之前進行配置,所以需要在 Open PLL 之前將所有系統的時鐘分頻器系數以及PLL的倍頻系數配置好。整個時鐘的配置流程如下所示:(1

2021-08-23 09:12:44

求大神分享一種基于FPGA的級聯結構FFT處理器的優化設計

2021-05-06 07:34:53

引言 隨著數字信號處理(DSP)技術的迅猛發展,以數字信號處理器及相關算法為技術的數字降噪聲技術也不斷出現。本文提到的JK-DP50型數字降噪聲處理器就是應用數字信號處理器DSP技術及高速實時處理

2019-07-04 06:03:56

的時鐘生成單元會最先工作,這時候處在參考時鐘ref_clk下(通常是10-100MHz),待到PLL輸出穩定后,時鐘生成單元會把給處理器的時鐘切換到正常工作頻率,并釋放處理器的復位信號,通常我們稱這個復位

2022-07-19 15:00:47

。 ②通過 8 分頻后送給 Cortex 的系統定時器時鐘,也就是 systick 了。 ③直接送給 Cortex 的空閑運行時鐘 FCLK。 ④送給 APB1 分頻器。 APB1 分頻器輸出一路供

2018-04-28 13:12:28

STM32時鐘系統是什么意思?STM32時鐘系統有什么意義呢?SysTick定時器的工作原理是什么呢?如何去實現對SysTick定時器的初始化呢?

2021-11-22 07:37:04

請問,想通過FPGA的PLL倍頻產生個500MHz的時鐘來使用,以此時鐘來做定時精密延遲,不知道PLL倍頻倍數有什么要求,比如好像有的器件支持不到500MHz,有沒有可推薦的器件呢

補充內容 (2017-1-4 09:26):

或者有大神用過類似能到500MHz的FPGA推薦么

2017-01-03 17:04:23

怎么設計一種級聯型多電平變流器?級聯型多電平變流器具有哪些特點?基于STS—SVM的三相級聯型多電平變流器有什么技術特點?

2021-04-14 06:48:51

怎樣設計FIR濾波器結構?怎樣設計級聯型信號處理器?如何對級聯型信號處理器進行仿真測試?

2021-04-28 07:04:01

寄存器的200 MHz時鐘,我試圖使用時鐘向導獲得超過900 MHz的單端但沒有幫助我的問題是我能從PLL,DCM或級聯PLL DCM獲得多大的輸出頻率限制? ,甚至可以從PLL或DCM獲得1.2 GHz?我將衷心感謝您的幫助問候,Morlerm

2019-08-02 06:10:13

音頻系統對處理器芯片有什么要求?

2021-06-03 06:03:34

針對直接數字頻率合成(DDS)和集成鎖相環(PLL)技術的特性,提出了一種新的DDS 激勵PLL 系統頻率合成時鐘發生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用濾波的方法

2009-12-14 10:22:00 36

36 一種具有功耗管理特性的DSP處理器的結構設計。該處理器采用4級流水線和增強型的哈佛并行系統結構及完善的時鐘管理模塊,提供了一種DSP處理器的集成設計。

2010-11-19 14:45:37 21

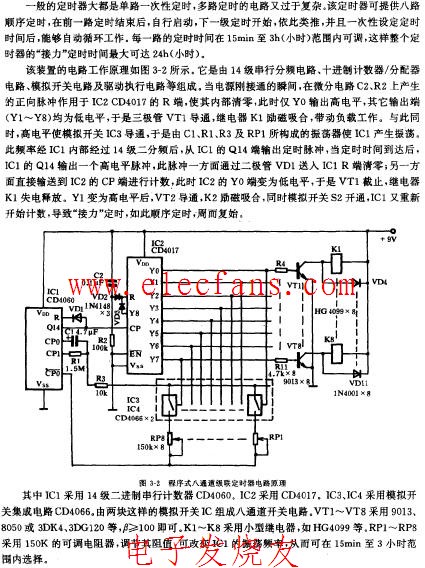

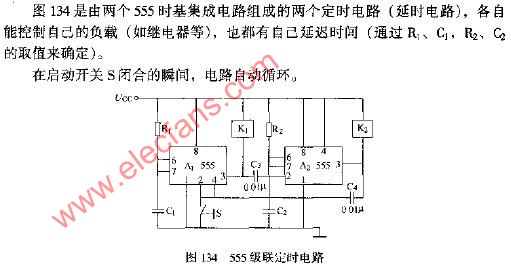

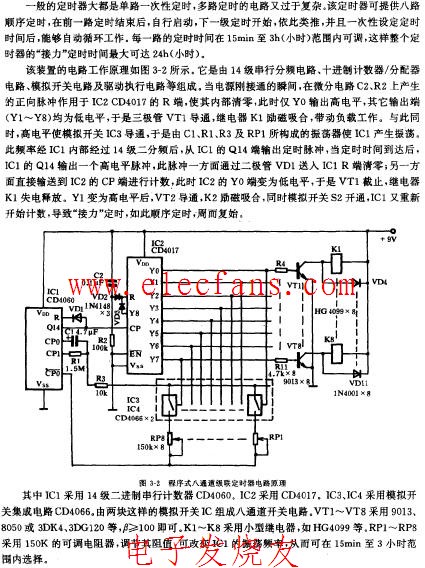

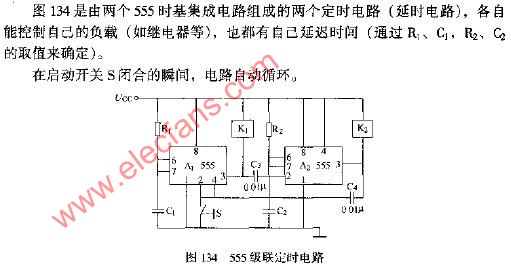

21 程序式八通道級聯定時器

2008-08-10 23:04:10 3213

3213

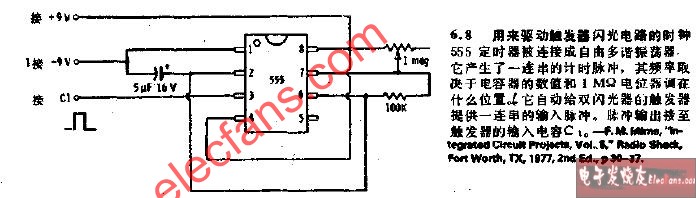

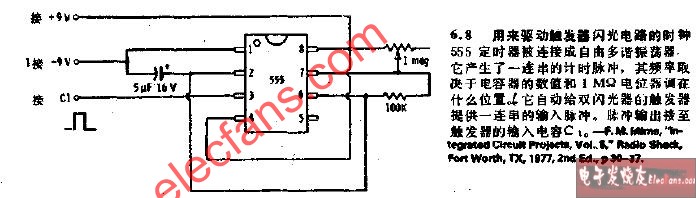

時鐘555定時器電路

2009-01-17 14:08:18 2812

2812

ICNexus應用處理器助力實現智能型運輸車輛系統

用新科際整合公司采用ICNexus 32位應用處理器NXC2620推出一款智能型運輸車輛系統,結合LCD觸控式面板、網絡、通信及語音

2009-12-02 08:36:48 925

925 基于FPGA的級聯結構FFT處理器的優化設計

0 引 言

數字信號處理主要研究采用數字序列或符號序列表示信號,并用數字計算方法對這些序列進行處理,以便

2009-12-28 11:07:33 2590

2590

555級聯定時電路圖

2010-03-30 15:13:36 828

828

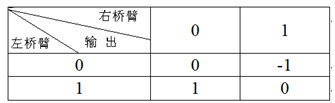

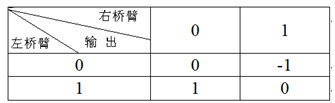

基于H橋級聯型逆變器PWM控制設計方案

摘 要:本文主要對大功率高壓變頻器H橋級聯型逆變器的實現方式進行了探討,主要從系統中

2010-04-27 09:38:32 9582

9582

本文介紹S3C4510B型ARM微處理器最小系統的構建,并給出系統外圍相關器件的選型。

2011-08-19 14:33:08 3579

3579

高壓級聯型SVG系統設計與裝置研發

2017-11-08 17:18:50 2

2 當PLL參考時鐘和PLL反饋時鐘的頻率和相位相匹配時,PLL則被稱為是鎖定狀態。達到鎖定狀態所需的時間稱為鎖定時間,這是PLL設計最關鍵的參數之一。

2018-03-14 15:17:00 7951

7951

目前對時鐘頻率還能代表處理器性能的話題在網上議論紛紛,情況有點復雜,自從英特爾在2008年推出睿頻加速技術能動態、自動地對處理器超頻后,這一技術就越來越普及了,在市場上銷售的處理器都能根據能耗和熱裕

2018-04-28 16:42:56 8486

8486 下一代微處理器通過增加系統功耗繼續挑戰電力系統設計者。

2018-05-16 09:21:58 6

6 用途:

1.產生操作系統的時鐘節拍

2.便于不同處理器之間程序移植

SysTick定時器被捆綁在NVIC中,異常號15

3.作為一個鬧鈴測量時間用于測量時間,

但當處理器在調試期間被喊停(halt)時,則SysTick定時器亦將暫停運作。

2018-12-11 15:44:49 4637

4637 本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2020-09-23 10:45:00 2

2 設計是基于嵌入式技術作的最小系統設計,一個嵌入式處理器自己是不能獨立工作的,必須給它供電、加上時鐘信號、提供復位信號,如果芯片沒有片內程序存儲器,則還要加上存儲器系統,然后嵌入式處理器芯片才可能工作。這些提供嵌入式處理器運行所必須的條件的電路與嵌入式處理器共同構成了這個嵌入式處理器的最小系統。

2020-10-28 16:54:29 16

16 (或晚期)時鐘的影響。早期時鐘定義為輸出時鐘的相位相對于參考輸入時鐘提前的情況。 簡介 時鐘驅動器架構有兩種主要類型:緩沖器型和帶鎖相環 (PLL) 的反饋型。在緩沖器型(非 PLL)時鐘驅動器中,輸入波通過器件傳播并由輸出緩沖器“重新驅動”。

2021-06-15 10:48:41 3297

3297

纖巧型低頻時鐘支持長持續時間上電復位和看門狗定時器應用

2021-03-20 22:22:07 6

6 EE-261:了解基于PLL的處理器的抖動要求

2021-04-23 14:39:28 10

10 EE-290:管理SHARC?處理器上的核心PLL

2021-05-20 14:49:15 2

2 PLL設計和時鐘頻率產生機理免費下載。

2021-06-07 14:36:43 22

22 款跟控制器/處理器相關的器材: 嵌入式開發系統板 TI MCU系統板 - 畢竟TI是贊助商,有一道題目中指定要用到TI的產品 微處理器最小系統板 不談TI的MCU系統板,那還有嵌入式開發系統板和微處理器最小系統板,從紙面上理解,這二者還是有一定的差異的

2021-08-10 15:59:16 4671

4671 ??STM32最小系統主要由STM32F103RCT6微處理器、時鐘晶振電路、按鍵復位電路、電源穩壓電路以及BOOT電路等部分構成,該最小系統所使用的微處理器是一款32位的處理器,該處理器基于高性能

2021-11-06 14:21:00 10

10 最小系統1,、供電電路2、復位電路3、時鐘:外部晶振(2個)4、Boot啟動模式選擇5、下載電路(JTAG)6、后背電池時鐘詳解:在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE

2021-11-17 15:36:02 12

12 華大HC32-(02)-系統時鐘和基本定時器

2021-11-23 18:06:41 31

31 系統時鐘配置錯誤而產生的串口定時器等問題在 STM32 中,有五個時鐘源,為 HSI、HSE、LSI、LSE、PLL。從時鐘頻率來分可以分為高速時鐘源和低速時鐘源,在這 5 個中 HIS,HSE

2021-11-23 18:21:38 9

9 系統的心跳時鐘。這樣可以節省MCU資源,不用浪費一個定時器。比如uCOS中,分時復用,需要一個最小的時間戳,一般在STM32+UCOS系統中,都采用Systick做uCOS心跳時鐘。Systick定時器

2021-12-31 19:46:43 15

15 為什么使用STM32F1定時器的級聯,主要是因為某些對于計時要求高的場合,而STM32F1單片機16位的定時器最多計數65535,那么很明顯us級別的計時只能維持6.5535ms,有時候解算過程可能

2022-01-17 09:34:11 16

16 每個A9處理器都有私有的32位定時器和32位看門狗定時器。兩個處理器共享一個64位定時器。這些定時器的時鐘始終是的CPU頻率的1/2(CPU_3x2x)。

2022-04-29 10:19:13 4888

4888 英特爾至強 D-1529:英特爾的 D-1529 不是針對汽車應用,而是旨在滿足IEC 61508安全集成級別 (SIL) 認證標準下的工業需求。該設計包括冗余鎖步處理器對、窗口看門狗定時器、時鐘

2022-08-10 11:33:39 2201

2201

在處理器控制的系統中,功耗與處理器的時鐘速度成正比。如果處理器上的計算負載很小,則大部分功率都會被浪費。將處理器速度調制到盡可能慢的頻率,同時保持執行手頭任務的最低計算能力可以減少這種浪費。本應用筆記描述了使用DS1077通過PC主機控制來控制8051型微處理器的時鐘速度。

2023-03-01 15:12:12 818

818

在處理器控制的系統中,功耗與處理器的時鐘速度成正比。如果處理器上的計算負載很小,則大部分功率都會被浪費。將處理器速度調制到盡可能慢的頻率,同時保持執行手頭任務的最低計算能力可以減少這種浪費。本應用筆記描述了使用DS1077通過PC主機控制來控制8051型微處理器的時鐘速度。

2023-06-01 19:05:13 858

858

介紹S3C4510B型ARM微處理器和基于該處理器設計的最小系統,概述該系統外圍應用電路的選型,以便使用者自行設計開發。

2023-07-23 15:17:02 1553

1553

pll鎖定時間按照頻率精度多少來計算? PLL鎖定時間是指當PLL嘗試將輸出頻率與輸入頻率相匹配時所需的時間。這個時間可以用來衡量PLL的性能,因為它決定了PLL能否快速、準確地鎖定頻率,并且

2023-09-02 15:12:23 2867

2867 時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll? 時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相環

2023-10-13 17:39:50 2233

2233 時及時響應。這些異常情況包括中斷、陷阱、系統調用等。在本文中,我們將介紹ARM處理器的中斷源以及對異常中斷的響應過程。 一、ARM處理器的中斷源 1.時鐘中斷 時鐘中斷是ARM處理器最基本的中斷源之一。ARM處理器內置一個時鐘,用來控制其內部的

2023-10-19 16:35:59 2359

2359 鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢? 鎖相環(Phase Locked Loop, PLL)是一種電路系統,它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環中,反饋回路

2023-10-23 10:10:15 4766

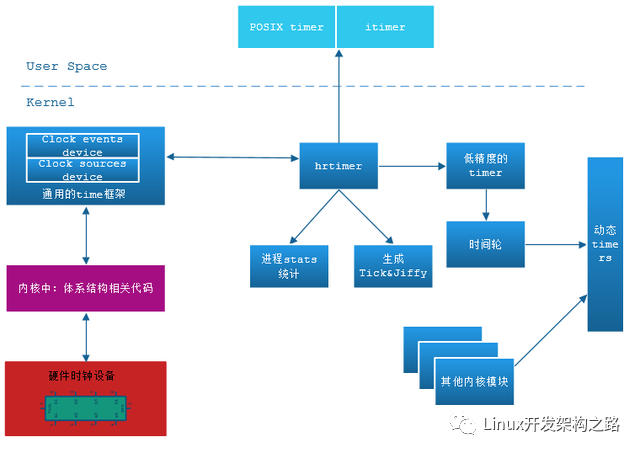

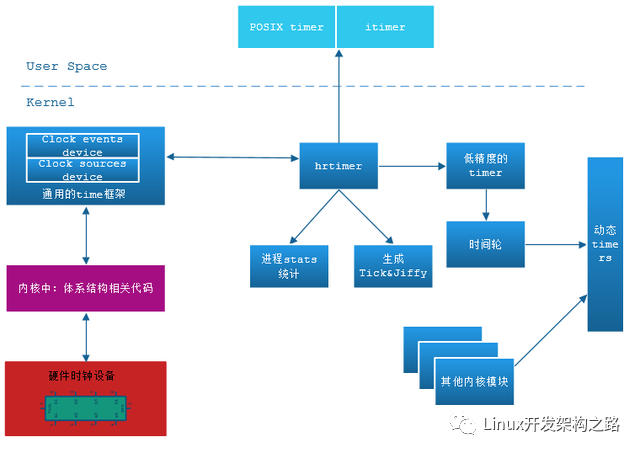

4766 Linux內核時鐘系統和定時器實現 Linux 2.6.16之前,內核只支持低精度時鐘,內核定時器的工作方式: 系統啟動后,會讀取時鐘源設備(RTC, HPET,PIT…),初始化當前系統時間

2023-11-09 09:12:12 2357

2357

替代SiTime,可編程振蕩器用于視頻處理器穩定時鐘信號

2024-06-28 09:50:44 902

902

電子發燒友網站提供《PLL1705/PLL1706雙通道PLL多時鐘發生器數據表.pdf》資料免費下載

2024-08-22 11:32:10 0

0 電子發燒友網站提供《OMAP5912多媒體處理器時鐘參考指南.pdf》資料免費下載

2024-12-17 16:17:43 0

0 電子發燒友網站提供《EE-290:管理SHARC處理器上的內核PLL.pdf》資料免費下載

2025-01-05 09:41:59 0

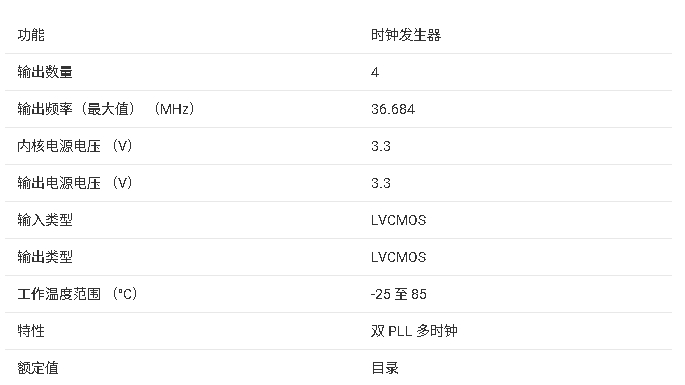

0 PLL1707成本低、鎖相 環路 (PLL) 多時鐘發生器。PLL1707和 PLL1708可以從 27 MHz 生成四個系統時鐘 參考輸入頻率。的時鐘輸出 PLL1707可以通過采樣頻率控制來控制

2025-09-22 13:57:44 598

598

PLL1707成本低、鎖相 環路 (PLL) 多時鐘發生器。PLL1707和 PLL1708可以從 27 MHz 生成四個系統時鐘 參考輸入頻率。的時鐘輸出 PLL1707可以通過采樣頻率控制來控制

2025-09-22 14:01:08 637

637

電子發燒友App

電子發燒友App

評論