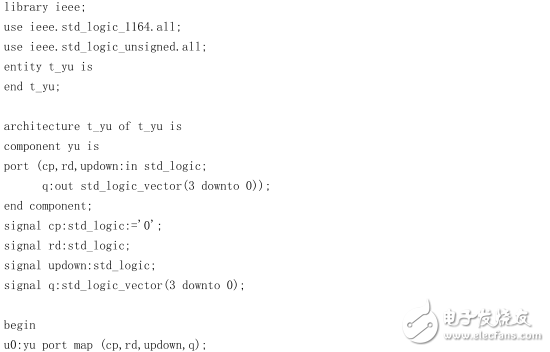

仿真測試程序

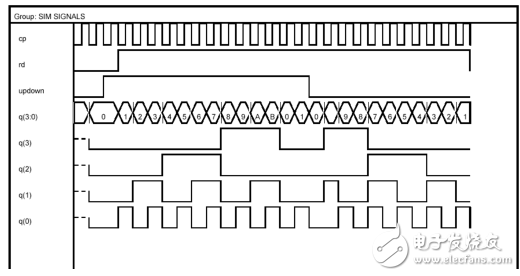

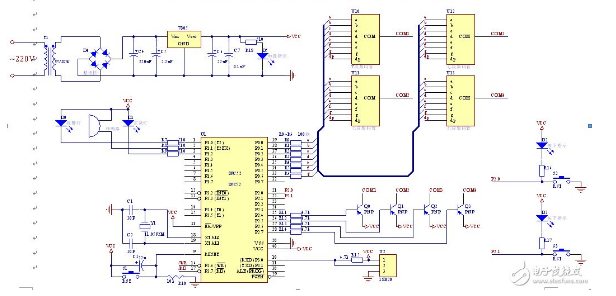

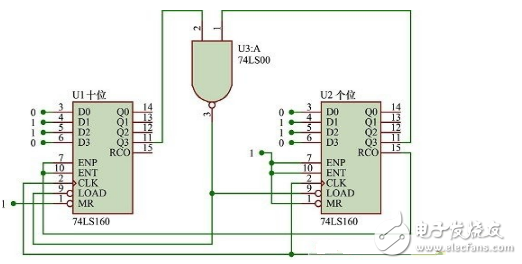

仿真圖

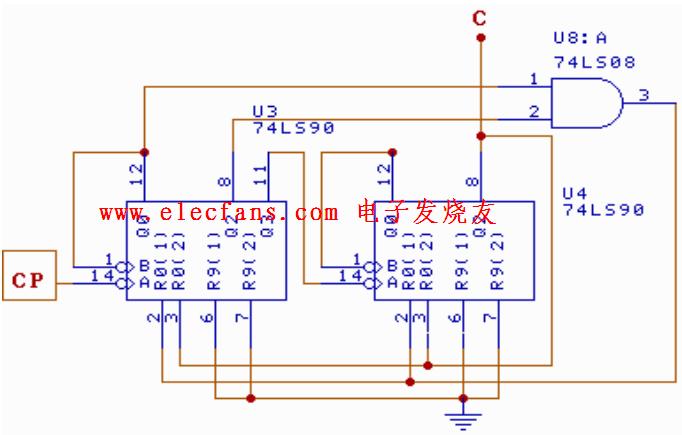

12進制計數器設計方案四:異步十二進制加減法計數器設計2

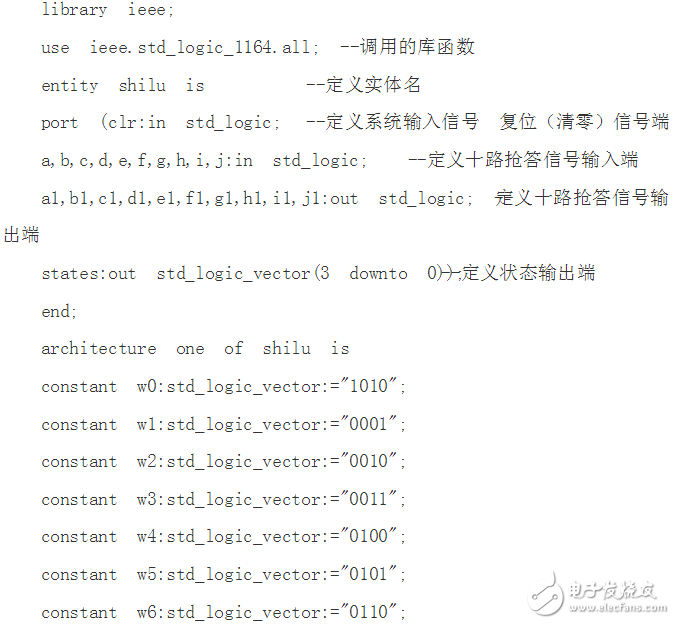

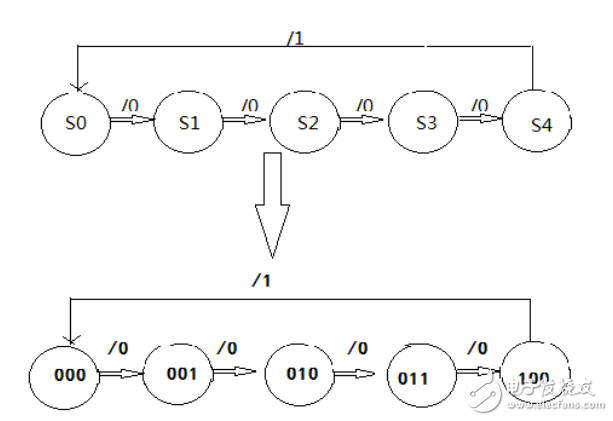

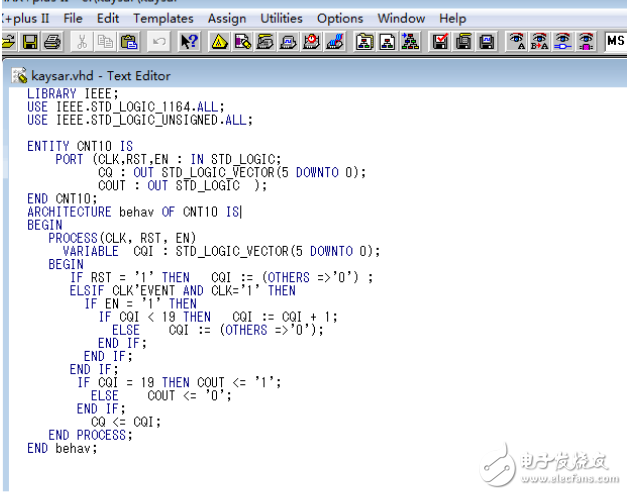

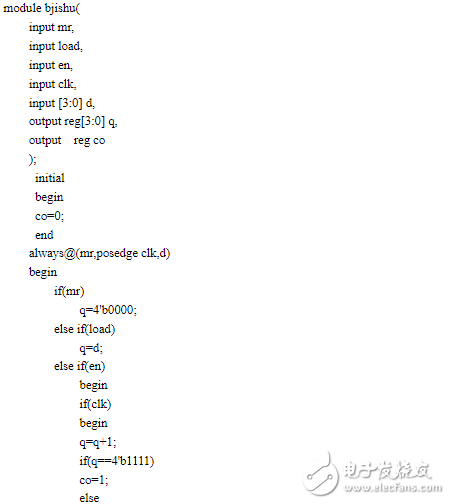

VHDl設計思路

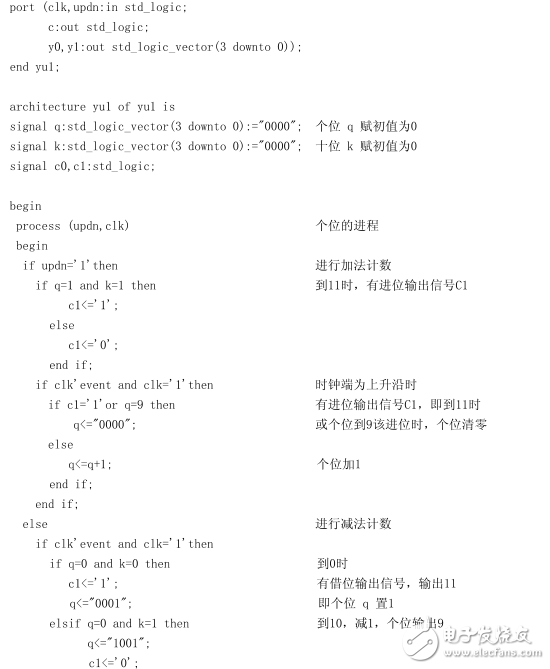

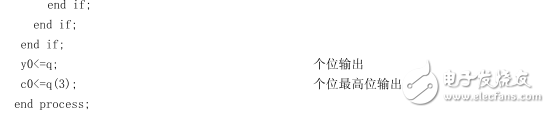

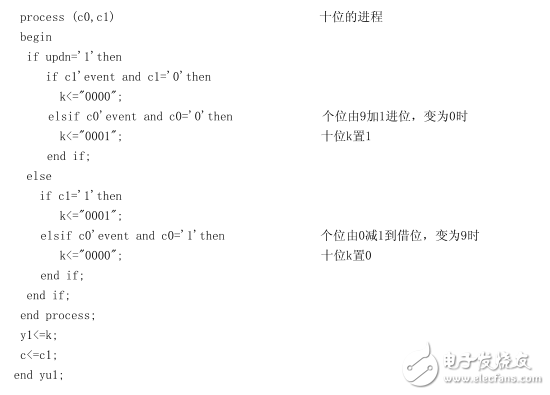

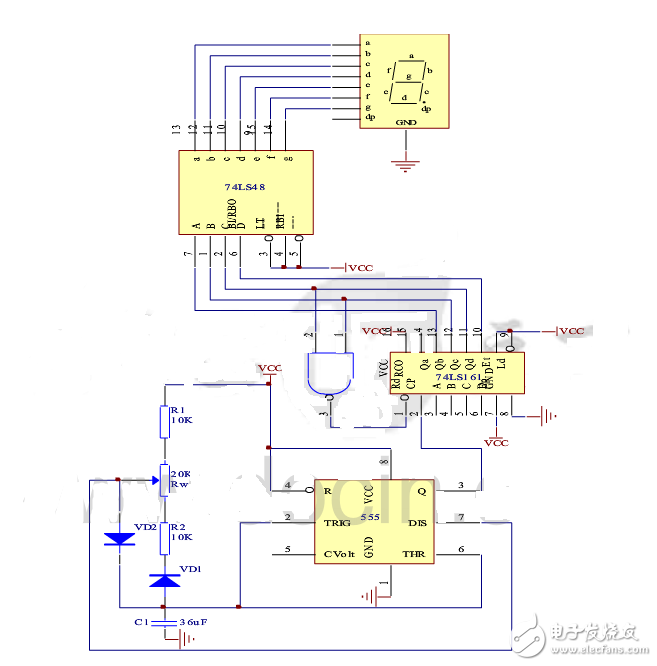

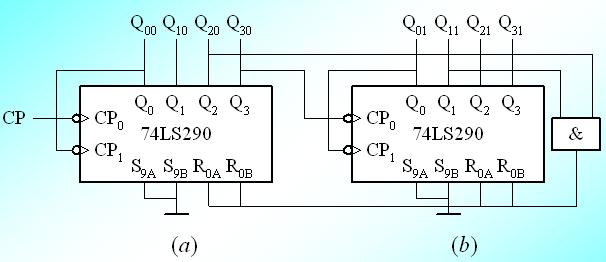

設計中,clk 是時鐘輸入端,上升沿有效;updn 為計數方式控制端,updn=“1”時作加法計數,updn=“0”時作減法計數; c 是進位/借位輸出端; c0 為個位最高位輸出。在計數工作之前,個位q 和十位k 全部置0。個位由時鐘上升沿觸發(fā)加/減1,十位由個位的進位/借位觸發(fā),從而實現十位的變化,即異步可逆計數。當updown=“1”時,計數器進行加法計數,個位從“0”依次計數到“9”,進位,十位由“0”到“1”,當計數到11時清零;同理,當updown=“0”時,計數器進行減法計數。

程序設計

電子發(fā)燒友App

電子發(fā)燒友App

評論