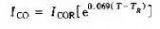

40個(gè)單片機(jī)晶振問題及解決方法小結(jié)

單片機(jī)晶振電路中兩個(gè)微調(diào)電容不對(duì)稱會(huì)怎樣?相差多少會(huì)使頻率怎樣變化?我在檢測無線鼠標(biāo)的接受模塊時(shí),發(fā)....

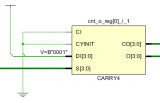

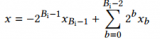

如何在FPGA中實(shí)現(xiàn)高效的compressor加法樹呢?

大規(guī)模的整數(shù)加法在數(shù)字信號(hào)處理和圖像視頻處理領(lǐng)域應(yīng)用很多,其對(duì)資源消耗很多,如何能依據(jù)FPGA物理結(jié)....

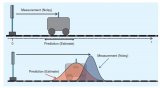

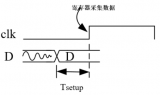

靜態(tài)時(shí)序分析基礎(chǔ)知識(shí)

為了確保寄存器在時(shí)鐘沿穩(wěn)定采集數(shù)據(jù),那么必須要滿足寄存器的建立,保持時(shí)間要求。 建立時(shí)間要求:在寄存....

如何用LUT做一個(gè)可動(dòng)態(tài)配置的卷積核呢?

由于卷積核數(shù)據(jù)在計(jì)算過程中保持不變,更新較慢。這樣就可以利用LUT來存儲(chǔ)權(quán)重并同時(shí)進(jìn)行乘法運(yùn)算。

Xilinx FPGA學(xué)習(xí)筆記

方法1.通過狀態(tài)機(jī)來實(shí)現(xiàn),通過verilog控制FPGA,讓它該快的時(shí)候快,該慢的時(shí)候慢。

嵌入式軟件與生態(tài)系統(tǒng):為嵌入式開發(fā)者提供必要的組件

Xilinx 提供兩款工具來構(gòu)建和部署嵌入式 Linux 解決方案。這些工具有 Xilinx 的 P....

Vitis加速庫:廣泛且性能優(yōu)化的開源庫

Vitis 統(tǒng)一軟件平臺(tái)包括一組廣泛的、性能優(yōu)化的開源庫,這些庫提供了即開即用的加速功能,并且對(duì)現(xiàn)有....

您的存儲(chǔ)器堆疊了嗎?—賽靈思推出16GB HBM FPGA

當(dāng)您想到處理性能時(shí),腦子里最先出現(xiàn)的影響因素往往并不是存儲(chǔ)吧?但是,如果您正在處理海量的大型數(shù)據(jù)集,....

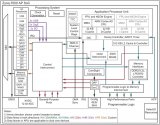

ZC706千兆網(wǎng)測試(ZYNQ,F(xiàn)reeRTOS,Echo,lwIP,TCP,RGMII)

ARM端配置如下圖所示,以5處的ARM-A9為核心,使用1處的UART1打印調(diào)試信息,使用2處的網(wǎng)口....

性能、價(jià)格、功耗的“三體問題”解:Xilinx KU19P

PON接入:無源光網(wǎng)絡(luò) (PON) 是網(wǎng)絡(luò)運(yùn)營商部署的主要寬帶接入技術(shù)之一。依托可編程邏輯和硬件加速....

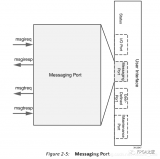

【FPGA】SRIO IP核系統(tǒng)總覽以及端口之Messaging Port介紹

消息傳遞端口是可選接口(消息也可以組合到I / O端口上,并使用Vivado集成設(shè)計(jì)環(huán)境(IDE)設(shè)....

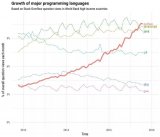

30年,Python正在吞食世界

一個(gè)人開發(fā)一門語言,難度那是相當(dāng)大的。好在當(dāng)時(shí)而立之年的Guido已經(jīng)有了相當(dāng)?shù)拈_發(fā)經(jīng)驗(yàn)。此前,他花....

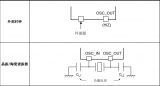

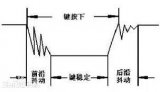

FPGA內(nèi)實(shí)現(xiàn)按鍵消抖的方法

通常的按鍵所用開關(guān)為機(jī)械彈性開關(guān),當(dāng)機(jī)械觸點(diǎn)斷開、閉合時(shí),由于機(jī)械觸點(diǎn)的彈性作用,一個(gè)按鍵開關(guān)在閉合....

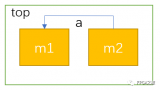

在模塊化設(shè)計(jì)過程中編寫testbench并仿真的方法介紹

?在開始設(shè)計(jì)前,根據(jù)設(shè)計(jì)劃分好各功能模塊(為了敘述方便,這里以對(duì)“FPGA數(shù)字信號(hào)處理(十三)鎖相環(huán)....

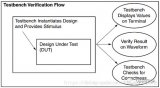

Testbench自動(dòng)化驗(yàn)證方法介紹

自動(dòng)化驗(yàn)證testbench結(jié)果可以減少人工檢查的時(shí)間和可能犯的失誤,尤其對(duì)于比較大的設(shè)計(jì)。

Testbench編寫指南(2)讀取txt文件數(shù)據(jù)

用“數(shù)組”來表述Verilog HDL中的定義并不準(zhǔn)確,但對(duì)大多數(shù)人來說應(yīng)該更好理解。

Testbench的基本組成和設(shè)計(jì)規(guī)則

??對(duì)于小型設(shè)計(jì)來說,最好的測試方式便是使用TestBench和HDL仿真器來驗(yàn)證其正確性。一般Te....