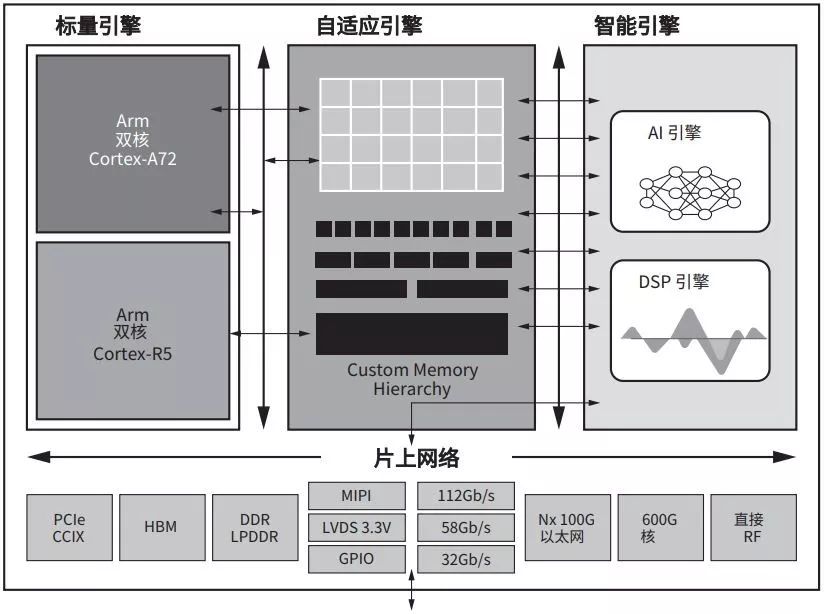

賽靈思正式推出 Versal ACAP,這是一個完全支持軟件編程的異構(gòu)計算平臺,可將標(biāo)量引擎、自適應(yīng)引擎和智能引擎相結(jié)合,實現(xiàn)顯著的性能提升,其速度超過當(dāng)前最高速的 FPGA 20 倍、比當(dāng)今最快的 CPU 實現(xiàn)快 100 倍,該平臺面向數(shù)據(jù)中心、有線網(wǎng)絡(luò)、5G 無線和汽車駕駛輔助應(yīng)用。

近期在半導(dǎo)體工藝領(lǐng)域涌現(xiàn)的技術(shù)挑戰(zhàn)阻礙了傳統(tǒng)上通用 (one-size-fits-all) 型 CPU 標(biāo)量計算引擎的擴(kuò)展。如圖 1 所示,半導(dǎo)體工藝頻率縮放的變化迫使標(biāo)準(zhǔn)計算單元愈發(fā)趨于并行。

因此,半導(dǎo)體工業(yè)正在探索替代特定領(lǐng)域的架構(gòu),包括以往被歸入特定極端性能應(yīng)用的部分,如基于向量的處理 (DSP、GPU) 和完全并行可編程的硬件 (FPGA)。問題在于,哪種架構(gòu)最適合哪項任務(wù)?

推出 ACAP:面向并行異構(gòu)計算開展軟硬件優(yōu)化

ACAP 的特點(diǎn)在于它結(jié)合了新一代標(biāo)量引擎、自適應(yīng)引擎和智能引擎。NoC 通過存儲器映射接口將它們相連,總帶寬為 1Tb/s+。除 NoC 之外,可編程邏輯(和集成型 RAM 塊)支持的大量存儲器帶寬支持可編程存儲器架構(gòu)針對單個計算任務(wù)進(jìn)行層級優(yōu)化(避免了其他基于高速緩存計算單元固有的高時延和時延不確定性)。

-

處理器

+關(guān)注

關(guān)注

68文章

20255瀏覽量

252325 -

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133435 -

異構(gòu)計算

+關(guān)注

關(guān)注

2文章

112瀏覽量

17182

發(fā)布評論請先 登錄

XC7Z020-2CLG484I 雙核異構(gòu)架構(gòu) 全能型 SoC

工程師必入!288 元解鎖賽靈思開發(fā)板

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

一文了解Mojo編程語言

【TEC100TAI-KIT】青翼凌云科技基于JFMQL100TAI的全國產(chǎn)化智能異構(gòu)計算平臺

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構(gòu)架構(gòu)下的智能邊緣計算標(biāo)桿

中科曙光構(gòu)建全國產(chǎn)化基因組學(xué)高性能計算平臺

FPGA 40周年!面向未來的FPGA,AMD聚焦邊緣智能與異構(gòu)計算

異構(gòu)計算解決方案(兼容不同硬件架構(gòu))

第三屆大會回顧第3期 | FFRT并發(fā)框架在OpenHarmony中的設(shè)計與實踐

如何釋放異構(gòu)計算的潛能?Imagination與Baya Systems的系統(tǒng)架構(gòu)實踐啟示

賽靈思推出首個完全支持軟件編程的異構(gòu)計算平臺

賽靈思推出首個完全支持軟件編程的異構(gòu)計算平臺

評論