我們在進行pcb布線時總會面臨一塊板上有兩種、三種地的情況,傻瓜式的做法當然是不管三七二十一,只要是地,就整塊敷銅了。這種對于低速板或者對干擾不敏感的板子來講還是沒問題的,否則可能導致板子就沒法正常工作了。當然若碰到一塊板子上有多種地時,即使板子沒什么要求,但從做事嚴謹認真的角度來講,咱們也還是有必要采用本文即將講到的方法去布線,以將整個系統最優化,使其性能發揮到極致!當然關于這些地的一些基礎概念、為什么要將它們分開,本文就不講了,不懂的同學自己查哈!

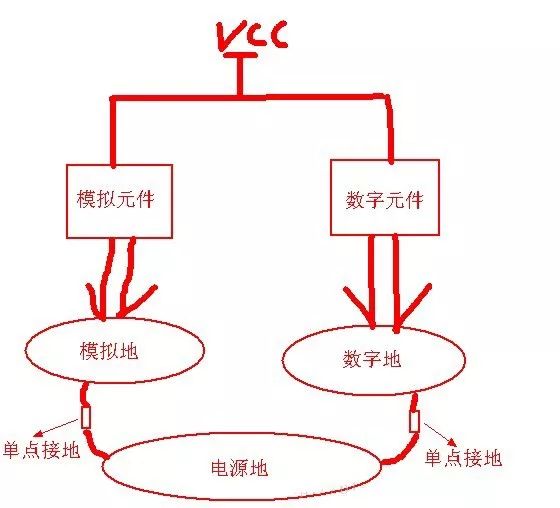

從這個圖可以看出:模擬地和數字地是完全分開的,最后都單點接到了電源地,這樣可以防止地信號的相互串擾而影響某些敏感元件,眾所周知數字元件對干擾的容忍度要強于模擬元件,而數字地上的噪聲一般比較大所以將它們的地分開就可以降低這種影響了。還有單點接地的位置應該盡量靠近板子電源地的入口(起始位置),這樣利用電流總是按最短路徑流回的原理可將干擾降到最小。

二、對于板子上只有數字地、電源地這種情況:

從此圖可以看出:只在電源地和數字地之間用一個0歐電阻或磁珠之類的單點接地就行了,同樣單點接地的位置應該盡量靠近板子電源地的入口(起始位置)。

三、展示一些第二種情況的pcb系統

1、地線分區

2、0歐電阻單點接地

3、板子正面圖

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4404文章

23878瀏覽量

424243 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44637

發布評論請先 登錄

相關推薦

熱點推薦

單片機硬件設計原則,抗干擾常用方法

、在單片機控制系統中,地線的種類有很多,有系統地、屏蔽地、邏輯地、模擬地等,地線是否布局合理,將決定電路板的抗干擾能力。在設計地線和接地點的時候,應該考慮以下問題:

邏輯地和模擬地要分開

發表于 12-09 06:30

提高單片機抗干擾能力的十個細節

;

電源監測:供電電壓出現異常時,給出報警指示信號或中斷請求信號;

硬件看門狗:當處理器遇到干擾或程序運行混亂產生“死鎖”時,對系統進行復位。

7、PCB電路合理布線

發表于 11-25 06:12

超強超全布線經驗教程大全

很好地掌握它,還需廣大電子工程設計人員去自

已體會, 才能得到其中的真諦。

1 電源、地線的處理

既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的

發表于 05-29 14:38

模擬地和數字地混合PCB布局探討

路徑過長,地環路過大。

圖2,模擬地和數字地分開,使用6層板單獨用一整層作為公共地,在ADC和DAC出將模擬地和數字地連接在公共地上然后公共地和電源

發表于 04-29 22:35

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

降低ESD風險的PCB布線與布局技巧。一、ESD路徑最短優先原則ESD是一種高頻、瞬態干擾,它往往會選擇阻抗最小的路徑泄放。因此,在布線時,必須確保ESD電流能快

芯片抗干擾能力概述

一、抗干擾能力定義 ? ? ? 芯片的抗干擾能力指其在電磁干擾、電源波動、信號噪聲等復雜環境中保持穩定運行的能力,確保數據準確傳輸與功能正常執行?。該能力是衡量芯片可靠性的核心指標,尤

開關電源的抗干擾問題

,它本身要有一定的抗干擾能力。這便是設備研制中所必須解決的兼容問題。2EMC試驗以往人們比較重視電磁發射的測試及抑制技術,以保護通訊、廣播系統或其它裝置不受干擾。近來,電磁敏感度的測試和對策技術已成為

發表于 04-07 15:59

濾波電感在電源抗干擾中的應用

,只有這樣才能得到最佳的抗干擾效果。最后本文指出由于開關電源的微型化,促進抗干擾電感器件向片式化和薄式化的發展。

關鍵詞:電磁干擾(EMI)電磁兼容(EMC)共模、差模

發表于 03-20 16:10

【PCB】PCB 電路板布線設計

,但要達到良好結果時,即使在一個簡單電路布線設計中存在小差異,都將導致無法達到最佳效果。本文中將探討模擬與數字布線間基本異同,有關旁路電容、電源

發表于 03-12 13:36

【PCB】四層電路板的PCB設計

布線 抗干擾

1 布局

所謂布局就是把電路圖中所有元器件都合理地安排在面積有限的PCB上。從信號的角度講,主要有數字信號電路 板、模擬信號

發表于 03-12 13:31

PCB Layout 工程師總結!25張圖講透PCB接地設計技巧!

PCB 接地 是 PCB Layout 工程師一直都會關注的問題,例如:如何在板上規劃有效地接地系統,是將模擬、數字、電源地等所有地單獨

發表于 03-06 15:13

怎樣PCB布線數字地和模擬地以及電源地抗干擾

怎樣PCB布線數字地和模擬地以及電源地抗干擾

評論