只需要簡單地用鼠標點擊幾下,就可定義、編輯和查看 PADS 原理圖環境中的網絡約束。為高速、布線和間距設置網絡和網絡類約束,為差分對設置特殊約束,或定義匹配長度組。高級工具提示會顯示如何操作。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

原理圖

+關注

關注

1353文章

6427瀏覽量

246312 -

網絡

+關注

關注

14文章

8265瀏覽量

94773 -

PADS

+關注

關注

82文章

821瀏覽量

111295

發布評論請先 登錄

相關推薦

熱點推薦

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定

輸入引腳時鐘約束_Xilinx FPGA編程技巧-常用時序約束詳解

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為:

輸入路徑(Input Path),使用輸入約束

寄存器到寄存器路徑

發表于 01-16 08:19

關于綜合保持時間約束不滿足的問題

兩個時鐘是沒有約束的異步時鐘

3、在 synthesis 中 打開 edit timing constraints 設置異步時鐘,如下圖:

4、再重新運行 synthesis 中的 report

發表于 10-24 07:42

如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

發表于 08-26 07:49

請問如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

發表于 08-20 06:23

技術資訊 I 圖文詳解約束管理器-差分對規則約束

本文要點你是否經常在Layout設計中抓瞎,拿著板子無從下手,拿著鼠標深夜狂按;DDR等長沒做好導致系統不穩定,PCIe沒設相位容差造成鏈路訓練失敗……這些都是血淚教訓,關鍵時刻需要靠約束管理器救命

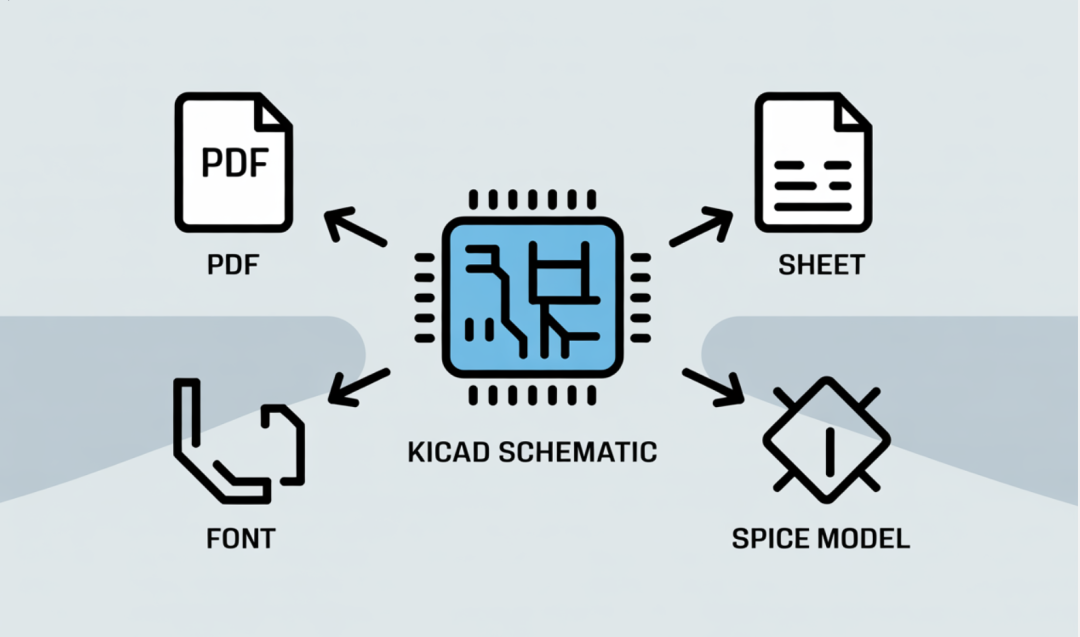

文件嵌入詳解(二):KiCad在原理圖中嵌入字體、圖框、數據手冊

尺寸)。 ” ? 在原理圖中嵌入外部文件 上文介紹了 如何在 PCB 封裝庫中嵌入 3D 模型 ,本文將介紹如何在原理圖中嵌入外部文件。 從 KiCad 9 開始,外部文件可以被嵌入到

PCB Layout 約束管理,助力優化設計

本文重點PCBlayout約束管理在設計中的重要性Layout約束有助避免一些設計問題設計中可以使用的不同約束在PCB設計規則和約束管理方面,許多設計師試圖采用“一刀切”的方法,認為同

如何在EZ-USB SX3配置實用程序中配置它的設置?

SX3 UVC(CYUSB3017)是否可以使用圖像傳感器接口以非整數幀速率(如 29.97fps)傳輸 UVC 視頻?

如何在 EZ-USB SX3 配置實用程序中配置它的設置?謝謝。

發表于 05-15 06:25

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時鐘的時序路徑,使用set_false_path約束

人臉識別指南:如何在樹莓派上安裝和設置 Dlib

學習如何在樹莓派上安裝Dlib并配置人臉識別功能,為您的AI項目奠定基礎。在樹莓派上安裝Dlib的詳細步驟要為樹莓派安裝Dlib并確保人臉識別項目順利運行,請按照以下詳細步驟操作。前置條件開始前,請

如何在原理圖中設置特殊約束

如何在原理圖中設置特殊約束

評論