大多數數字系統中,除了需要具有邏輯運算和算術運算功能的組合邏輯電路外,還需要具有儲存功能的電路,組合邏輯電路和儲存電路相結合可構成時序邏輯電路,鎖存器Lacth& 觸發器Flip-flop就是實現儲存功能的兩種邏輯單元電路。

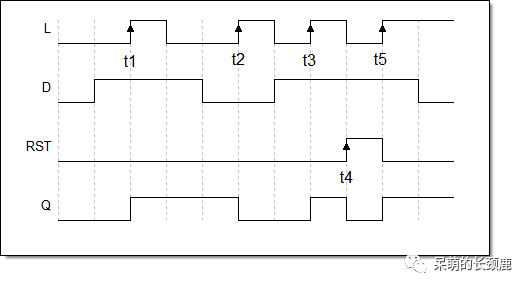

鎖存器是對電平敏感的電路,它們在一定電平作用下改變狀態。基本SR鎖存器由輸入信號電平直接控制其狀態,傳輸門控或邏輯門控鎖存器在使能電平作用下由輸入信號決定其狀態。在使能信號作用期間,門控鎖存器輸出跟隨輸入信號變化而變化。

觸發器則是對時鐘脈沖邊沿敏感的電路,根據不同的電路結構,它們在時鐘脈沖的上升沿或下降沿作用下改變狀態。目前流行的觸發器電路主要有主從、維持阻塞和利用傳輸延遲等幾種結構,它們的工作原理個不相同。

觸發器按邏輯功能分類有D觸發器、JK觸發器、T觸發器和SR觸發器。它們的功能可用特性表、特性方程和狀態圖來描述。觸發器的電路結構與邏輯功能沒有必然聯系。例如JK觸發器既有主從結構也有維持阻塞或利用傳輸延遲結構。每一種邏輯功能的觸發器都可以通過增加門電路和適當的外部連線轉換為其它功能的觸發器。

之所以能夠有記憶功能能夠存儲信息,最主要的就是它把輸出有反饋到了輸入,形成了反饋這樣它就能保持穩定。這使得Lacth & Flip-flop與組合邏輯電路的分析有了很大的不同,當然Latch & Flip-flop本來就只有這么幾種,記住就行。不需要自己去創新。

從最基本的用兩個或非門構成的SR鎖存器到在前面加上兩個與門和一個使能端E的邏輯門控SR鎖存器,這樣就可以實現多個鎖存器同步進行數據鎖存。但是SR鎖存器有個很不好的地方就是當SR同時為1的時候,它會出現不確定狀態,解決這個問題其實也很簡單在邏輯門SR鎖存器的S和R之間串上一個非門這樣S和R永遠都不會一樣,當然同時為0的狀態時有使能端E決定的,這個就是D鎖存器,當E為1時,輸出Q = D;當E為0時,輸出Q保持之前的狀態不變。再講了傳輸門門控D鎖存器,大致工作原理是當E為1的時候,放輸入信號進來,當E為0時,鎖存前一時刻(E=1時)的數據,后來就提出了在時序圖中的幾個基本概念:建立時間(Tsu)、保持時間(Th)、脈沖寬度(Tw)和傳輸延遲時間()。

觸發器的電路結構就不仔細分析了,關鍵是看看幾種觸發器的邏輯功能,觸發器在每次時鐘脈沖觸發沿到來之前的狀態稱為現態,而在此之后的狀態稱為次態。所謂觸發器的邏輯功能,是指次態與現態、輸入信號之間的邏輯關系。

D觸發器功能比較簡單,輸出Q的值直接等于輸入D就行。JK觸發器由特性表,特性方程或狀態圖都可以看出,當J=1,K=0時,觸發器的下一個狀態被置1;當J=0,K=1時,將被置0;當J=K=0時,觸發器狀態保持不變;當J=K=1時,觸發器翻轉。在所有類型的觸發器中JK觸發器具有最強的邏輯功能,它能執行置1、置0、保持和翻轉四種操作,并可以簡單的附加電路轉換為其他功能的觸發器,因此在數字電路中被廣泛應用。在某些場合,需要對計數功能進行控制,當控制信號T=1時,每來一個CP脈沖,它的狀態翻轉一次;而當T=0時,則不對CP信號做出響應而保持狀態不變。這就是T觸發器。其實T觸發器很簡單就是把JK觸發器的JK兩端接在了一起。僅有置位、復位功能的觸發器稱為SR觸發器,并且還有約束條件SR=0。

各種觸發器之間是可以很輕松的相互轉換的,要會靈活應用。

鎖存器能根據輸入端把結果自行保持;觸發器是指由時鐘邊沿觸發的存儲器單元;由敏感信號(電平,邊沿)控制的鎖存器就是觸發器;

寫電路時,產生鎖存器的原因:

if語句中,沒有寫else,默認保持原值,產生鎖存器,可能不是想要的結果;

case語句中,沒有寫完整default項,也容易產生鎖存器;

例子:

always@(a or b)

begin

if(a) q=b;

end

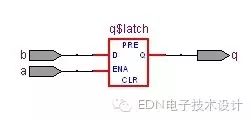

產生了鎖存器,如下

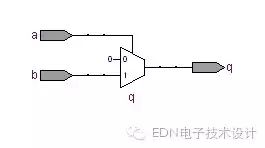

沒有鎖存器的情況

always@(a or b)

begin

if(a) q=b;

else q=0;

end

避免使用D鎖存器,盡量使用D觸發器

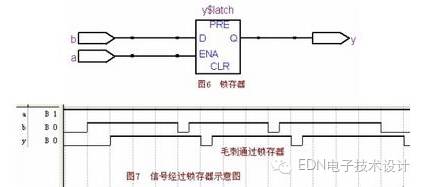

D鎖存器

moduletest_latch(y,a,b);

outputy;inputa;inputb;regy;

always@(aorb)begin

if(a==1’b1)

y=b;

endendmodule

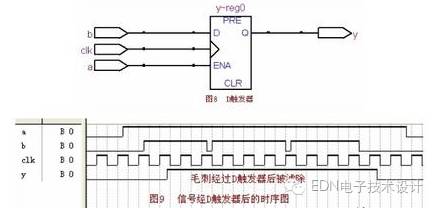

D觸發器

moduletest_d(y,clk,a,b);

outputy;inputclk;inputa;inputb;regy; always@(posedgeclk)begin if(a==1'b1)

y=b;

endendmodule

從圖8可知,例10對應的電路是D觸發器。信號a被綜合成D觸發器的使能端,只有在時鐘上沿到來且a為高時,b信號的值才能傳遞給a;只要在時鐘上升沿期間信號b是穩定,即使在其他時候b還有毛刺,經過D觸發器后數據是穩定的,毛刺被濾除。

-

電路

+關注

關注

173文章

6084瀏覽量

178764 -

鎖存器

+關注

關注

8文章

957瀏覽量

45431 -

觸發器

+關注

關注

14文章

2065瀏覽量

63516

原文標題:鎖存器Latch和觸發器Flip-flop有何區別?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

鎖存器Lacth & 觸發器Flip-flop就是實現儲存功能的兩種邏輯單元電路

鎖存器Lacth & 觸發器Flip-flop就是實現儲存功能的兩種邏輯單元電路

評論