RS觸發(fā)器的邏輯功能是什么

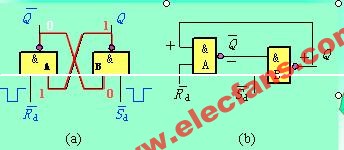

RS觸發(fā)器(RS flip-flop)是一種經(jīng)典的數(shù)字電路元件,用于存儲(chǔ)和控制數(shù)據(jù)。它由兩個(gè)交叉連接的反饋環(huán)路和兩個(gè)輸入端(R和S)組成。

RS觸發(fā)器的邏輯功能如下:

1. Set(設(shè)置)功能:當(dāng)輸入端S為高電平(1),輸入端R為低電平(0)時(shí),RS觸發(fā)器的輸出Q將被置為高電平(1),稱為Set狀態(tài)。無(wú)論之前RS觸發(fā)器的狀態(tài)如何,設(shè)置操作都會(huì)強(qiáng)制觸發(fā)器的輸出保持高電平,直到接收到復(fù)位(Reset)信號(hào)。

2. Reset(復(fù)位)功能:當(dāng)輸入端R為高電平(1),輸入端S為低電平(0)時(shí),RS觸發(fā)器的輸出Q將被置為低電平(0),稱為Reset狀態(tài)。無(wú)論之前RS觸發(fā)器的狀態(tài)如何,復(fù)位操作都會(huì)強(qiáng)制觸發(fā)器的輸出保持低電平,直到接收到設(shè)置信號(hào)。

3. Hold(保持)功能:當(dāng)輸入端S和R都為低電平(0)時(shí),RS觸發(fā)器的輸出Q將保持原來(lái)的狀態(tài),稱為Hold狀態(tài)。在這種狀態(tài)下,輸入端的變化不會(huì)引起輸出端的變化。

需要注意的是,當(dāng)輸入端的S和R同時(shí)為高電平(1)時(shí),即出現(xiàn)了禁止?fàn)顟B(tài)(Set和Reset同時(shí)有效),RS觸發(fā)器的輸出狀態(tài)將不確定,并稱為非法狀態(tài)。

RS觸發(fā)器是許多更復(fù)雜電路和存儲(chǔ)器元件的基礎(chǔ)。它可以用作時(shí)序電路、寄存器和計(jì)數(shù)器等應(yīng)用中的重要組成部分。

rs觸發(fā)器是什么沿觸發(fā)

RS觸發(fā)器在特定的輸入信號(hào)沿上觸發(fā)輸出變化的情況下被稱為沿觸發(fā)器。

沿觸發(fā)器是根據(jù)觸發(fā)器的輸入信號(hào)在上升沿(rising edge)或下降沿(falling edge)時(shí)觸發(fā)輸出變化的觸發(fā)器。根據(jù)觸發(fā)器的類型和功能,可以有不同類型的沿觸發(fā)器。

常見(jiàn)的沿觸發(fā)器包括:

1. 正沿觸發(fā)器(Positive Edge-Triggered):這是最常見(jiàn)的沿觸發(fā)器類型,當(dāng)觸發(fā)器的時(shí)鐘信號(hào)在上升沿時(shí)觸發(fā)輸出變化。在時(shí)鐘信號(hào)上升沿到來(lái)時(shí),輸入信號(hào)在之前的時(shí)鐘信號(hào)期間保持穩(wěn)定。常見(jiàn)的正沿觸發(fā)器包括D觸發(fā)器和JK觸發(fā)器。

2. 負(fù)沿觸發(fā)器(Negative Edge-Triggered):與正沿觸發(fā)器相反,當(dāng)觸發(fā)器的時(shí)鐘信號(hào)在下降沿時(shí)觸發(fā)輸出變化。在時(shí)鐘信號(hào)下降沿到來(lái)時(shí),輸入信號(hào)在之前的時(shí)鐘信號(hào)期間保持穩(wěn)定。負(fù)沿觸發(fā)器也可以用于特殊應(yīng)用需求。

沿觸發(fā)器在數(shù)字電路中非常重要,它們被廣泛應(yīng)用于時(shí)序電路、計(jì)數(shù)器、存儲(chǔ)器等設(shè)計(jì)中。通過(guò)沿觸發(fā)器,可以實(shí)現(xiàn)更復(fù)雜的計(jì)時(shí)和同步邏輯。

rs觸發(fā)器有幾個(gè)穩(wěn)定狀態(tài)的電路

RS觸發(fā)器有兩個(gè)穩(wěn)定狀態(tài)的電路。這兩個(gè)穩(wěn)定狀態(tài)分別是Set狀態(tài)和Reset狀態(tài)。

1. Set狀態(tài):當(dāng)輸入端S為高電平(1),輸入端R為低電平(0)時(shí),RS觸發(fā)器的輸出Q將被置為高電平(1)。同時(shí),輸出Q?(即Q的反相輸出)將保持低電平(0)。在Set狀態(tài)下,無(wú)論之前RS觸發(fā)器的狀態(tài)如何,設(shè)置操作都會(huì)強(qiáng)制觸發(fā)器的輸出保持高電平。

2. Reset狀態(tài):當(dāng)輸入端R為高電平(1),輸入端S為低電平(0)時(shí),RS觸發(fā)器的輸出Q將被置為低電平(0)。同時(shí),輸出Q?將保持高電平(1)。在Reset狀態(tài)下,無(wú)論之前RS觸發(fā)器的狀態(tài)如何,復(fù)位操作都會(huì)強(qiáng)制觸發(fā)器的輸出保持低電平。

需要注意的是,當(dāng)輸入端的S和R都為低電平(0)時(shí),RS觸發(fā)器將保持原來(lái)的狀態(tài),稱為Hold狀態(tài)。在Hold狀態(tài)下,輸入端的變化不會(huì)引起輸出端的變化。

在正常操作和設(shè)計(jì)中,應(yīng)該避免將輸入端的S和R同時(shí)設(shè)為高電平(1),以避免產(chǎn)生非法狀態(tài)。非法狀態(tài)下,RS觸發(fā)器的輸出將不確定。

編輯:黃飛

-

存儲(chǔ)器

+關(guān)注

關(guān)注

39文章

7738瀏覽量

171650 -

RS觸發(fā)器

+關(guān)注

關(guān)注

3文章

101瀏覽量

18912 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1651瀏覽量

83335 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2056瀏覽量

63395

發(fā)布評(píng)論請(qǐng)先 登錄

基本RS觸發(fā)器

鐘控同步RS觸發(fā)器教材

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

RS觸發(fā)器是什么?解讀rs觸發(fā)器的作用和數(shù)字電路中的rs觸發(fā)器的作用

RS觸發(fā)器的邏輯功能是什么 rs觸發(fā)器有幾個(gè)穩(wěn)定狀態(tài)的電路

RS觸發(fā)器的邏輯功能是什么 rs觸發(fā)器有幾個(gè)穩(wěn)定狀態(tài)的電路

評(píng)論