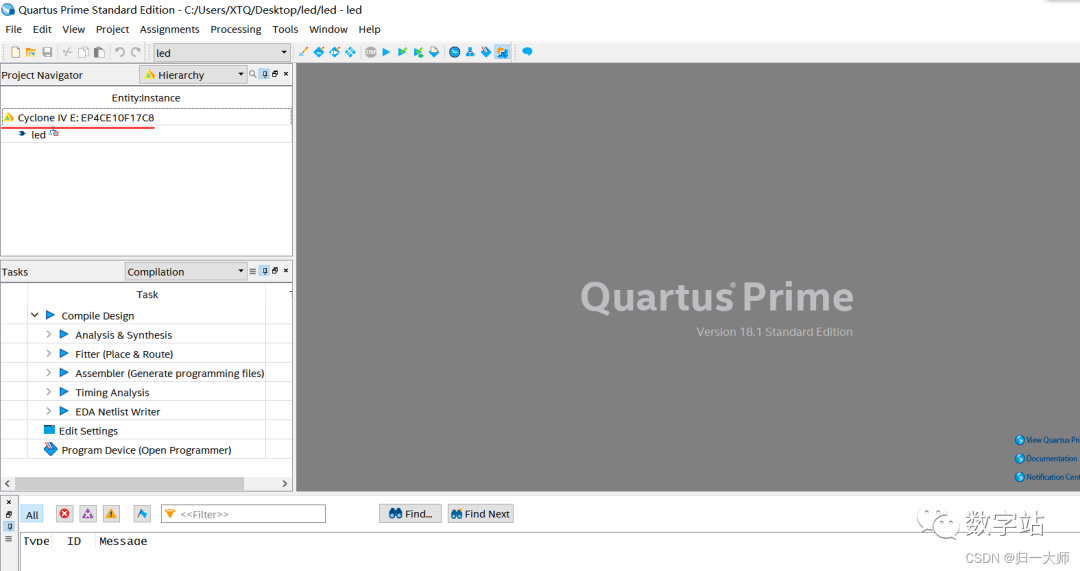

如何使用TimeQuest

用Altera的話來說,TimeQuest Timing Analyzer是一個功能強大的,ASIC-style的時序分析工具。采用工業標準--SDC(synopsys design contraints)--的約束、分析和報告方法來驗證你的設計是否滿足時序設計的要求。

TimeQuest的基本操作流程

做為altera FPGA開發流程中的一個組成部分,TimeQuest執行從驗證約束到時序仿真的所有工作。Altera推薦使用下面的流程來完成TimeQuest的操作。

1、建立項目并加入相關設計文件

不管做什么事情,都需要有一個目標或者說對象。我們用TimeQuest做時序分析,當然也需要一個對象,這個對象實際上就是我們的設計。所以首先是建立一個Quartus II的項目,并把所有需要的設計文件都加入到項目中去。需要注意的一點是,這里的設計文件,不僅僅包含邏輯設計相關的文件,也包含已經存在的時序約束文件,當然,需要以synopsys Design Constraints(.sdc)的格式存在的。關于 sdc文件,可以使用Quartus的向導來建立,在生成sdc文件后,你可以再在此sdc文件上進行自己的修改,如下圖所示,Assignments-》TimeQuest Timing Analyzer Wizard.。。

2、對項目進行預編譯(initial compilation)

項目建立以后,如果從來沒有對項目進行過編譯的話,就需要對項目進行預編譯。這里的預編譯是對應于全編譯(full compilation)來講的,我們可以理解為預編譯是對項目進行部分的編譯,而全編譯是對項目進行完整的編譯。做預編譯的目的是為了生成一個initial design database,然后我們可以根據這個database用Timequest采用交互的模式生成時序約束。實際上,對于小的設計,編譯時間并不是很長的話,完全可以不去區分預編譯和全編譯,需要編譯的時候,直接做全編譯就可以了,做全編譯的話,可以生成一個post-fit的database,完全可以給TimeQuest使用。

3、向設計中添加時序約束

在用TimeQuest做時序分析之前,必須要指定出對時序的要求,也就是我們通常所說的時序約束。這些約束包括時鐘,時序例外(timing exceptions)和輸入/輸出延時等。

默認情況下,Quartus II 軟件會給所有沒有被下約束的時鐘都設定為1GHz。沒有任何的時序例外,也就是說所有的timing path都按1T去check。所有的輸入/輸出的延遲都按0來計算。這顯然不符合絕大多數設計的時序要求,所以有必要根據設計的特性,添加必要的時序約束。

如上所述,時序約束主要包括三類:時鐘,時序例外和輸入/輸出延遲。其中時鐘和輸入/輸出延遲可以認為是在某種程度上增強時序設計的要求。而時序例外可以認為是在某種程度上降低時序設計的要求。比如說,僅僅設定一個時鐘的頻率為100MHz的話,這個時鐘域里所有timing path都需要能工作在100MHz下。這顯然是增強了時序設計的要求。可是如果在這個時鐘域下面,有部分timing path是不需要做1T的check的,那么就可以通過添加時序例外來避免對這些timing path做1T的check,即降低了時序設計的要求。

在用TimeQuest做時序分析時,如果非常熟悉設計的構架和對時序的要求,又比較熟悉sdc的相關命令,那么可以直接在sdc文件里輸入時序約束的命令。而通常情況下,可以利用TimeQuest GUI提供的設定時序約束的向導添加時序約束。不過要注意的是,用向導生成的時序約束,并不會被直接寫到sdc文件里,所以如果要保存這些時序約束,必須在TimeQuest用write sdc的命令來保存所生成的時序約束。

4. 執行完整的編譯

在設定好時序約束以后,就需要對整個設計進行完整的編譯。在編譯過程中,軟件會優化設計的邏輯、布局布線等來盡可能滿足所有的時序約束。

如果沒有添加時序約束,那么軟件在編譯的時候,會按照默認的時序約束對設計進行優化,對于絕大多數的設計,都會報出來時序的問題,但因為默認的時序約束與設計本身的要求在絕大多數情況下,都是不同的,所以這些時序的問題也并不是設計本身的問題,并沒有太多的參考價值,而且很多初學者也不會注意到這個問題。這樣就把設計中很多潛在的時序問題給隱藏起來了,最終帶來的可能就是系統運行的不穩定,甚至是完全不能運行。

5. 驗證時序

當完成編譯以后,我們就可以用TimeQuest來驗證時序了。在時序分析的過程中,TimeQuest會分析設計中所有的timing path,計算每一條timing path的延時,檢查每一條timing path是否滿足時序約束,最后按照positive slack或negative slack來報告時序分析的結果。其中negative slack就表示對應的timing path不滿足時序約束的要求(timing violation)。

如果遇到有不滿足時序要求的情況,則可以根據對應的時序報告分析設計,確定如何優化設計使之滿足時序約束。時序約束有任何變化的話,都需要重新編譯設計。這個反復的過程可以讓我們解決設計中的時序問題。

DAC7512控制器

DAC7512是一個具有三線串行接口的DAC。我們基于FPGA用Verilog語言實現了一個簡單的DAC7512的控制器。下面是控制器的結構圖

DAC7512控制器由三個模塊組成,PLL用來生成控制器所要的時鐘C0(25MHz)和C1(50MHz),其lock信號用來做為控制器的異步reset。da_data模塊生成要送往DAC7512的數據,其中DA_DATA為數據,DA_DATA_EN為數據有效信號,該模塊使用C0時鐘,整個屬于C0時鐘域。DAC7512模塊用于將DA_DATA轉換成符合DAC7512接口標準的串行數據并送給DAC7512,要用到C1(50MHz)和DA_SCLK(C1二分頻,25MHz)兩個時鐘。

DAC7512控制器一共有四個輸入輸出端口。CLK_IN為PLL的基準時鐘,為25MHz。DA_DIN,DA_SCLK和DA_SYNC為三線串口,都為輸出端口。由于C0,C1是由同一個PLL輸出的,DA_SCLK是由C1經二分頻得到的,三者之間是同步的,處于同一個clock group中。不過要注意一點的是,在串行總線上,DA_DIN是在DA_SCLK的下降沿有效的。把DA_DIN設計為C1時鐘域的信號,并控制其值只在DA_SCLK為高電平的時候發生變化。這樣可以把DA_DIN與DA_SCLK之間的時序要求轉換為DA_DIN在C1時鐘域的時序要求,具體的使用方法我們跟著視頻一起來學習一下。

-

TimeQuest

+關注

關注

0文章

11瀏覽量

11659

發布評論請先 登錄

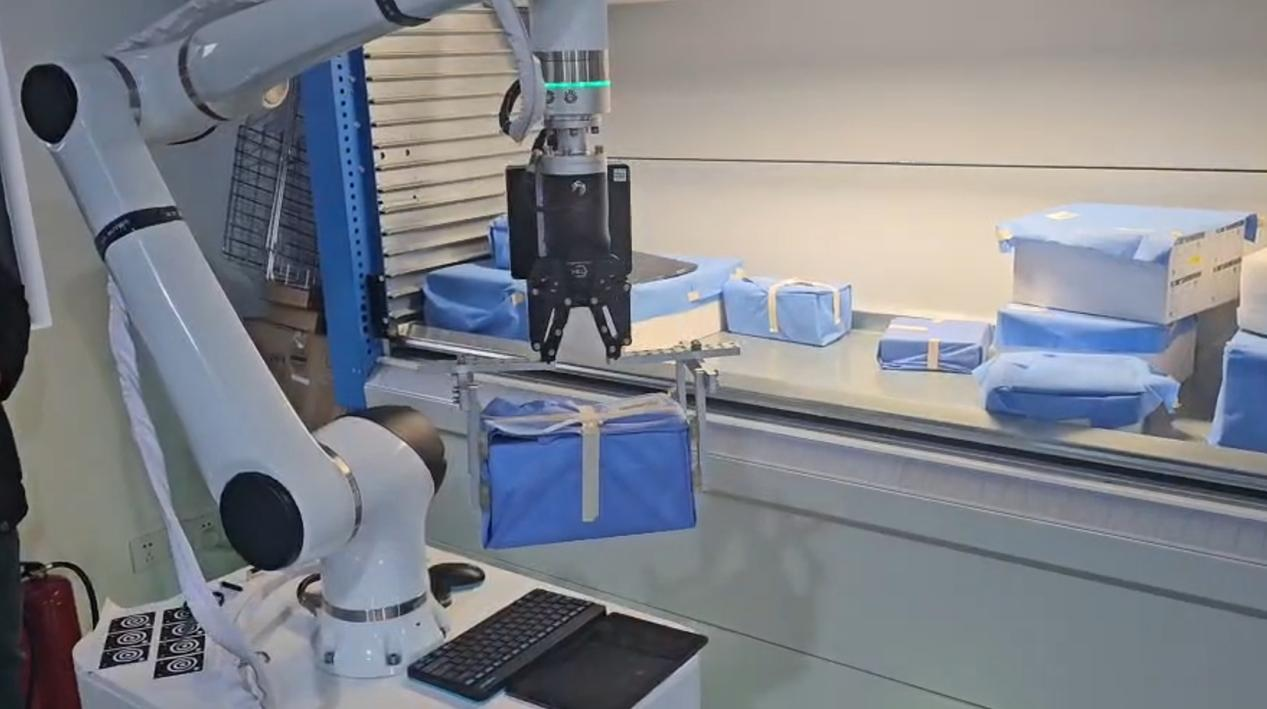

復合機器人可重構柔性裝配 賦能智能制造產線全面升級

探索CSD85312Q3E:雙20V N溝道NexFET?功率MOSFET的卓越性能

YAGEO國巨貼片電容采購需要了解哪些

成都華微與循態量子達成戰略合作

電解電容正負極接法的詳細介紹

【一周工控】阿普奇每周資訊(2.26-3.4)

【行業資訊】錨定新國標,阿普奇TER30R領航人形機器人“小腦”新時代

【具身智能】TER30R實現機器人“空翻級”性能

使用 Keil Studio for Visual Studio Code開發 STM32 設備

瑞可達復合銅排解決方案助力800V平臺高效配電

晶科能源與澳大利亞分銷商簽署10.5MW飛虎3系列高效光伏組件供貨協議

國產低功耗NFC芯片新選擇:DP1323EA兼容替換

如何使用TimeQuest

如何使用TimeQuest

評論