乘法器是眾多數字系統中的基本模塊。從原理上說它屬于組合邏輯范疇:但從工程實際設計上來說,它往往會利用時序邏輯設計的方法來實現,屬于時序邏輯的范疇。

通過這個實驗使大家能夠掌握利用FPGA/CPLD設計乘法器的思想,并且能夠將我們設計的乘法器應用到實際工程中。乘法器的設計方法有兩種:組合邏輯設計方法和時序邏輯設計方法。采用經合邏輯設計方法,電路事先將所有的乘積項全部計算出來,最后加法運算。采用時序邏輯設計方法,電路將部分已經得到的乘積結果右移,然后與乘積項相加并保存和值,反復迭代上述步驟直到計算出最終乘積。

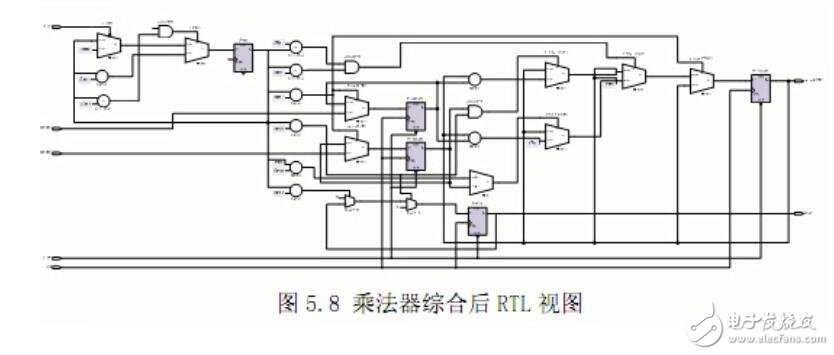

在該實驗中就是要利用時序邏輯設計方法來設計-一個16位乘法器,既然是利用時序邏輯設計方法那么就得利用時鐘信號控制乘法器運算。用時序邏輯設計方法與用組合邏輯設計方法比較,它有什么好處呢?利用時序邏輯設計方法可以使整體設計具備流水線結構的特征,能適用在各種實際工程設計中。

更多關于BJ-EPM240學習板之乘法器設計實驗請看視頻。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636330 -

乘法器

+關注

關注

9文章

221瀏覽量

38809

發布評論請先 登錄

相關推薦

熱點推薦

CDCF5801A:時鐘乘法器的卓越之選

CDCF5801A:時鐘乘法器的卓越之選 在電子工程師的日常設計工作中,時鐘信號的處理至關重要,而時鐘乘法器則是實現精確時鐘信號的關鍵組件。今天,我們就來深入探討德州儀器(Texas

深入剖析ADL5391:高性能模擬乘法器的卓越之選

深入剖析ADL5391:高性能模擬乘法器的卓越之選 在電子工程師的設計工具箱中,模擬乘法器是實現各種復雜信號處理功能的關鍵組件。今天,我們要深入探討一款來自Analog Devices的杰出

低成本模擬乘法器AD633:特性、應用與設計指南

低成本模擬乘法器AD633:特性、應用與設計指南 在電子工程師的日常設計工作中,模擬乘法器是一個常用的基礎器件。今天,我們就來深入探討一下ADI公司的低成本模擬乘法器AD633,從它的特性、參數

深入剖析AD632:高性能四象限乘法器/除法器

深入剖析AD632:高性能四象限乘法器/除法器 在電子工程師的日常設計中,高性能的模擬信號處理芯片是不可或缺的工具。今天,我們就來詳細探討一下Analog Devices公司的AD632——一款內部

AD532:高性能單芯片乘法器/除法器的卓越之選

AD532:高性能單芯片乘法器/除法器的卓越之選 在電子設計領域,乘法器和除法器是實現復雜運算和信號處理的關鍵組件。而AD532作為一款預微

E203在基于wallace樹+booth編碼的乘法器優化后的跑分結果

優化思路

E203為了實現低功耗的要求,乘法器為基于booth編碼和移位加法器結合的思路,優點是只需要一個加法器,而且該加法器還和除法器復用

發表于 10-27 07:54

E203V2長周期乘法器核心booth算法解讀

E203V2乘法器所在模塊為e203_exu_alu_muldiv.v,其中包含乘法和除法兩大塊,這里僅對乘法模塊進行解讀。

乘法模塊首先進行booth編碼,其目的為方便兩個有符號數相

發表于 10-24 09:33

Verilog實現使用Booth編碼和Wallace樹的定點補碼乘法器原理

周期乘法器。乘法器,對于無符號乘法進行一位符號擴展后統一當作有符號數進行運算,因此需要17個迭代周期。為了改良乘法器性能,我們可以使用Booth編碼和Wallace樹的定點補碼

發表于 10-23 08:01

改進wallance樹乘法器優化方法

首先,根據之前分享的乘法器的優缺點,我們針對17周期的乘法器進行優化,為乘法設計的專用數據通路,為了保持e203的低功耗、低面積的優點、我們仍采用基4booth算法進行部分積生成,而對于原有的17

發表于 10-23 06:37

關于E203內核高性能乘法器優化(一)

一、簡介

對于cpu各類測試程序,設計一個高性能的硬件乘法器模塊無疑是提分最快的法案,本文將從乘法算法開始,到rtl設計進行詳細的解釋說明,并附帶一部分源碼。

二、乘法算法

乘法器

發表于 10-23 06:09

蜂鳥乘法器設計分享

蜂鳥的乘法器主體設計在ALU模塊的子單元MDV模塊中,MDV模塊包括乘除法器邏輯設計,它只包含運算控制,但并不包含具體運算,它們都需要將部分積或者部分余數傳入數據通路(dpath模塊)中,從而實現

發表于 10-22 08:21

蜂鳥E203乘法器改進

蜂鳥E203為了節約資源,乘法運算采用循環移位方式計算最終結果,這樣的乘法器需要經過較多時鐘周期來處理數據,導致處理數據效率較低。為了提高計算效率,這里分享一種基于流水線思想的乘法器,即采用多個

發表于 10-22 07:28

蜂鳥E203內核乘法器的優化

乘法器的優化實現一般從兩個方面入手。第一是減少生成的部分積數量,另外就是減少部分積累加的延時。

在開源的E203源碼中,32*32乘法器是利用radix-4 booth編碼產生部分積,每個周期做一次

發表于 10-22 06:11

優化boot4乘法器方法

優化電路設計:在電路設計中,可以采用更快速的邏輯單元和存儲器元件,優化關鍵路徑和信號傳輸路線,從而降低延遲,縮短乘法器的運算周期。

固定位寬:Boot4乘法器可以處理不同位寬的數據,但是處理不同位寬

發表于 10-21 12:13

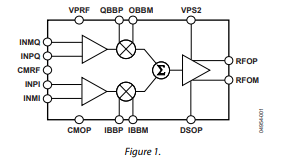

ADL5390 RF矢量乘法器技術手冊

ADL5390矢量乘法器由一對匹配的寬帶可變增益放大器組成,二者輸出相加,每個放大器具有單獨的線性幅度增益控制。如果兩個輸入RF信號正交,則可以將該矢量乘法器配置為矢量調制器,或將增益控制引腳用作

BJ-EPM240學習板之乘法器設計實驗

BJ-EPM240學習板之乘法器設計實驗

評論