CDCF5801A:時鐘乘法器的卓越之選

在電子工程師的日常設計工作中,時鐘信號的處理至關重要,而時鐘乘法器則是實現精確時鐘信號的關鍵組件。今天,我們就來深入探討德州儀器(Texas Instruments)推出的CDCF5801A時鐘乘法器,看看它在時鐘處理方面的獨特魅力。

文件下載:cdcf5801a.pdf

一、產品概述

CDCF5801A是一款具備延遲控制和相位對齊功能的時鐘乘法器,它能將參考時鐘(REFCLK)信號進行乘法運算,同時還能對CLKOUT/CLKOUTB信號進行精確的延遲或提前操作,步長僅為1.3 mUI。這種獨特的功能使得它在眾多應用場景中都能發揮出色的性能。

二、產品特性

1. 低抖動時鐘乘法

CDCF5801A支持×1、×2、×4、×8的時鐘乘法,能夠在輸入頻率范圍為12.5 MHz至240 MHz的情況下,輸出25 MHz至280 MHz的穩定時鐘信號,并且具有低抖動特性,確保了時鐘信號的高質量。

2. 故障安全上電初始化

該器件具備故障安全上電初始化狀態機,能在各種上電條件下保證正常運行,為系統的穩定性提供了有力保障。

3. 可編程雙向延遲

通過DLYCTRL和LEADLAG引腳,CDCF5801A可以實現可編程的雙向延遲,延遲步長為1.3 mUI,這使得它能夠靈活地進行相位對齊,滿足不同應用的需求。

4. 多種輸出驅動能力

它支持單端和差分輸出,輸出能夠驅動LVPECL、LVDS和LVTTL等不同類型的負載,具有很強的通用性。

5. 低功耗設計

CDCF5801A采用了三種功率操作模式,能夠有效降低功耗,在280 MHz/3.3 V的工作條件下,功耗小于190 mW。

6. 無需外部組件

PLL部分無需外部組件,簡化了設計,降低了成本和電路板空間。

7. 擴頻時鐘跟蹤能力

具備擴頻時鐘跟蹤能力(SSC),可以有效降低電磁干擾(EMI)。

三、引腳功能

CDCF5801A共有24個引腳,每個引腳都有其特定的功能:

1. 時鐘輸出引腳

CLKOUT和CLKOUTB是低噪聲CMOS輸出引腳,用于輸出時鐘信號。

2. 延遲控制引腳

DLYCTRL引腳的每個上升沿可以使CLKOUT/CLKOUTB信號延遲或提前1/768個CLKOUT/CLKOUTB周期(1.3 mUI)。

3. 電源和地引腳

包括VDDREF、VDDP、VDDO、VDDPD、VDDPA等電源引腳,以及GND、GNDO、GNDP、GNDPA等地引腳,為器件提供穩定的電源和接地。

4. 控制引腳

LEADLAG引腳用于控制輸出時鐘相對于REFCLK的延遲或提前;MULT[0:1]和P[0:2]引腳用于選擇頻率乘法和除法比率;P0、STOPB和PWRDN引腳用于選擇不同的功率模式。

四、頻率設置

通過設置MULT[0:1]和P[1:2]引腳,可以選擇不同的頻率乘法和除法比率,從而實現從25 MHz到280 MHz的輸出頻率。具體的設置可以參考文檔中的表1,需要注意的是,在輸入頻率范圍有重疊的情況下,應選擇表格中更靠近頂部的輸入頻率范圍,以確保設備的最佳運行。

五、功率模式

CDCF5801A提供了多種功率模式,通過PWRDNB和STOPB引腳進行選擇:

1. 掉電模式

當PWRDNB為低電平時,器件進入掉電模式,CLKOUT/CLKOUTB輸出低電平。

2. 時鐘停止模式

當STOPB為低電平時,輸出被禁用,PLL和PA仍在運行,CLKOUT和CLKOUTB輸出一個直流值。

3. 正常模式

當PWRDNB和STOPB都為高電平時,器件正常工作,輸出頻率根據MULT[0:1]和P[0:2]的設置而定。

六、應用場景

1. 視頻圖形和游戲產品

在這些應用中,需要精確的時鐘信號來確保圖像和游戲的流暢運行,CDCF5801A的低抖動特性和相位對齊功能能夠滿足這些需求。

2. 數據通信和電信

在數據傳輸和通信系統中,穩定的時鐘信號是保證數據準確傳輸的關鍵,CDCF5801A可以提供高質量的時鐘信號,提高系統的可靠性。

3. FPGA噪聲消除

FPGA在工作過程中會產生噪聲,CDCF5801A可以通過相位對齊和延遲控制,有效消除FPGA產生的噪聲,提高系統的性能。

七、使用注意事項

1. VDDREF的選擇

VDDREF可以設置在1.2 V至VDD之間的任何值,它直接影響輸入的觸發電壓。在使用小信號擺幅驅動輸入時,如PECL,建議將VDDREF直接連接到VDD,并對REFCLK輸入進行交流耦合和重新偏置。

2. 反饋回路

如果在CDCF5801A的CLKOUT到DLYCTRL反饋回路中使用了有源元件(如微控制器、ASIC、DSP等),請參考應用報告SCAA075。

八、總結

CDCF5801A作為一款功能強大的時鐘乘法器,具有低抖動、可編程延遲、多種輸出驅動能力和低功耗等優點,適用于多種應用場景。在設計過程中,工程師們可以根據具體需求合理設置引腳和參數,充分發揮其性能優勢。你在實際使用中是否遇到過類似的時鐘乘法器?它們的表現如何呢?歡迎在評論區分享你的經驗和見解。

-

低抖動

+關注

關注

0文章

62瀏覽量

6070

發布評論請先 登錄

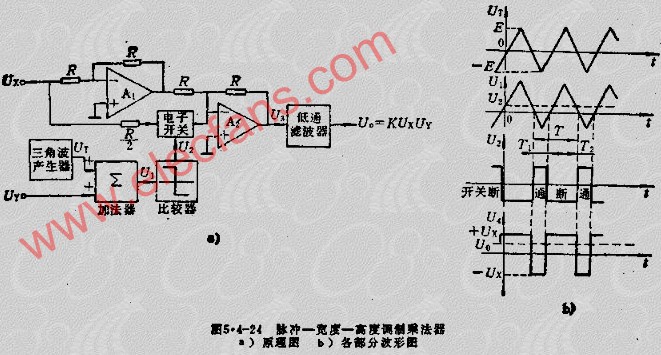

脈沖-寬度-高度調制乘法器

進位保留Barrett模乘法器設計

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

CDCF5801A具有延遲控制和相位對準的時鐘乘法器數據表

?CDCF5801A時鐘乘法器技術文檔總結

CDCF5801A:時鐘乘法器的卓越之選

CDCF5801A:時鐘乘法器的卓越之選

評論