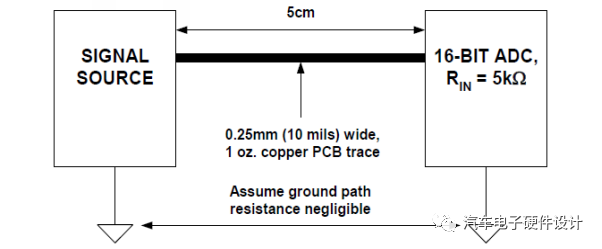

歐姆定律說明由于PCB導(dǎo)體上的壓降會導(dǎo)致>1的

LSB

16-bit的ADC的輸入阻抗為5Kohm

PCB的走線長5cm,寬0.25mm,厚度為1OZ

接收端的實(shí)際電壓是0.1/5k(~0.0019%)的增益系數(shù)

大于 1LSB(0.0015% for 16bits).

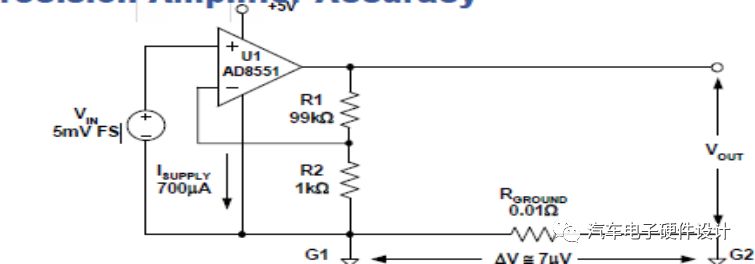

小型共地回路會降低放大器精度

一個5mv低電壓信號Vin,需要的增益為100

考慮到DC精度,使用AD8551

回顧下AD8551的規(guī)格

Low offset voltage: 1 μV, offset drift: 0.005μV/°C

在終端,信號Vout的參考地是G2

因?yàn)镚1與G2之間有一個約700uA的Isupply電流,所以這兩點(diǎn)會由0.01ohm的阻抗引起7uv的誤差

大約是7倍!

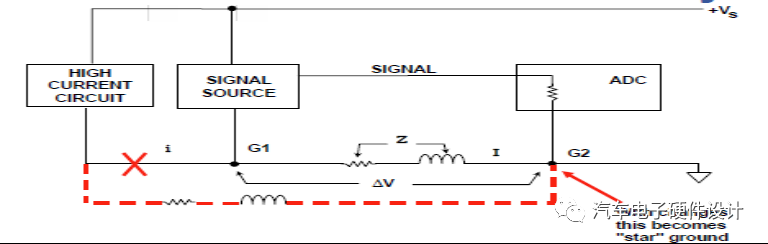

一個更加真實(shí)的地系統(tǒng)模型

任何電流流過地都會引起誤差

ΔV = (I + i) *Z

-

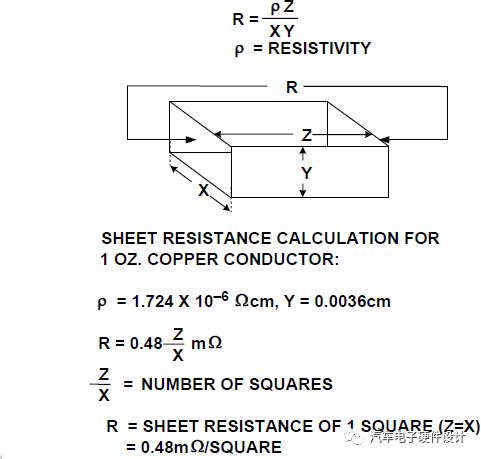

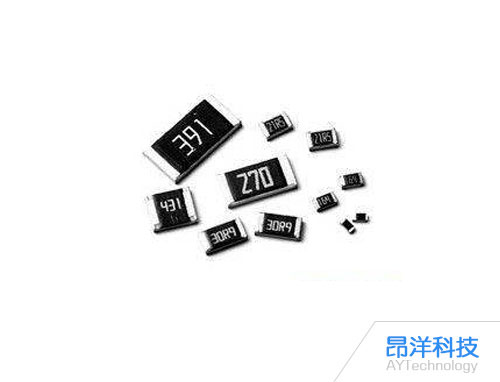

電阻

+關(guān)注

關(guān)注

88文章

5779瀏覽量

179504 -

表面電阻率

+關(guān)注

關(guān)注

1文章

5瀏覽量

6597

原文標(biāo)題:計算表面電阻

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

體積表面電阻率測試儀的關(guān)鍵性能指標(biāo):精度、量程與穩(wěn)定性

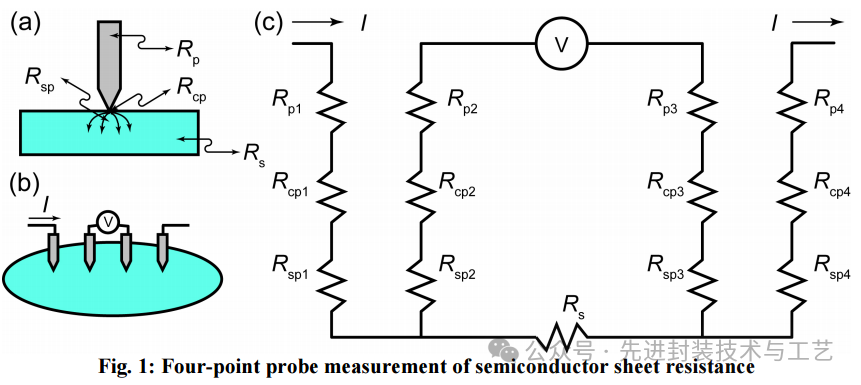

四探針法測量半導(dǎo)體薄層電阻的原理解析

真不敢信,PCB板上就挪動了一個電阻,DDR3竟神奇變好了

體積表面電阻率測試儀中電磁干擾的識別與消除實(shí)戰(zhàn)

體積/表面電阻率:探索物質(zhì)電學(xué)特性的奧秘(下)

體積/表面電阻率:探索物質(zhì)電學(xué)特性的奧秘(上)

四探針法 | 測量射頻(RF)技術(shù)制備的SnO2:F薄膜的表面電阻

揭秘高頻PCB設(shè)計:體積表面電阻率測試儀如何確保信號完整性

吉時利6517A靜電計/高電阻計Keithley6517B深圳中瑞儀科

PCB表面處理工藝詳解

如何避免體積表面電阻率測試儀中的“假高阻”現(xiàn)象?

電阻上的數(shù)字如何表示電阻大小?

半導(dǎo)體硅表面氧化處理:必要性、原理與應(yīng)用

在橡膠體積表面電阻率測試過程中,電磁干擾對測試結(jié)果的影響,如何有效屏蔽

PCB導(dǎo)體上的表面電阻應(yīng)該如何計算呢?

PCB導(dǎo)體上的表面電阻應(yīng)該如何計算呢?

評論