本課程主要介紹如何校準DAC從而幫助消除某些固有誤差、代碼對代碼的干擾以及降低干擾影響的方法、數字饋通及如何將其停止、過沖及如何避免過沖的方法等。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ti

+關注

關注

114文章

8068瀏覽量

219200 -

dac

+關注

關注

44文章

2713瀏覽量

197066 -

代碼

+關注

關注

30文章

4967瀏覽量

73954

發布評論請先 登錄

相關推薦

熱點推薦

PID調參實用方法

) 周圍抖動

在講了PI和PD系統的調節方式后,下面分享一下PID系統的調節方式,首先我們先按照PI系統進行調節,先調P在調I,讓系統有一定的過沖后達到穩定.

在出現了上面的 PI 波形之后,下面就開始調節D,慢慢增加D,將過

發表于 11-28 07:17

如何巧妙甚至避免單片機的干擾問題

注意的是:該方法適合有上拉電阻的單片機電路。

1、精選上拉電阻值

在高干擾環境下,選擇較小的上拉電阻(如1KΩ),以此減少干擾信號在電阻上產生的電壓。

若是家用設計,采用10-20KΩ的上拉電阻,以此

發表于 11-26 06:48

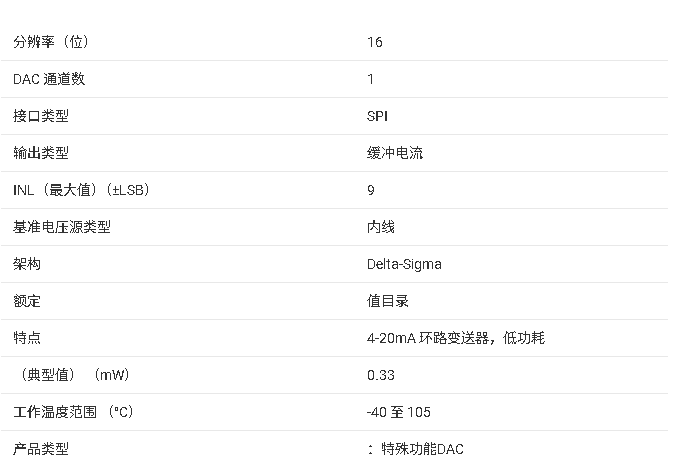

DAC161S997 16位精密DAC技術手冊

該DAC161S997是一款非常低功耗的 16 位 ΣΔ 數模轉換器 (DAC),用于通過行業標準的 4-20 mA 電流環路傳輸模擬輸出電流。 這 DAC161S997有一個簡單的4

如何避免傳感器故障報警閾值調整不當的問題?

避免傳感器故障報警閾值調整不當,需建立 “ 事前明確依據 + 事中規范操作 + 事后持續驗證 ” 的閉環管理流程,核心是讓閾值調整 “有數據支撐、有測試驗證、有風險管控”,而非依賴主觀經驗。以下

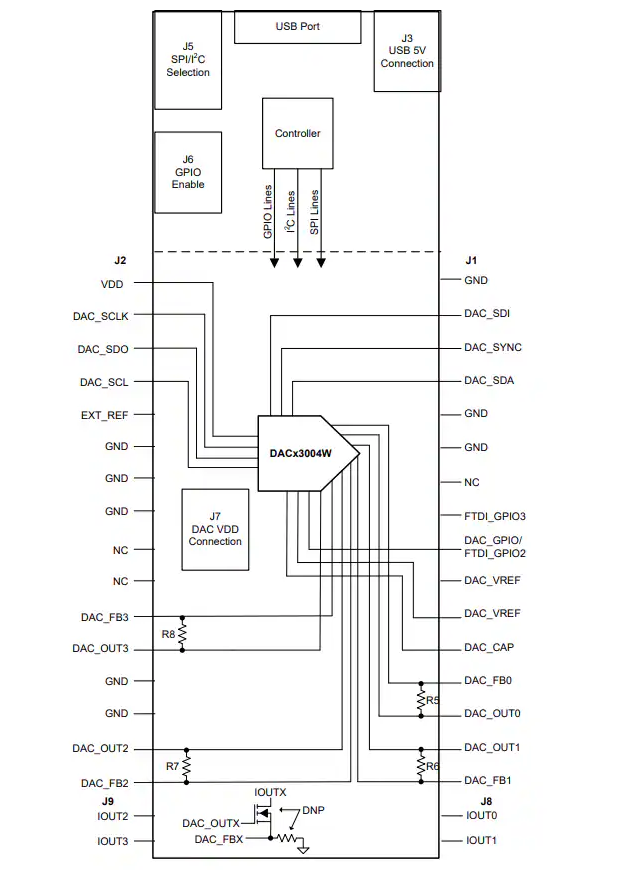

DAC63004WCSP-EVM評估模塊技術解析與應用指南

63004是商用超低功耗、緩沖電壓、電流輸出數模轉換器 (DAC),有各種配置可供選擇。此外,還有一個可選電路,用于評估DAC63004W或DAC53004W作為可變電流源,輸出電流高

芯對話|CBM108S085破局多通道DAC“同步+精度+低功耗”困局

,需要實現8通道的納秒級同步輸出,分立DAC不僅占用大量PCB面積,還難以有效避免通道間的延遲誤差;另一方面,便攜式設備面臨著‘低功耗’與‘高精度’之間的平衡挑戰

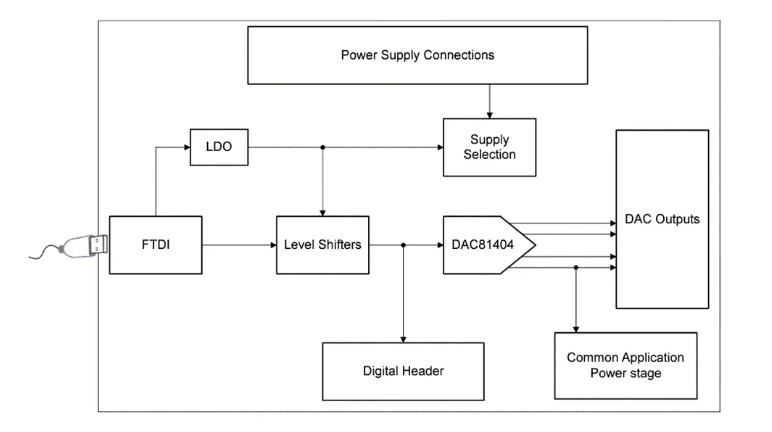

Texas Instruments DAC81404EVM評估模塊數據手冊

Texas Instruments DAC81404EVM評估模塊設計用于評估DAC81404 DAC。DAC81404是引腳兼容系列的四通道、緩沖高壓輸出數模轉換器(

如何減小DAC電路的耦合影響?

設計優化獨立電源軌為DAC的模擬部分(如參考電壓、輸出緩沖器)和數字部分(如時鐘、控制邏輯)提供獨立的低噪聲LDO(低壓差線性穩壓器)或線性電源,避免數字開關噪聲通過電源耦合到模擬信號。示例

發表于 07-29 09:39

MCSDK 6.2.1位置模式過沖的原因?如何解決?

,運行平穩

但是在位置控制時,反復測試發現在Ramp運行時間為3.3s-3.7s時,電機可以在任意目標位置下正常停止不會過沖,只要計算出的最大速度不超過電機最大速度就都是正常的

只要Ramp運行時間小于

發表于 07-11 08:17

無刷直流電機反電勢過零檢測新方法

的危險。同時,根據控制信號占空比切換低速區與高速區反電勢采樣方式,能有效改善在低速區時反電勢過零檢測效果。實驗結果表明,提出的反電勢過零檢測新方法能保證電機工作于更寬的轉速范圍內。

純

發表于 06-26 13:50

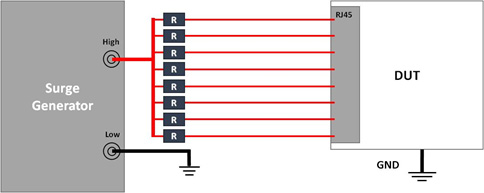

“System Level EOS Testing Method”可以翻譯為: “系統級電性過應力測試方法”

“System Level EOS Testing Method”可以翻譯為:

“系統級電性過應力測試方法”

DAC 與 ADC:數字與模擬的往復之旅

吻合。

該 DAC 架構的主要缺陷在于所需電阻值很快會變得不切實際。為避免靜態電流過大,最高有效位(MSB)對應的電阻值不能過低(1 kΩ是合理的起始值)。但對于16位DAC而言,這意

發表于 03-25 13:42

過壓保護控制集成電路CN36B

關斷和緩慢導通外部P溝道MOSFET。快速關斷可以將負載與過沖電壓快速隔離;緩慢導通可以控制負載的浪涌電流,實現了對負載的有效保護。CN36B采用3管腳SOT23封裝。特點:?輸入電壓高達32V?

發表于 03-24 13:56

過壓保護控制集成電路CN36A

關斷和緩慢導通外部P溝道MOSFET。快速關斷可以將負載與過沖電壓快速隔離;緩慢導通可以控制負載的浪涌電流,實現了對負載的有效保護。CN36A采用3管腳SOT23封裝。應用:?小家電?便攜式裝置?醫療

發表于 03-21 10:03

如何使用FPGA驅動并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時的注意事項

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行

避免DAC過沖的有效方法有哪些

避免DAC過沖的有效方法有哪些

評論