Vinay Singh,高級產品經理,使用Zynq-7000 All Programmable SoC將實時計算機視覺算法應用到設計中。OpenCV簡單的說就是一個開源的計算機視覺庫,個人感覺功能強大,使用方便,算是圖像處理和計算機視覺開發方面的神器了。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133435 -

soc

+關注

關注

40文章

4576瀏覽量

229149 -

計算機

+關注

關注

19文章

7807瀏覽量

93203

發布評論請先 登錄

相關推薦

熱點推薦

HLS設計中的BRAM使用優勢

高層次綜合(HLS)是一種將高級編程語言(如C、C++或SystemC)轉換為硬件描述語言(HDL)的設計方法。在FPGA設計中,設計者可以靈活地利用FPGA內部的資源,如塊RAM(BRAM)。雖然

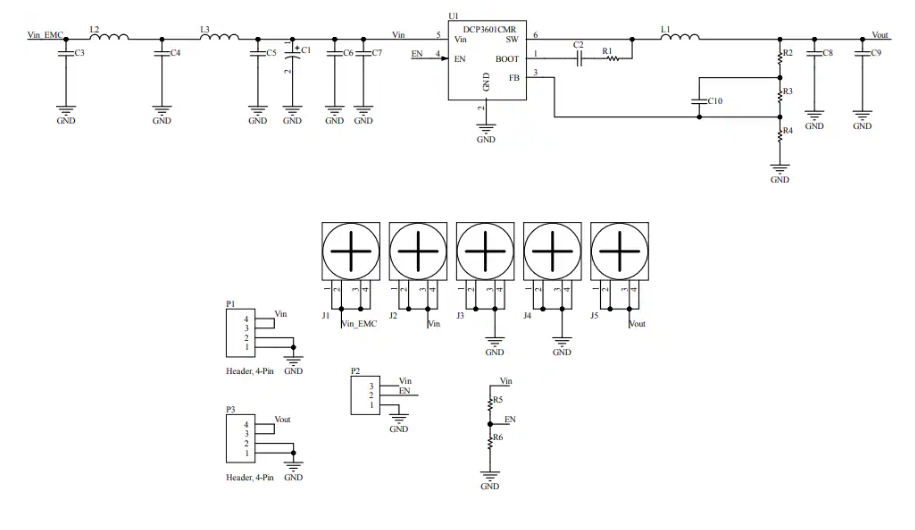

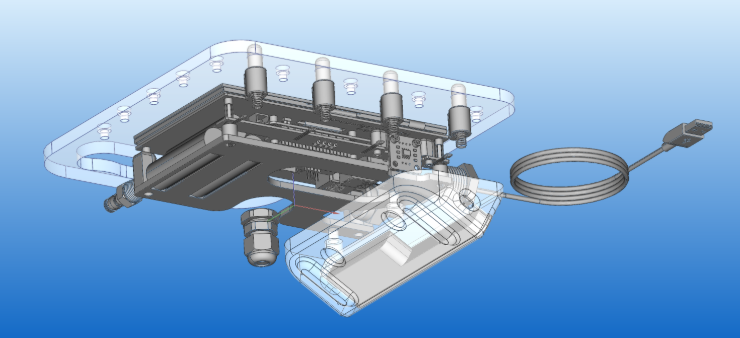

STEVAL-3601CV1評估板技術解析與應用指南

STMicroelectronics STEVAL-3601CV1評估板采用DCP3601CMR同步降壓轉換器,可增強峰值電流控制和高級設計電路。該板演示智能轉換器設計,可在3.3V至36V輸入

半導體器件CV特性/CV特性測試的定義、測試分析和應用場景

一、基本概念 CV特性 (電容-電壓特性)是指半導體器件在不同偏置電壓下表現出的電容變化規律,主要用于分析器件的介電特性、載流子分布和界面狀態。該特性是評估功率器件性能的核心指標之一。 CV特性測試

如何在Unified IDE中創建視覺庫HLS組件

最近我們分享了開發者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統 IDE)和開發者分享|AMD Vitis HLS 系列 2:AMD

使用AMD Vitis Unified IDE創建HLS組件

這篇文章在開發者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統 IDE) 的基礎上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統版本的 Vitis HLS。

如何使用AMD Vitis HLS創建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創建一個 HLS IP,通過 AXI4 接口從存儲器讀取數據、執行簡單的數學運算,然后將數據寫回存儲器。接著會在 AMD Vivado Design Suite 設計中使用此

半導體器件CV測量技術解析

前言:研究器件特性和器件建模都離不開精確的電容電壓(CV)測量。精確的CV模型在仿真器件的開關特性,延遲特性等方面尤為重要。目前,在寬禁帶器件(GaN/SiC)、納米器件、有機器件、MEMS等下

基于LockAI視覺識別模塊:C++使用圖像的統計信息

為 BGR 圖像

BGR ? HLS

cv::COLOR_BGR2HLS

將 BGR 圖像轉換為 HLS 圖像

cv::COLOR_

發表于 05-08 10:31

Vivado HLS設計流程

為了盡快把新產品推向市場,數字系統的設計者需要考慮如何加速設計開發的周期。設計加速主要可以從“設計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx 推出的 Vivado HLS 工具可以

Open Echo:一個開源的聲納項目

“ ?這是一個還在迭代中的項目。開源的回聲測深儀/水深測量儀/聲吶系統,適用于水文測繪及科研用途。基于Arduino平臺開發并具備良好兼容性? ” ? Open Echo 概覽 作為持續迭代

直流電源CV/CC模式實現原理

直流電源實現恒壓(CV)和恒流(CC)模式輸出的核心在于 雙閉環反饋控制 ,通過電壓和電流的實時監測與動態調整,確保在負載變化時自動切換模式。以下是具體實現原理和步驟: 1、基本工作原理 恒壓模式

HLS Open CV演示

HLS Open CV演示

評論