1、高斯濾波器的實現方式

方法1:與高斯核直接進行卷積實現,這樣使用的資源和乘法器 加法器都會很多。例如3*3窗口的濾波核進行卷積運算,一共需要進行9次乘法和8次加法。

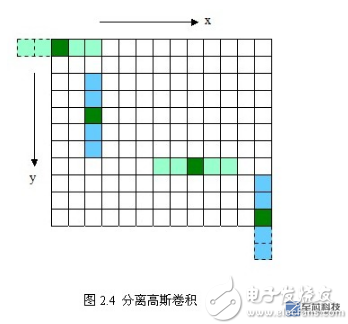

方法2:采用兩個一維的高斯濾波進行兩次濾波,即先對行進行一維濾波,然后再對列進行一維濾波,這樣計算簡單,降低了復雜度。

比較兩種方法,采用第二種實現方法。

2、行列分離計算方法

采用下圖的計算方法,其中對邊界的處理填0處理。

3、實現結果

always

begin

#10 clk = ~clk; //100Mhz

end

時間:5201520000ps=5.2ms

always

begin

#5 clk = ~clk; //200Mhz

end

時間:2600780000ps=2.6ms

4、與仿真比較

如下圖

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636239

發布評論請先 登錄

相關推薦

熱點推薦

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRA

25年11月上海FPGA算法實現與應用技術高級研修分享

。

第十章: LTE20M DFE雙載IP的FPGA設計:基于兩個LTE20M載波信號上變頻過程完成FPGA設計,實現信號產生、存儲、時序分配、低通濾波、半帶

發表于 10-11 11:55

數據濾波算法的具體實現步驟是怎樣的?

? 數據濾波算法在電能質量在線監測裝置中的具體實現,需圍繞 “ 數據采集→預處理→算法執行→參數適配→效果驗證→結果輸出 ” 的全流程展開,核心是結合裝置硬件特性(采樣率、ADC 精度)和干擾類型

基于Matlab與FPGA的雙邊濾波算法實現

前面發過中值、均值、高斯濾波的文章,這些只考慮了位置,并沒有考慮相似度。那么雙邊濾波來了,既考慮了位置,有考慮了相似度,對邊緣的保持比前幾個好很多,當然實現上也是復雜很多。本文將從原理

基于FPGA的壓縮算法加速實現

本設計中,計劃實現對文件的壓縮及解壓,同時優化壓縮中所涉及的信號處理和計算密集型功能,實現對其的加速處理。本設計的最終目標是證明在充分并行化的硬件體系結構 FPGA 上實現該算法時,可

粗糙度的濾波值是怎么設置的?

微觀不平度的信息。本文將詳細探討粗糙度濾波值的設置方法與依據。 濾波原理與類型 表面輪廓包含了形狀誤差、波紋度和粗糙度等不同尺度的幾何特征,濾波的本質是通過數學算法對輪廓數據進行頻率分離。常見的

GLAD應用:高斯光束的吸收和自聚焦效應

的,這將使不同空間位置的光所經歷的光程長度不同,即介質對入射光束的作用等價于光學透鏡,從而導致光束的自行聚焦效果。

特別地,當入射光束強度沿垂直光軸的界面內呈高斯形時,且強度足夠產生非線性效應的情況下

發表于 06-17 08:52

GLAD應用:高斯光束的吸收和自聚焦效應

的,這將使不同空間位置的光所經歷的光程長度不同,即介質對入射光束的作用等價于光學透鏡,從而導致光束的自行聚焦效果。

特別地,當入射光束強度沿垂直光軸的界面內呈高斯形時,且強度足夠產生非線性效應的情況下

發表于 05-16 08:47

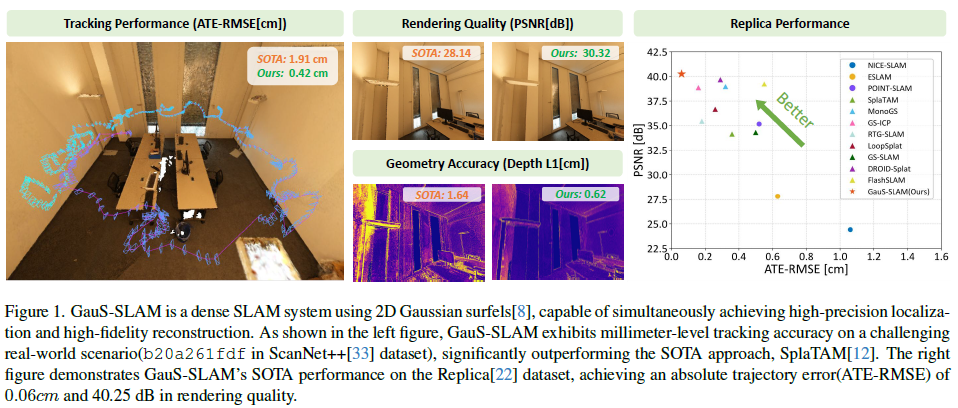

基于高斯的稠密視覺SLAM研究

基于高斯的場景表示在新視角下會出現幾何失真,這大大降低了基于高斯的跟蹤方法的準確性。這些幾何不一致主要源于高斯基元的深度建模以及在深度融合過程中表面之間的相互干擾。為了解決這些問題,我們提出了一種

基于 FPGA 的任意波形發生器+低通濾波器系統設計

第一部分 設計概述

1.1 設計目的

本次設計包括基于FPGA的任意波形發生器設計實現和基于FPGA的低通濾波器設計實現。

波形發生器是一種

發表于 05-07 15:34

OptiSystem應用:FBG濾波仿真

光柵組件在OptiSystem中作為濾波器的應用。本案例有兩種項目布局。在第一種布局中,使用了白色光源。在第二種布局下,使用了高斯脈沖。

2. 白光光源下的FBG濾波器

下圖所示為光路圖。

初始

發表于 04-10 08:45

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

~

01、數字信號處理的FPGA實現

旨在講解前端數字信號處理算法的高效實現。首先概述了當前的FPGA技術、器件以及用于設計最先進DSP系統的工具。闡述了計算機算法的概念、理論、FI

發表于 04-07 16:41

LC濾波器設計與制作 [日 森榮二]

本書主要介紹了濾波器的種類和特性,低通濾波器的經典設計,巴特沃思型低通濾波器的設計,切比雪夫型低通濾波器的設計,白塞爾型低通濾波器的設計,

發表于 03-06 15:04

基于FPGA的FIR數字濾波器設計

在現代通信信號處理領域中,隨著各種精密計算和快速計算的發展對信號處理的實時性、快速性的要求越來越高。以往的模擬濾波器無法克服電壓漂移、溫度漂移和噪聲等問題,從而帶來了許多誤差和不穩定因素。而數字濾波器具有穩定性高、精度高、設計靈活、實現

FPGA 實現 高斯濾波

FPGA 實現 高斯濾波

評論