Abstract

在Verilog中,always block可以用來(lái)代表Flip-Flop, Combination Logic與Latch,本文比較在不寫(xiě)else下,always block所代表的電路。

Introduction

在C語(yǔ)言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

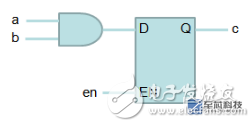

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會(huì)產(chǎn)生latch。

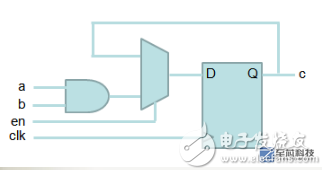

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會(huì)產(chǎn)生latch。if將產(chǎn)生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結(jié)果卻有天大的差異。

全文完。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636242

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

【「龍芯之光 自主可控處理器設(shè)計(jì)解析」閱讀體驗(yàn)】--LoongArch的SOC邏輯設(shè)計(jì)

本書(shū)第二章以SOC BX2004講述了LoongArch的SOC邏輯設(shè)計(jì)。

芯片使用130nm CMOS工藝,CPU內(nèi)核工作頻率120MHz,內(nèi)存總線工作頻率81MHz,功耗小于250 mW。核心

發(fā)表于 01-18 13:45

199.CHH?Series?厚膜超級(jí)高功率電阻工程版規(guī)格書(shū)(P-10-01-210-03)

199.CHHSeries厚膜超級(jí)高功率電阻工程版規(guī)格書(shū)

發(fā)表于 11-25 17:25

?0次下載

使用NucleiStudio生成tb仿真需要的.verilog文件

打開(kāi)仿真頂層文件tb_top.v,存放在ITCM模塊里面的指令是通過(guò)readmemh函數(shù)讀入.verilog文件實(shí)現(xiàn)的:

下面通過(guò)對(duì)NucleiStudio IDE進(jìn)行設(shè)置,實(shí)現(xiàn)將c

發(fā)表于 11-05 07:07

利用蜂鳥(niǎo)E203搭建SoC【1】——AXI總線的配置與板級(jí)驗(yàn)證

由于Vivado中Block Design的友好的ui界面以及豐富的IP資源,在FPGA上實(shí)現(xiàn)SoC大多會(huì)采用Block Design進(jìn)行設(shè)計(jì)與實(shí)現(xiàn)。對(duì)于基于蜂鳥(niǎo)e203內(nèi)核的SoC設(shè)

發(fā)表于 10-30 07:35

金山區(qū)黨政代表團(tuán)到訪西井科技

在西井科技上海總部,金山區(qū)黨政代表團(tuán)參觀了西井武夷路展廳,現(xiàn)場(chǎng)觀摩了西井在智慧物流、自動(dòng)駕駛等領(lǐng)域的創(chuàng)新產(chǎn)品與應(yīng)用場(chǎng)景。

Altera Agilex 3/5 FPGA和SoC的功能特性

Agilex 5 FPGA 和 SoC 以及新推出的 Agilex 3 FPGA 和 SoC 代表著可編程邏輯技術(shù)方面的重大飛躍。這兩個(gè)設(shè)備系列均具備全新功能,可隨著設(shè)計(jì)需求的變化實(shí)現(xiàn)輕松遷移和靈活擴(kuò)展。

通嘉科技大功率之高性能集成PFC+LLC解決方案-LD7771/T

其臨界模式(CrM)PFC級(jí)採(cǎi)用數(shù)位電路實(shí)現(xiàn)臨界模式控制,具備低電磁干擾(EMI)、低電流諧波(THDi)及高功因(PF)的優(yōu)勢(shì),特別適合各應(yīng)用領(lǐng)域300W以下的應(yīng)用;LLC級(jí)則是採(cǎi)用

發(fā)表于 08-15 11:21

?3次下載

【米爾-安路MYD-YM90X 創(chuàng)意秀】點(diǎn)燈也是入門(mén)絕活

DR1系列,是集成了雙核ARM Cortex-A35@1GHz 的FPGA,或者說(shuō)SoC FPGA,對(duì)標(biāo)的就是我們熟悉的Xilinx ZYNQ 7000 SoC FPGA。

安路MYC-YM90X

發(fā)表于 08-10 22:10

FP5207中文應(yīng)用說(shuō)明書(shū)

1.2V,內(nèi) 置軟啟動(dòng),工作頻率由外部電阻調(diào)整;過(guò)電流保護(hù),檢測(cè)電感峰值電流,檢測(cè)電阻Rcs接在

發(fā)表于 08-08 15:17

?0次下載

26 路觸控按鍵和 PWM 的增強(qiáng)型 8051SOC RM1221A數(shù)據(jù)手冊(cè)

26 路觸控按鍵和 PWM 的增強(qiáng)型 8051SOC基于 8051 指令的高速 1T 增強(qiáng)型 MTP SOC

發(fā)表于 07-25 15:28

?0次下載

半導(dǎo)體器件

載子帶負(fù)電2. P型半導(dǎo)體→在帶電性的半導(dǎo)體材料中摻入少量的三價(jià)無(wú)素(負(fù)電),使其內(nèi)部多數(shù)載子帶負(fù)電 四、 相關(guān)元件:二極體、三極體、集成

發(fā)表于 04-22 15:17

200w開(kāi)關(guān)電源__功率級(jí)電路設(shè)計(jì)總結(jié)

/5A

24V/6A

電源分為兩個(gè)單元。第一電源集成一個(gè)功率因素校正電路,內(nèi)置在 FAN4800 PFC/PWM(脈寬調(diào)制)二合一控制器

發(fā)表于 04-02 15:17

FPGA Verilog HDL語(yǔ)法之編譯預(yù)處理

Verilog HDL語(yǔ)言和C語(yǔ)言一樣也提供了編譯預(yù)處理的功能。“編譯預(yù)處理”是Verilog HDL編譯系統(tǒng)的一個(gè)組成部分。Verilog HDL語(yǔ)言允許在程序中使用幾種特殊的命令(它們不是一般

4芯光纜是不是代表可以走4路網(wǎng)絡(luò)

4芯光纜并不意味著可以直接走4路網(wǎng)絡(luò)。光纜的芯數(shù)主要指的是光纜內(nèi)部光纖的數(shù)量,而光纖則是用來(lái)傳輸光信號(hào)的媒介。在光纜中,每一根光纖都可以獨(dú)立地傳輸一路光信號(hào),因此理論上4芯光纜可以支持4路光信號(hào)

always block內(nèi)省略else所代表的電路 (SOC) (Verilog)

always block內(nèi)省略else所代表的電路 (SOC) (Verilog)

評(píng)論