CMOS/TTL邏輯測試筆,可探測時鐘信號,CMOS / TTL logic tester

關鍵字:CMOS/TTL邏輯測試筆,可探測時鐘信號

CMOS/TTL邏輯測試筆,可探測時鐘信號

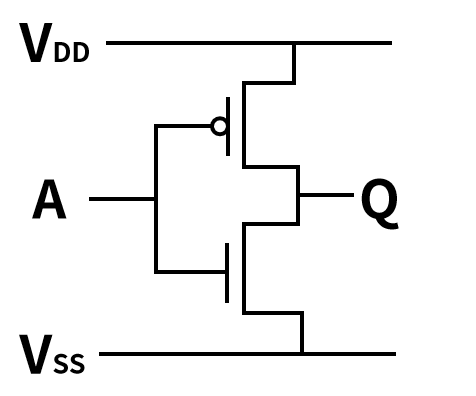

本電路(見附圖)能用來測試CMOS和TTL邏輯電路的邏輯狀態,也能測試邏輯電路中任何地點幾Hz至10MHz以上的時鐘信號。

探頭電路的電源供給可用鱷魚夾取用被測電路中的電源。在本電路中,LM319雙比較器芯片IC1連接成窗口檢測器,比較器N1的反相輸入腳在開關S1置TTL位置時偏置到接近2V,當S1置CMOS位置時偏置到Vcc的80%。只有在邏輯探頭輸入電壓超過偏置電壓時,N1的輸出才能變低電位,紅色LED1發光,指示邏輯探頭測得的邏輯狀態為“1”。

同理,比較器N2的反相輸入腳在開關S1置TTL位置時偏置到接近0.8V,當S1置CMOS位置時偏置到Vcc的20%。只有在邏輯探頭輸入電壓小于偏置電壓時,N2的輸出才能變低電位,綠色LED2發光,指示邏輯探頭測得的邏輯狀態為“0”。

邏輯探頭還通過C1連接到芯片CD4049(六反相器IC2)的N3輸入,可同時送入交流和時鐘信號。N3的作用是緩沖器,它只耦合N3輸入,輸出端的脈沖下降沿至N4的輸入端。

N6用來驅動黃色LED3,它的短暫發光表示探頭測到振蕩輸入。N6的輸出還用來封閉和激活由N7和N8構成的振蕩器,此振蕩器用來推動蜂鳴器PZI在單穩周期內發聲,表示探頭測到振蕩輸入。所以對測試時鐘脈沖和振蕩信號來說,測試邏輯探頭有可見、可聞兩種指示手段。

將測試結果見附表。

翻譯:子良

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

熱點推薦

單片機TTL和CMOS電平知識

1. TTL電平

TTL指雙極型三極管邏輯電路(transistor transistor logic),這種信號0對應0V,1對應3.3V

發表于 12-03 08:10

SN74AHCT244NSR 歸屬 74AHCT 系列的高速 CMOS 邏輯八路緩沖器 / 線路驅動器

與TTL邏輯電路對接,無需額外電平轉換器件,能靈活融入不同邏輯電平的數字系統,降低電路設計復雜度。●高速低耗性能優異:傳播延遲僅5-10ns,高速傳輸特性適配高頻信號場

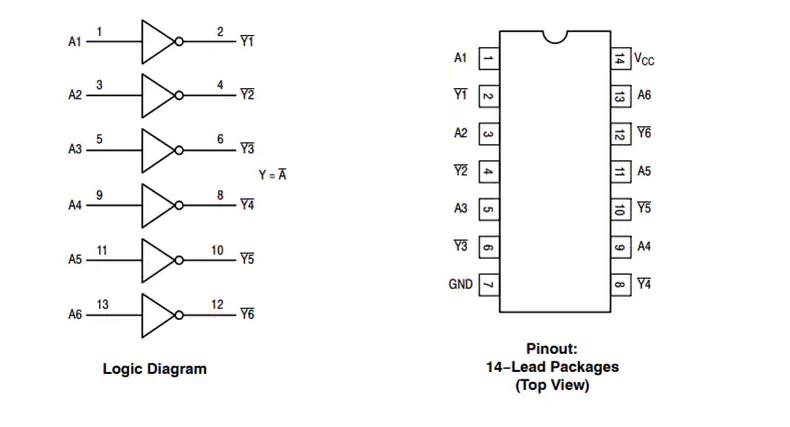

深入解析ON Semiconductor MC74VHC04與MC74VHCT04A CMOS六路反相器數據手冊

) 逆變器實現了與等效雙極型SCHOTTKY TTL類似的高速運行,同時保持了CMOS低功率耗散。MC74VHC04輸入與標準CMOS電平兼容,而MC74VHCT04A輸入與TTL電平

關于光模塊TTL電平你知道多少?

TTL電平是? TTL電平信號規定,+5V等價于邏輯“1”,0V等價于邏輯“0”(采用二進制來表示數據時)。這樣的數據通信及電平規定方式,被

TTL光模塊電平標準是什么

在數字電路領域,TTL(Transistor-TransistorLogic,三極管-三極管邏輯)和 LVTT(Low Voltage TL,低壓晶體管-晶體管邏輯)是兩種重要的邏輯電

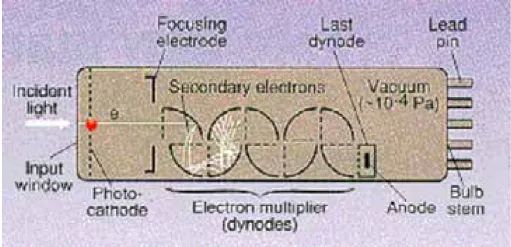

光電探測器PMT、APD、CCD、CMos、ICCD、EMCCD

,屬于靈敏度極高,響應速度非常快的單點光探測器。 主要是由光電發射陰極(光陰極)和聚焦電極、電子倍增極及電子收集極(陽極)等組成。 核心原理就是:通過把入射的光子轉化成電子,在電子倍增電場作用下進行倍增放大,放大后的電子通過陽極收集后輸出。通過AD轉換器,信號

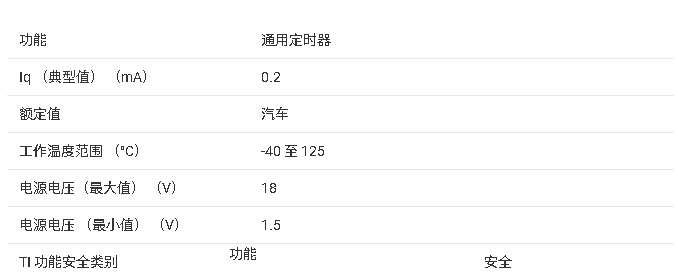

?TLC3555-Q1 汽車級高速CMOS定時器技術文檔總結

TLC3555-Q1 是一款采用 TI CMOS 工藝制造的單片定時電路。該定時器與CMOS、TTL和MOS邏輯完全兼容,工作頻率高達3MHz甚至更高。TLC3555-Q1 從性能和功

光模塊TTL電平是什么?

TTL電平信號規定,+5V等價于邏輯“1”,0V等價于邏輯“0”(采用二進制來表示數據時)。這樣的數據通信及電平規定方式,被稱做TTL(晶體

TTL/LVTTL:供電電源、電平標準及使用注意事項

在數字電路領域,TTL(Transistor-Transistor Logic,三極管 - 三極管邏輯)和 LVTTL(Low Voltage TTL,低壓晶體管 - 晶體管

CMOS的邏輯門如何應用在電路中

低電平時,PMOS導通實現電流上拉;輸入高電平時,NMOS導通完成信號下拉。兩種晶體管交替工作,構成無直流通路的完美配合。合科泰采用的溝槽屏蔽柵工藝優化了晶體管性能,讓CMOS互補管在開關切換的電路降低,滿足現代互聯網和人工智能的能耗要求。

硬件基礎篇——TTL與CMOS電平

電平TTL集成電路主要由BJT晶體管構成,如STC單片機,電平規范如下:輸出模式:Uoh ≥ 2.4V,Uol≤0.4V;輸入模式:Uih ≥ 2.0V,Uil≤0.8V;3、CMOS電平CMOS

發表于 03-22 15:21

CMOS/TTL邏輯測試筆,可探測時鐘信號,CMOS / TTL logic tester

CMOS/TTL邏輯測試筆,可探測時鐘信號,CMOS / TTL logic tester

評論