在數據采集系統中,所設計的系統應具有通用性,可根據不同的數據采集對象,產生不同的采樣頻率;或者系統處于不同的運動情況時,能夠動態改變采樣頻率,即數據采集系統應當具有改變采樣頻率的能力。傳統的數據采集系統,一般都是固定頻率的數據采集,很難應用于其它采樣頻率的場合。為了使所設計的系統適用于不同的場合,具有廣泛的適應性,系統必須具有在線改變采樣頻率的方法。可編程時鐘發生器芯片ICD2053B提供了系統動態改變頻率的方法,其動態時鐘輸出頻率范圍從391kHz到100MHz(TTL電平)或391kHz到90MHz(CMOS電平),具有較寬的頻率范圍,在系統中采用ICD2053B能很好地解決上述問題。ICD2053B提供完全用戶可編程的鎖相環特性,鎖相環振蕩器輸入由外部參考時鐘(1MHz~25MHz)或外部晶振(2MHz~24MHz)提供。其二線串行接口便于對輸出頻率進行編程控制,具有三態輸出控制使能。5V供電、低功耗、小體積又使其適宜于功耗和空間要求高的應用場合。它所具有的動態改變輸出頻率的能力,給設計得提供了靈活的設計自由度。

1 ICD2053B的結構及工作原理

1.1 引腳功能表及內部結構圖

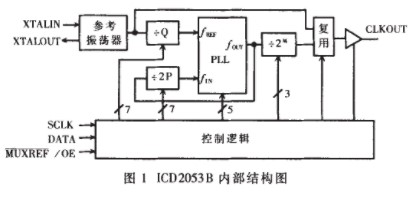

ICD2053B的內部結構如圖1所示,引腳功能如表1所示。

表1 ICD2503B引腳功能表

1.2 ICD2053B的寄存器

ICD2053B包含兩個寄存器:控制寄存器和編程寄存器。

這兩個寄存器使用協議字011110來區分是控制寄存器數據還是編程寄存器數據。所有要發送的其它數據(除協議字外)在連續3個1之后,不論原來其后的數值是1還是0必須插入一個0,來區分是協議字還是數據。所有要編程的串行字從最低位開始串行地移入,當SCLK從低到高跳變時,將數據移入到可編程寄存器中。一旦協議字檢出后,前面已移入的8位數據就傳遞到控制寄存器中,然后控制命令立刻被執行。

1.2.1 控制寄存器

當要寫入的數據寫入到控制寄存器時,必須包含協議字011110,用來識別所寫入的數據為控制寄存器數據。

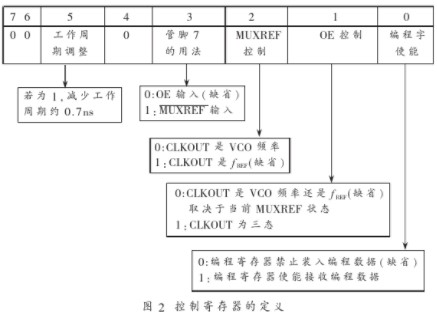

控制寄存器用來控制ICD2053B的非頻率特性設置,它是一個8位的寄存器,其含義如圖2所示。

控制寄存器數據的寫入從控制字的低位(位0)開始,一直到控制字的高位(位7),然后是6位的協議字寫入到寄存器中,故控制寄存器的設置其需14位數據。

在上電后,控制寄存器裝入缺省值00000100,即MUXREF控制位設置為1,強制CLKOUT輸出為參考頻率fREF,編程寄存器禁止裝入,芯片管腳7是輸出使能管腳。

1.2.2 編程寄存器

按照所需要的輸出頻率,將22位的編程字裝入到編程寄存器,用以實現輸出頻率的更改。由于協議字為011110,在傳送編程數據時,凡連續出現3個1,在其后便添一個“虛”0,以避免混淆;在接收端凡連續收到3個1,就將其后的零丟掉,故裝入的數據要完成“位填充”功能。由于這個原因,實際的編程字的長度可以為22到27位。編程寄存器各字段含義如表2所示。

表2編程寄存器定義

可編程振蕩器的頻率fvco由下式確定:

fvco=2×fREF×(P+3)/(Q+2)

式中,fREF為參考頻率(1MHz~25MHz)。

Fvco的頻率值必須保證處在50MHz和150MHz之間。因此對于輸出頻率低于50MHz,fvco必須設法處于上述限制之內,可通過復用(M)字段的設置來實現該功能,M初值為000。首先將所希望的輸出頻率倍頻,作為新的輸出頻率,M值增1,若仍未處于上述范圍,循環直至滿足要求為止(M≤7)。由于倍頻所希望的輸出頻率,實際的輸出頻率就要進行相應的分頻,最大的分頻值為128,即輸出頻率fout由下式確定:

fout=fvco/2 m

指針(I)字段用來使壓控振蕩器VCO預置到適當的頻率范圍。若fvco在50~80MHz,I為0000;若fvco在80~150MHz內,I為1000。注意,此處僅指壓控振蕩器頻率fvco。而非所希望的輸出頻率。

如果壓控振蕩器的頻率正好處在80MHz,則推薦使用對應高頻率范圍的設置,即I為1000。

1.2.3 VCO編程的限制

編程時有以下3個主要的限制:

(1)50MHz≤fvco≤150MHz

(2)1≤P≤127

(3)1≤Q≤127

對于上述限制,要在最優速度、最低噪聲和VCO穩定性等因素中,折衷考慮。

2 頻率調整過程

當改變頻率到一個新頻率時,由于串行字的變化,輸出信號頻率會產生頻率跳變。為了避免這種情況發生,可以利用控制寄存器中MUXREF的特性。MUXREF使得參考時鐘多路復用,無跳變地切換,作為輸出時鐘,即當VCO尋求新的編程值時,它使輸出時鐘頻率維持在固定的參考時鐘頻率上。

ICD2053B初始化或調整新頻率的步驟如下:

(1)裝入控制寄存器控制字,允許編程寄存器裝入數據,使能MUXREF功能,使輸出頻率穩定在參考頻率上,且這個過程保證無跳變。控制字如下:

控制字 011110 0000X101 --- LSB

協議字 要寫入的控制寄存器控制字

管腳7的用法由用戶定義,用X表示。

注意:所有的數據都從低位移入,首先移入的是控制字的最低位,協議字緊跟著控制寄存器的控制字之后輸入到寄存器中。

(2)裝入編程寄存器編程字,使用“位填充”,最多可得27位的編程字。

(3)裝入控制寄存器控制字,使能MUXREF功能,禁止編程寄存器數據的裝放。該過程將編程字裝入到編程寄存器中,保持輸出在參考頻率上,同時進行新頻率的建立。控制字如下:

控制字 011110 0000X100

(4)等待至少10ms,使壓控振蕩器VCO的頻率穩定在新的頻率值上。

(5)裝入控制寄存器控制字,使能芯片輸出新頻率,該過程保證無跳變。控制字如下:

控制字 011110 0000X000

總之,為了使芯片通過編程輸出一個新頻率,該芯片需要三個控制字加上一個編程字共同來實現。

3 ICD2053B在數據采集系統中的應用

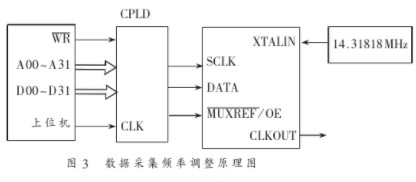

在我們所設計的通用數據采集系統中,系統可以在線改變采樣頻率,具有動態改變采樣頻率的能力。該通用數據采集系統選用可編程時鐘發生器芯片ICD2053B,提供大范圍的采樣頻率(391kHz~100MHz)。ICD2053B的編程連接僅需要兩條線,即SCLK(2)、DATA(4)。利用ICD2053B動態改變采樣頻率的電路原理圖如圖3所示。

在該系統中,參考晶振頻率為14.31818MHz。可編程邏輯器件CPLD作為上位機與ICD2053B的接口,實現可編程時鐘發生器串行時鐘和編程數據的串行輸入控制功能。CPLD的主時鐘由上位機提供,經分頻后產生所需的串行時鐘SCLK,控制移位寄存器,串行移出所需的編程數據。為了幫助實現計算,上位機提供系統工作的驅動程序,根據用戶的參考輸入頻率和所希望的輸出頻率,產生適當的編程寄存器編程字。

當用戶輸入所希望的輸出頻率時,驅動程序自動計算所需的編程字,同時考慮到“位填充”的要求,產生實際的編程字。然后在上位機的控制下,經上位機寫入到可編程邏輯器件CPLD對應的寄存器中,作為觸發信號,啟動頻率調整狀態機。

按照頻率調整過程,該狀態機的狀態0為空閑狀態;狀態1為在串行時鐘SCLK的控制下,將控制字01111000000101由低位開始串行移入可編程芯片中;狀態2為在串行時鐘的控制下,將寄存器中存放的編程字串行移入到可編程芯片中,此時要增加超過22位編程數據的位計數器,以便正確地將編程字移入;狀態3為在串行時鐘的控制下,將控制字01111000000100由低位開始串行移入可編程芯片中;狀態4為在串行時鐘的控制下,延時等待10ms,進入下一狀態;狀態5為在串行時鐘的控制下,將控制字0111100000000由低位開始串行移入可編程芯片中,使芯片輸出所希望的新頻率,同時進入狀態0,等待下一次的頻率調整。

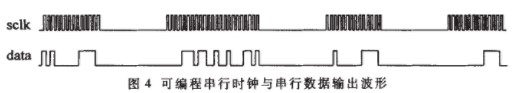

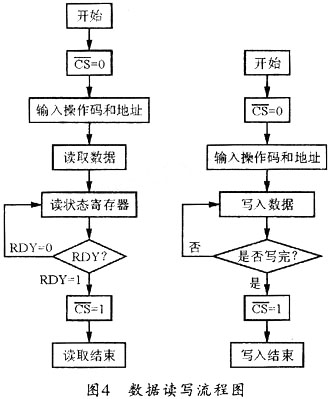

串行時鐘并不是一直輸出,只有在對ICD2053B進行編程調整輸出頻率時,才有串行時鐘輸出。即串行時鐘在非編程狀態時輸出為零,在編程狀態時才輸出可編程時鐘。若產生39.5MHz的輸出頻率,考慮位填充的實際編程字為589370H,其相應的可編程時鐘與串行數據輸出的波形如圖4所示。

在該數據采集系統中,采用可編程時鐘發生器芯片ICD2053B,動態調整采樣頻率,使得系統具有通用性。系統硬件設計簡單,通過串行數據編程,可在線改變采樣頻率。而在頻率調整過程中,無頻率跳變,輸出時鐘頻率維持在固定的參考時鐘頻率上,特別適用于對采樣頻率調整要求高的場合。

-

芯片

+關注

關注

463文章

54010瀏覽量

466175 -

cpld

+關注

關注

32文章

1259瀏覽量

173904 -

計數器

+關注

關注

32文章

2316瀏覽量

98196

發布評論請先 登錄

用ARM和FPGA怎么設計便攜式人工地震數據采集系統?

基于CPLD的多通道數據采集系統設計

CPLD在多路高速同步數據采集系統中的應用

CPLD芯片ICD2053B的原理構造及在數據采集系統中的應用

CPLD芯片ICD2053B的原理構造及在數據采集系統中的應用

評論