AD9540:高性能低抖動時鐘發生器的深度解析

在電子工程領域,時鐘發生器扮演著至關重要的角色,尤其是對于那些對時鐘精度和穩定性有極高要求的應用場景。今天,我們就來深入探討一下Analog Devices推出的AD9540,一款專門為滿足高性能數據轉換器嚴格時鐘要求而設計的655 MHz低抖動時鐘發生器。

文件下載:AD9540.pdf

一、產品特性概覽

AD9540擁有一系列令人矚目的特性,使其在眾多時鐘發生器中脫穎而出。

卓越的時鐘性能

- 低抖動表現:具備出色的本征抖動性能,能為系統提供穩定、精確的時鐘信號。例如在某些對時鐘精度要求苛刻的測試設備中,可以有效減少因時鐘抖動帶來的測量誤差。

- 高頻率處理能力:支持高達2.7 GHz的外部VCO速率,同時擁有655 MHz的可編程輸入分頻器和CML模式、PECL兼容的輸出驅動器,可滿足不同頻率需求。

- 精細的頻率調節:具有48位頻率調諧字分辨率,能實現極其精細的頻率調節,步長小于2.33μHz,這在一些需要精確頻率控制的通信系統中非常關鍵。

靈活的配置選項

- 多種可編程功能:包括可編程的RF分頻器(÷R)、相位/頻率配置文件、電荷泵電流等。例如,通過改變RF分頻器的分頻比,可以靈活調整輸出頻率;而可編程的電荷泵電流則能更好地匹配不同的系統需求。

- 多模式操作:支持8種可編程相位/頻率配置文件,可根據不同的應用場景快速切換時鐘頻率和相位。還支持擴展頻譜模式操作,進一步增強了其在不同電磁環境下的適應性。

其他特性

- 低功耗設計:通過軟件控制的掉電模式,可有效降低系統功耗。例如在一些電池供電的設備中,合理使用掉電模式可以延長設備的續航時間。

- 寬溫度范圍:能夠在 -40°C至 +85°C的擴展汽車溫度范圍內正常工作,適用于各種惡劣的工業和汽車應用環境。

二、產品應用領域

AD9540的廣泛應用領域充分展示了其強大的適應性和高性能。

數據轉換領域

- 高性能數據轉換器:為高速、高精度的數據轉換器提供穩定、低抖動的時鐘信號,確保數據轉換的準確性和可靠性。例如在一些高速采樣的ADC中,AD9540的低抖動時鐘可以有效提高ADC的信噪比,從而提升整個系統的性能。

通信領域

- 基站時鐘:為基站的各種模塊提供精確的時鐘同步,保證基站的穩定運行。在5G基站等對時鐘同步要求極高的通信設備中,AD9540的高性能時鐘可以有效減少通信干擾,提高通信質量。

- 網絡時鐘:適用于SONET/SDH、Gigabit Ethernet等網絡時鐘應用,確保網絡數據的準確傳輸和同步。

其他領域

- 儀器儀表:為各種測試和測量設備提供精確的時鐘信號,保證測量結果的準確性。

- 汽車雷達:為汽車雷達系統提供穩定的時鐘信號,確保雷達的探測精度。

- 其他應用:還可用于聲光設備驅動、快速LO頻率合成等領域。

三、工作原理剖析

PLL電路

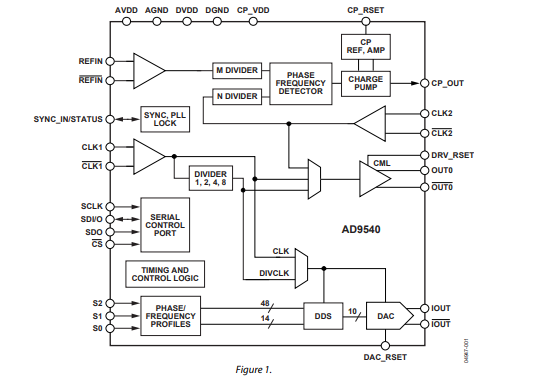

PLL(鎖相環)電路是AD9540的核心部分之一,它主要由RF分頻器、48位DDS核心、14位可編程延遲調整、10位DAC(數模轉換器)、相位頻率檢測器和可編程輸出電流電荷泵組成。

- RF分頻器:可以接受高達2.7 GHz的差分或單端信號,并將其分頻后提供給DDS和CML驅動。通過編程設置分頻比,可以靈活匹配不同頻率的輸入信號。

- 相位頻率檢測器:有兩個差分輸入REFIN和CLK2,可由單端信號驅動。其最大輸入速度為200 MHz,當信號頻率超過200 MHz時,可通過控制寄存器設置分頻器進行分頻。

- 電荷泵:根據相位頻率檢測器產生的誤差信號輸出電流,通過在CP_RSET引腳連接電阻來編程輸出電流,還可通過控制寄存器設置可編程縮放器來調整電流大小。

CML驅動

片上的電流模式邏輯(CML)驅動能夠產生非常低抖動的時鐘邊沿。其輸出電流可通過在DRV_RSET引腳連接電阻進行編程,還可以獨立編程上升沿和下降沿的轉換速率,以控制過沖和振鈴。CML驅動可以由RF分頻器輸入、RF分頻器輸出或CLK2輸入驅動。

DDS和DAC

DDS(直接數字頻率合成)技術實現了設備內的精確頻率分頻。通過向48位累加器加載頻率調諧字,控制累加器的溢出率,從而生成所需的頻率。累加器的輸出經過相位偏移調整后,通過相位 - 幅度轉換塊轉換為幅度字,再輸入到10位DAC中。DAC將數字信號轉換為模擬信號,輸出重構的正弦波,需要通過負載電阻進行濾波以去除高頻雜波。

四、典型應用電路示例

雙時鐘配置

在這種配置中,M = 1,N = 16,R = 4,DDS調諧字為 ?,使得CLOCK1’的頻率等于CLOCK1的頻率。通過DDS的相位調整,可以實現CLOCK1’相對于CLOCK1的14位可編程上升沿延遲。

光網絡時鐘

將AD9540配置為光網絡時鐘,可用于生成622 MHz的OC12時鐘。同時,DDS可以編程輸出8 kHz作為子系統中其他電路的基準參考。

分數分頻環

該環路利用DDS的精確頻率分頻(48位)和頻率掃描功能。通過編程DDS從24 MHz掃描到25 MHz,可以使VCO的輸出從2.7 GHz掃描到2.6 GHz。

直接上變頻

將AD9540配置為使用DDS作為PLL的精確參考。由于VCO頻率小于655 MHz,可直接將其輸入到相位頻率檢測器的反饋路徑中。

LO和基帶調制生成

利用AD9540的PLL部分生成LO,DDS部分生成調制后的基帶信號,再通過外部混頻器在RF ISM頻段進行簡單的調制。

五、寄存器配置與控制

AD9540通過一系列寄存器進行配置和控制,包括Control Function Register 1(CFR1)、Control Function Register 2(CFR2)等。

CFR1寄存器

主要用于控制各種功能、特性和操作模式。例如,通過設置CFR1[3]可以啟用自動同步功能,使設備自動將內部SYNC_CLK與外部參考信號同步;通過設置CFR1[15]可以選擇串行數據傳輸的模式(MSB先傳或LSB先傳)。

CFR2寄存器

主要控制模擬和時序功能。例如,通過CFR2[39]可以對DAC部分進行掉電控制;通過CFR2[22:21]可以控制RF分頻器的分頻比。

六、性能與注意事項

性能指標

AD9540在各種性能指標上表現出色,如總系統抖動、相位噪聲、時鐘驅動器的上升和下降時間等。在不同的頻率和測試條件下,其各項性能指標都能滿足嚴格的要求。

注意事項

- 絕對最大額定值:在使用過程中,要確保各項參數不超過絕對最大額定值,如電源電壓、工作溫度等,否則可能會導致設備損壞。

- ESD防護:由于AD9540對靜電比較敏感,在操作和焊接過程中要注意靜電防護,避免靜電對設備造成損壞。

AD9540是一款功能強大、性能卓越的時鐘發生器,在高性能數據轉換、通信、儀器儀表等眾多領域都有著廣泛的應用前景。通過深入了解其特性、工作原理、應用電路和寄存器配置,電子工程師可以更好地發揮其優勢,為設計出高性能的電子系統提供有力支持。大家在實際應用中有沒有遇到什么問題或者有什么獨特的使用經驗呢?歡迎在評論區分享交流。

-

時鐘發生器

+關注

關注

1文章

355瀏覽量

70150 -

低抖動

+關注

關注

0文章

75瀏覽量

6124 -

AD9540

+關注

關注

0文章

4瀏覽量

8470

發布評論請先 登錄

AD9540:高性能低抖動時鐘發生器的深度解析

AD9540:高性能低抖動時鐘發生器的深度解析

評論