文章來源:學習那些事

原文作者:前路漫漫

本文介紹了集成電路封裝在寬I/O接口領域中的2.5DIC集成技術。

概述

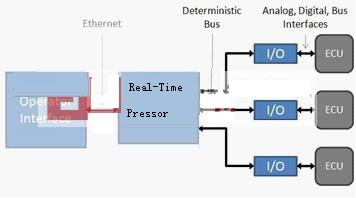

2.5DIC集成在寬I/O接口領域有著重要的實際應用,其核心結構由一塊采用TSV(硅通孔)技術的無源硅片,以及未采用TSV技術的高性能、高密度IC芯片共同組成。這塊無源硅片也被稱為無源轉接板,主要作用是為IC芯片提供支撐,同時其表面的RDL(再分布層)是實現芯片間橫向通信的核心結構,相關結構可參考圖1和圖2最右側所示,這種集成方式即為2.5DIC集成。

隨著IC芯片集成密度和引腳數量的持續提升,以及IC襯底間距與尺寸的不斷縮小,傳統封裝基板已無法滿足當前IC芯片的使用需求,而采用中間基板(無源轉接板)則能有效解決這一問題。圖3、圖4和圖5展示了該技術的部分實際應用案例,其中圖3和圖4中的樣品采用了臺積電(TSMC)自主研發并運營的一站式垂直集成制造工藝(CoWoS,即芯片-轉接板晶圓-封裝基板堆疊工藝)進行制造與組裝,圖5中的樣品則由多方協作完成,其中包含TSV/RDL轉接板的制造以及MEOL工藝的應用,MEOL的具體定義可參考相關技術規范。

TSV/RDL無源轉接板的實際應用

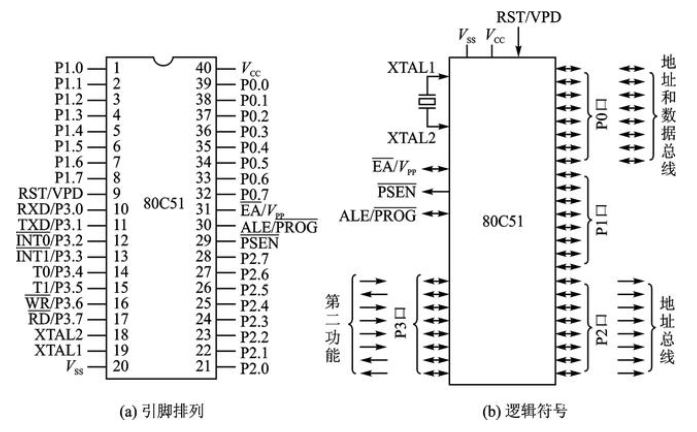

從圖3至圖5的實際樣品中可以清晰看出,即便封裝基板采用12個積層結構(6-2-6),仍無法滿足四個28nm FPGA芯片的使用需求。為此,還需搭配一塊具備四個頂部RDL層(包含三個銅大馬士革層和一個鋁層)的TSV硅轉接板,該轉接板的TSV直徑為10um、深度為100um。其核心原因在于,為提升器件制造良率、降低生產成本,采用臺積電28nm工藝制造的大型SoC芯片會被切割為四個較小的FPGA芯片,這些FPGA芯片之間的10000余個橫向互連,主要通過轉接板上最小間距為0.4um的RDL實現。RDL與鈍化層的最小厚度約為1um,每個FPGA芯片擁有超過50000個帶有焊料帽層的銅柱微凸點,轉接板上的微凸點總數則超過200000個,微凸點間距為45um,相關細節可參考圖3至圖5。由此可見,無源TSV/RDL轉接板非常適用于極細間距、高I/O數量、高性能以及高密度的半導體IC應用場景。

轉接板的制造

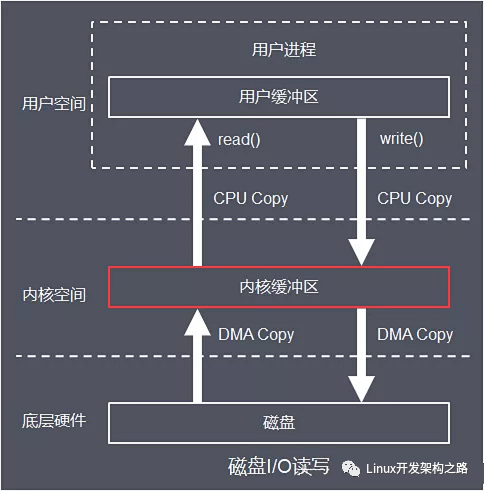

轉接板的制造過程主要包含兩個關鍵環節,分別是TSV的制造和RDL的制造,以下將對這兩個環節的具體工藝進行詳細說明。

TSV的制造工藝流程如圖6所示,首先通過熱氧化或等離子體增強化學氣相沉積(PECVD)工藝在硅襯底表面形成SiN/SiO?絕緣層。隨后,經過光刻膠涂覆與TSV光刻工藝處理后,采用Bosch型深反應離子刻蝕(DRIE)技術將TSV通孔刻蝕至硅襯底內部,形成深寬比為10.5的通孔結構。接下來,通過亞大氣化學氣相淀積(SACVD)工藝對蝕刻后的TSV結構進行SiO?襯墊處理,再依次沉積Ta阻擋層并采用物理氣相沉積(PVD)技術進行鍍銅填充,最終完成TSV結構的制備。制備完成的盲孔TSV頂部開孔直徑約為10um,深度約為105um,深寬比維持在10.5。由于該通孔結構具有較高的深寬比,因此采用自下而上的電鍍機制,以確保場區銅層厚度合理且TSV結構無縫隙。

圖7為TSV橫截面的掃描電子顯微鏡(SEM)圖像,從圖像中可觀察到TSV底部直徑略有減小,這是蝕刻工藝過程中的正常現象。場區銅層厚度控制在5um以內,電鍍完成后需在400℃環境下進行30分鐘的退火處理。為完成整個TSV制造工藝,最后通過化學機械拋光(CMP)技術去除場區多余的銅層。

目前RDL的制造主要有兩種成熟方法。第一種方法是采用聚合物材料作為鈍化層,常用的聚合物包括聚酰亞胺(PI)PWDC1000、苯并環丁烯(BCB)環烯4024-40、聚苯并雙惡唑(PBO)HD-8930以及氟化芳香族AL-X2010等,金屬層則通過電鍍(如電鍍銅)工藝制備。該方法已被外包半導體組裝和測試(OSAT)企業廣泛應用于RDL制造(無需使用半導體設備),適用于晶圓級(扇入)芯片規模封裝、嵌入式晶圓級(扇出)球柵陣列封裝以及(扇出)再分布芯片封裝等場景。第二種方法是銅大馬士革方法,該方法由傳統半導體后道工藝改進而來,主要用于制備銅金屬RDL,圖3至圖5中的RDL均采用該方法制備。總體而言,銅大馬士革方法能夠制備出更薄的結構(包括介質層和銅RDL),且可實現更細的線寬、間距以及更高的集成精度。詳細的工藝將在之后的文章介紹。

-

集成電路

+關注

關注

5462文章

12659瀏覽量

375512 -

接口

+關注

關注

33文章

9581瀏覽量

157565 -

封裝

+關注

關注

128文章

9313瀏覽量

148990

原文標題:寬I/O接口(2.5DIC集成)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PLC I/O接口的作用及選擇

145010 帶I/O接口的光電煙霧檢測電路

145010 帶I/O接口的光電煙霧檢測電路

SD卡I_O接口設計

基于FPGA I/O接口的五大優勢與FPGA深層分析

2.5DIC集成在寬I/O接口領域的實際應用

2.5DIC集成在寬I/O接口領域的實際應用

評論