納芯微磁編碼器(霍爾/AMR/TMR,尤以MT68xx為代表)采用統(tǒng)一的 “磁敏感單元→低噪聲模擬前端→高精度同步ADC→硬件CORDIC解算→多級(jí)校準(zhǔn)補(bǔ)償→多格式接口輸出” 標(biāo)準(zhǔn)化信號(hào)鏈架構(gòu)。其核心競(jìng)爭(zhēng)力在于 全維度閉環(huán)校準(zhǔn)機(jī)制 與 低延時(shí)高兼容設(shè)計(jì) :通過(guò)出廠(chǎng)校準(zhǔn)、客戶(hù)端勻速自校準(zhǔn)、實(shí)時(shí)動(dòng)態(tài)溫補(bǔ)三重補(bǔ)償,系統(tǒng)性消除固有誤差、安裝誤差與溫漂;通過(guò)硬件加速解算與可編程多接口,實(shí)現(xiàn)微秒級(jí)延時(shí)與工業(yè)主流協(xié)議全兼容。本文深度解析其信號(hào)鏈設(shè)計(jì)細(xì)節(jié)、自校準(zhǔn)完整流程、延時(shí)特性與接口兼容性,為高精度運(yùn)動(dòng)控制系統(tǒng)設(shè)計(jì)提供技術(shù)依據(jù)。

一、標(biāo)準(zhǔn)化信號(hào)鏈全鏈路設(shè)計(jì)

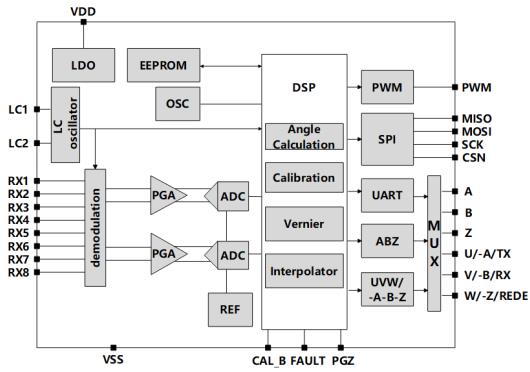

納芯微磁編碼器(以MT68xx AMR系列為典型)信號(hào)鏈采用 “模擬優(yōu)化+數(shù)字校準(zhǔn)+硬件加速” 協(xié)同架構(gòu),確保微弱磁信號(hào)到高精度角度的低失真、低延遲轉(zhuǎn)換。

1.1 磁敏感單元:正交差分信號(hào)源

- AMR架構(gòu) :集成兩對(duì)互成45°的 正交惠斯通電橋 ,直接輸出 差分SIN/COS 模擬信號(hào)(幅值數(shù)十mV),僅響應(yīng)磁場(chǎng)方向、免疫Z軸干擾。

- 霍爾/TMR :同源差分輸出架構(gòu),TMR信號(hào)幅值為AMR的30~50倍,霍爾信號(hào)最弱。

- 核心優(yōu)勢(shì) : 差分輸出+平面敏感 ,共模抑制比(CMRR)天生>85dB,為低噪聲奠定基礎(chǔ)。

1.2 模擬前端(AFE):微弱信號(hào)調(diào)理核心

低噪聲差分放大器

- 輸入噪聲 <10nV/√Hz,CMRR >100dB,抑制電橋失調(diào)與共模干擾。

可編程增益放大器(PGA)

- 增益1~64倍可調(diào),適配氣隙0.5~3mm(氣隙3mm時(shí)設(shè)64倍),確保信號(hào)滿(mǎn)量程輸入ADC。

抗混疊低通濾波(AAF)

- 二階巴特沃斯拓?fù)洌刂诡l率10kHz~200kHz可編程,濾除電機(jī)PWM開(kāi)關(guān)噪聲(>50kHz)。

1.3 高精度同步ADC:數(shù)字化保真

- 架構(gòu) : 雙通道同步采樣SAR ADC ,SIN/COS信號(hào)同時(shí)采樣,嚴(yán)格保持相位關(guān)系。

- 型號(hào)差異 :

- MT6835 (21位):16位ADC,SNR>95dB,ENOB>15位

- MT6826S (15位):14位ADC,SNR>90dB,ENOB>13位

- 基準(zhǔn) :內(nèi)部高精度帶隙基準(zhǔn)(溫漂<10ppm/℃),降低全溫域增益誤差。

1.4 硬件CORDIC角度解算:零軟件開(kāi)銷(xiāo)

- 原理 :硬件實(shí)現(xiàn)坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算,直接求解θ=arctan(SIN/COS)。

- 速度 : 納秒級(jí)解算 (<2μs),無(wú)CPU負(fù)載,支持最高150,000rpm超高速電機(jī)。

- 優(yōu)勢(shì) :純硬件流水線(xiàn), 確定性延時(shí) ,無(wú)抖動(dòng)、無(wú)中斷沖突。

1.5 數(shù)字校準(zhǔn)與補(bǔ)償模塊

- 內(nèi)置 EEPROM/OTP 存儲(chǔ)校準(zhǔn)系數(shù)。

- 集成 高精度NTC溫度傳感器 (-40℃~125℃),用于實(shí)時(shí)動(dòng)態(tài)溫補(bǔ)。

1.6 多格式輸出接口

- 支持 SPI/ABZ/UVW/PWM 并行輸出,可獨(dú)立配置。

- 集成 CRC校驗(yàn)、異常診斷、磁場(chǎng)監(jiān)測(cè) 功能。

二、全維度多級(jí)校準(zhǔn)機(jī)制(精度核心)

納芯微采用 “出廠(chǎng)校準(zhǔn) + 客戶(hù)端自校準(zhǔn) + 實(shí)時(shí)動(dòng)態(tài)溫補(bǔ)” 三級(jí)閉環(huán)校準(zhǔn)體系,全面消除四大誤差源: 電橋失配、非線(xiàn)性、安裝偏心、溫漂 。

2.1 一級(jí):出廠(chǎng)基礎(chǔ)校準(zhǔn)(芯片級(jí),納芯微完成)

- 失調(diào)校準(zhǔn) :消除SIN/COS直流偏置,輸出零磁場(chǎng)時(shí)歸零。

- 增益校準(zhǔn) :校正SIN/COS幅值失衡,使峰峰值一致。

- 正交校準(zhǔn) :修正相位非90°誤差(從±1°→<±0.1°)。

- 非線(xiàn)性校準(zhǔn) :多項(xiàng)式擬合修正AMR固有非線(xiàn)性。

- 存儲(chǔ) :系數(shù)寫(xiě)入 OTP ,永久保存。

- 效果 :基礎(chǔ)INL從±1°優(yōu)化至±0.2°~±0.3°。

2.2 二級(jí):客戶(hù)端勻速自校準(zhǔn)(系統(tǒng)級(jí),用戶(hù)執(zhí)行)

核心功能 :一鍵補(bǔ)償 安裝偏心(0.3mm內(nèi))、氣隙偏差、磁環(huán)缺陷、機(jī)械應(yīng)力 。

2.2.1 觸發(fā)方式(MT68xx)

- 硬件引腳 :`CAL_EN`引腳拉高(MT6835為Pin4)。

- 軟件指令 :SPI寫(xiě)寄存器`0x155 = 0x5E`。

2.2.2 完整操作流程

1. 配置轉(zhuǎn)速區(qū)間

- SPI寫(xiě)`AUTO_CAL_FREQ[2:0]`,8檔可選(25~6400rpm)。

- 默認(rèn) :400~800rpm(通用伺服最優(yōu))。

2. 系統(tǒng)準(zhǔn)備

- 電機(jī)平穩(wěn)勻速運(yùn)轉(zhuǎn), 轉(zhuǎn)速波動(dòng)≤±5% ,無(wú)振動(dòng)干擾。

3. 啟動(dòng)校準(zhǔn)

- 拉高`CAL_EN`,芯片進(jìn)入自校準(zhǔn)模式。

4. 等待完成

- 保持勻速旋轉(zhuǎn) ≥64圈(約6秒) 。

5. 狀態(tài)監(jiān)控

- PWM引腳 :50%=進(jìn)行中,>99%=成功,25%=失敗。

- SPI寄存器 :讀`0x113[7:6]`,`11`=成功。

6. 生效

- 斷電重啟 ,EEPROM參數(shù)加載。

2.2.3 校準(zhǔn)效果(MT68xx)

- MT6835:INL ±0.2° → <±0.07° ?

- MT6826S:INL ±0.3° → <±0.1° ?

- 允許安裝偏心擴(kuò)大至 0.3mm ,降低機(jī)械加工精度要求。

2.3 三級(jí):實(shí)時(shí)動(dòng)態(tài)溫度補(bǔ)償(運(yùn)行級(jí),全自動(dòng))

- 原理 :內(nèi)置NTC實(shí)時(shí)監(jiān)測(cè)結(jié)溫,調(diào)用預(yù)存 全溫域誤差曲線(xiàn) 實(shí)時(shí)修正。

- 補(bǔ)償對(duì)象

1. AMR電橋磁阻溫漂

2. AFE放大器失調(diào)/增益溫漂

3. ADC基準(zhǔn)/增益溫漂

- 效果 :溫度系數(shù) <±0.001°/℃ ?(MT6835),-40℃~125℃全溫域精度波動(dòng)極小。

2.4 校準(zhǔn)算法原理(數(shù)字域)

1. 失調(diào)修正 :`SIN' = SIN - Offset_S`

2. 幅值均衡 :`COS' = COS × Gain_C`

3. 正交校正 :`COS'' = COS' - SIN'·sinε`(ε為正交誤差)

4. 非線(xiàn)性擬合 :高階多項(xiàng)式修正SIN/COS波形畸變

三、系統(tǒng)延時(shí)特性:低延遲與高速穩(wěn)定性

3.1 延時(shí)構(gòu)成(總延時(shí):2~10μs)

1. 模擬鏈路延時(shí) :AFE濾波+ADC采樣 → <1μs ?

2. CORDIC解算延時(shí) :硬件角度計(jì)算 → <2μs ?

3. 校準(zhǔn)補(bǔ)償延時(shí) :數(shù)字修正 → <1μs ?

4. 接口輸出延時(shí) :SPI/ABZ驅(qū)動(dòng) → <1μs ?

3.2 型號(hào)與轉(zhuǎn)速對(duì)應(yīng)延時(shí)

- MT6835 / MT6826S

- 典型延時(shí): 2~6μs (勻速)

- 最高轉(zhuǎn)速: 120,000rpm (無(wú)精度衰減)

- MT6825

- 典型延時(shí): ≤2μs (低延遲優(yōu)化)

- 最高轉(zhuǎn)速: 25,000rpm

3.3 延時(shí)特性工程價(jià)值

- 伺服電流環(huán)匹配 : <10μs ?延時(shí)適配 ?100kHz ?電流環(huán)帶寬。

- 高速無(wú)抖動(dòng) :確定性硬件延時(shí),無(wú)軟件調(diào)度抖動(dòng),高速(>30,000rpm)角度輸出平滑。

- 低速超平滑 :低噪聲+高分辨率,消除電機(jī)“爬行”。

四、多接口兼容性設(shè)計(jì)(工業(yè)全適配)

4.1 支持接口類(lèi)型(MT68xx)

1. SPI(4線(xiàn))

- 時(shí)序:Mode 0/3, 最大10MHz SCLK

- 輸出:15/18/21位絕對(duì)角度+狀態(tài)+CRC

- 應(yīng)用:高速數(shù)字通信、MCU直連

2. ABZ增量

- 分辨率:1~4096線(xiàn)可編程

- 最高頻率:支持120,000rpm(30,000rpm@16384ppr)

- 應(yīng)用:傳統(tǒng)伺服、PLC

3. UVW換相

- 極對(duì)數(shù):1~16對(duì)極可編程

- 應(yīng)用:BLDC電機(jī)無(wú)傳感器換向

4. PWM

- 分辨率:12位,頻率1~10kHz

- 應(yīng)用:低成本模擬替代、簡(jiǎn)單調(diào)速

4.2 電氣兼容性

- 供電 :3.3V~5.0V寬壓, 15~28mA (典型22mA)

- IO :3.3V/5V兼容,推挽/開(kāi)漏可選

- 抗干擾 :CMRR>85dB,ESD±8kV(HBM),工業(yè)級(jí)EMC

4.3 系統(tǒng)級(jí)兼容優(yōu)勢(shì)

- 單芯片多協(xié)議 :同時(shí)輸出SPI+ABZ+UVW, 無(wú)需外接芯片 。

- 即插即用 :直接替代光電編碼器(ABZ), 硬件無(wú)需改板 。

- 長(zhǎng)距離傳輸 :差分信號(hào)(ABZ)支持 10米+ 線(xiàn)纜,抗干擾強(qiáng)。

五、總結(jié):核心技術(shù)亮點(diǎn)與選型啟示

5.1 技術(shù)核心總結(jié)

1. 信號(hào)鏈 : 低噪聲AFE + 同步高精度ADC + 硬件CORDIC ,實(shí)現(xiàn) 微秒級(jí)、低抖動(dòng)、高保真 角度解算。

2. 校準(zhǔn)機(jī)制 : 三級(jí)全維度校準(zhǔn) (出廠(chǎng)+客戶(hù)端+動(dòng)態(tài)溫補(bǔ)),將INL壓縮至 ±0.07° ,兼容 0.3mm 大偏心安裝。

3. 延時(shí) : 確定性2~10μs 延時(shí),完美適配 120,000rpm 超高速伺服。

4. 接口 : SPI/ABZ/UVW/PWM 全兼容,工業(yè)系統(tǒng)無(wú)縫對(duì)接。

5.2 工程選型要點(diǎn)

- 追求極致精度 :選MT6835(21位,INL<±0.07°),必須執(zhí)行 ?客戶(hù)端自校準(zhǔn) ?。

- 工業(yè)通用平衡 :選MT6826S(15位,INL<±0.1°), ?性?xún)r(jià)比+高速+強(qiáng)抗干擾 ?最優(yōu)。

- 低延時(shí)場(chǎng)景 :選MT6825(18位,延時(shí)≤2μs),適合動(dòng)態(tài)響應(yīng)要求高的中低速系統(tǒng)。

審核編輯 黃宇

-

磁編碼器

+關(guān)注

關(guān)注

0文章

133瀏覽量

6688 -

納芯微

+關(guān)注

關(guān)注

3文章

427瀏覽量

16205

發(fā)布評(píng)論請(qǐng)先 登錄

納芯微磁編碼器全角度誤差建模與自適應(yīng)校準(zhǔn)

基于幅度補(bǔ)償與相位校正的磁編碼器高精度校準(zhǔn)技術(shù)

從 ±1° 到 ±0.01°:納芯微霍爾/AMR/TMR 磁編碼器精度體系解析

AMR磁編碼器精度優(yōu)化:納芯微MT68xx系列校準(zhǔn)與信號(hào)鏈設(shè)計(jì)

納芯微 MT 系列磁編碼器工作機(jī)理:AMR 敏感單元、差分信號(hào)調(diào)理與數(shù)字角度解算-艾畢勝電子

納芯微霍爾 & AMR & TMR 磁傳感編碼器核心機(jī)理(技術(shù)深度解析)-艾畢勝電子

納芯微磁編碼器:磁電轉(zhuǎn)換與高精度角度解析原理深度解析

納芯微AMR磁編碼器MT6835/MT6826S:21位高精度角度檢測(cè)技術(shù)-艾畢勝電子

納芯微磁編碼器 SPI 接口硬件接線(xiàn)設(shè)計(jì)

MT6826S 磁性角度編碼器內(nèi)部信號(hào)鏈與 DSP 解算原理

納芯微推出MT6901雙碼道游標(biāo)算法電感編碼器芯片

磁編碼器接口定義及標(biāo)準(zhǔn)接線(xiàn)方法

基于 MT6816 的磁編碼器系統(tǒng)調(diào)試與參數(shù)優(yōu)化

磁編碼器磁鋼–傳感單元–信號(hào)處理鏈路工作機(jī)制

納芯微磁編碼器校準(zhǔn)機(jī)制與信號(hào)鏈設(shè)計(jì):自校準(zhǔn)流程、延時(shí)與多接口兼容性

納芯微磁編碼器校準(zhǔn)機(jī)制與信號(hào)鏈設(shè)計(jì):自校準(zhǔn)流程、延時(shí)與多接口兼容性

評(píng)論