高性能14位2.5 GSPS RF數模轉換器AD9739的深度解析

在電子設計領域,高性能數模轉換器(DAC)是實現數字信號到模擬信號轉換的關鍵組件,對于許多應用如寬帶通信系統、軍事干擾器、儀器儀表以及雷達和航空電子等至關重要。今天,我們就來深入探討一下Analog Devices公司的AD9739這款14位、2.5 GSPS的高性能RF數模轉換器。

文件下載:AD9739.pdf

一、AD9739的關鍵特性

(一)高速合成能力

AD9739具備直接RF合成能力,更新速率高達2.5 GSPS。在基帶模式下,它能覆蓋DC到1.25 GHz的頻率范圍;在混合模式下,頻率范圍可擴展至1.25 GHz到3.0 GHz,為寬帶信號合成提供了強大的支持。

(二)低失真性能

其DAC核心采用了四開關架構,這種架構能夠有效抑制失真,提供卓越的線性性能。在不同頻率下,它都展現出了出色的ACLR(鄰道泄漏比)指標,例如在350 MHz時,ACLR可達80 dBc;在950 MHz時,ACLR為78 dBc;在2100 MHz時,ACLR為69 dBc。

(三)靈活的接口設計

AD9739采用雙端口LVDS數據接口,支持高達1.25 GSPS的操作,并采用源同步DDR時鐘技術,確保數據傳輸的高效性和穩定性。此外,它與AD9739A引腳兼容,方便工程師進行升級和替換。

(四)多芯片同步能力

該轉換器具備多芯片同步能力,通過片上同步控制器,可以實現多個AD9739芯片之間的同步,滿足一些對同步要求較高的應用場景。

(五)可編程輸出電流

輸出電流可在8.7 mA到31.7 mA之間進行編程,為不同的應用需求提供了靈活性。

(六)低功耗設計

在2.5 GSPS的工作速率下,功耗僅為1.16 W,有效降低了系統的整體功耗。

二、技術參數分析

(一)直流參數

AD9739的分辨率為14位,積分非線性(INL)為±1.3 LSB,差分非線性(DNL)為±0.8 LSB,確保了較高的轉換精度。其模擬輸出的增益誤差、滿量程輸出電流、輸出合規范圍等參數也都在合理的范圍內,為系統設計提供了可靠的保障。

(二)LVDS數字參數

LVDS數據輸入和時鐘輸入的各項參數,如輸入共模電壓范圍、邏輯高低差分輸入閾值、接收器差分輸入阻抗等,都符合IEEE標準,保證了數據傳輸的可靠性和穩定性。

(三)交流參數

在動態性能方面,DAC時鐘速率范圍為800到2500 MSPS,調整后的DAC更新速率同樣為800到2500 MSPS。輸出建立時間(tst)到0.1%僅為13 ns,展現出了快速的響應能力。此外,在不同頻率下的無雜散動態范圍(SFDR)、雙音互調失真(IMD)、噪聲譜密度(NSD)以及WCDMA ACLR等指標都表現出色。

(四)絕對最大額定值

AD9739對各種電壓、溫度等參數都有明確的絕對最大額定值限制,在使用過程中必須嚴格遵守這些限制,以確保器件的安全和可靠性。

三、工作原理及功能模塊

(一)整體架構

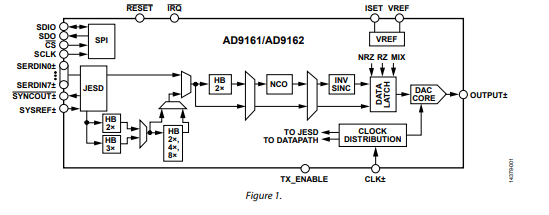

從功能框圖來看,AD9739主要由TxDAC核心、時鐘分布模塊、數據接收器控制器、同步控制器等部分組成。TxDAC核心負責將數字信號轉換為模擬電流輸出,時鐘分布模塊為各個部分提供所需的時鐘信號,數據接收器控制器確保數據的正確接收和處理,同步控制器則用于實現多芯片之間的同步。

(二)LVDS數據端口接口

AD9739支持1.6 GSPS到2.5 GSPS的輸入數據速率,采用雙LVDS數據端口,接口為源同步和雙數據速率(DDR)。主機通過提供嵌入式數據時鐘輸入(DCI),并將數據以交錯的方式輸入到DB0和DB1端口。數據接收器控制器會生成一個與DCI相位偏移90°的內部采樣時鐘,用于對輸入數據進行采樣。

(三)數據接收器控制器

該控制器的主要作用是確保主機和AD9739內部數字時鐘域之間的數據正確交接。它通過一個延遲鎖定環(DLL),使用DCI時鐘輸入的90°相移版本來采樣輸入數據,保證采樣時刻處于數據模式眼圖的中間位置。在初始化時,需要按照一定的步驟進行配置,如設置FINE_DEL_SKEW、禁用和啟用控制器等,以確保其正常工作。

(四)Mu控制器

Mu控制器用于優化AD9739內部數字和模擬域之間的時序,通過一個可編程的延遲線來調整數字時鐘和模擬時鐘之間的相位關系。在初始化時,需要設置相位檢測器、啟用延遲控制器、指定搜索/跟蹤模式和目標相位等參數。一旦鎖定目標相位,Mu控制器會在跟蹤模式下持續調整延遲值,以應對溫度、時間和電源變化等因素帶來的影響。

(五)中斷請求

AD9739可以向主機處理器提供中斷請求輸出信號(IRQ),用于指示一個或多個內部控制器是否達到鎖定或失去鎖定狀態。主機可以通過輪詢IRQ狀態寄存器來確定具體是哪個控制器出現問題,并采取相應的措施。

(六)多設備同步

多個AD9739設備的同步需要確保所有設備具有匹配的流水線延遲。通過一個同步控制器,將主設備的SYNC_OUT信號作為參考時鐘,分發給其他從設備的SYNC_IN輸入,實現多個設備之間的相位對齊。但在同步過程中,需要注意一些限制因素,如時鐘速率較高時,相鄰相位之間的時序裕量會減小,需要特別關注PCB布局和時鐘分布IC的選擇。

四、模擬接口考慮

(一)模擬操作模式

AD9739采用四開關架構,這種架構能夠消除傳統兩開關DAC中存在的代碼相關毛刺,從而降低失真。它支持三種操作模式:正常模式、混合模式和歸零(RZ)模式。通過SPI寄存器可以選擇不同的模式,以滿足不同的應用需求。

(二)時鐘輸入考慮

時鐘源的質量和驅動強度對AD9739的AC性能至關重要。建議使用具有低相位噪聲和低雜散特性的時鐘源,并且時鐘接收器在由LVPECL或CML輸出驅動器驅動時能提供最佳的抖動性能。同時,需要注意時鐘輸入的共模電平調整,以確保最佳的工作狀態。

(三)電壓參考

AD9739的輸出電流由數字控制位和I120參考電流共同決定。在配置電壓參考電路時,需要注意使用10 kΩ電阻和1 nF旁路電容,并且可以通過數字方式調整輸出滿量程電流。

(四)模擬輸出

AD9739提供互補的電流輸出IOUTP和IOUTN,其輸出可以建模為一對直流電流源和一個差分交流電流源。在實際應用中,需要根據具體需求選擇合適的輸出網絡,以實現最佳的性能。

五、實驗室評估與啟動序列

(一)實驗室評估

為了評估AD9739的性能,需要搭建合適的實驗室測試平臺。推薦使用DPG2數據模式發生器作為數據輸入源,使用低相位噪聲/抖動的RF源作為DAC時鐘,使用高動態范圍的頻譜分析儀來測量輸出信號的AC性能。

(二)啟動序列

在AD9739上電后,需要通過SPI端口對其進行初始化和配置。具體的啟動序列包括軟件復位、配置SPI端口、配置Mu控制器、配置數據接收器控制器和同步控制器等步驟。在配置過程中,需要注意各個控制器的鎖定狀態,并根據需要進行相應的調整。

六、總結與思考

AD9739作為一款高性能的RF數模轉換器,具備高速合成、低失真、靈活接口等諸多優點,適用于多種應用場景。但在實際設計過程中,工程師需要充分考慮其各項參數和工作原理,合理配置各個功能模塊,以確保系統的性能和穩定性。同時,對于多設備同步等復雜問題,需要仔細分析和處理,避免出現同步誤差等問題。你在使用AD9739的過程中遇到過哪些挑戰呢?你又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

數模轉換器

+關注

關注

14文章

1481瀏覽量

85927 -

高性能

+關注

關注

0文章

767瀏覽量

21488 -

AD9739

+關注

關注

1文章

5瀏覽量

3214

發布評論請先 登錄

高性能8位210 MSPS TxDAC? D/A轉換器AD9748深度解析

高性能12位210 MSPS TxDAC數模轉換器AD9742深度解析

AD9737A/AD9739A:高性能RF DAC的技術剖析與應用指南

AD9148:高性能四通道16位1GSPS TxDAC+數模轉換器深度解析

AD9146:高性能16位數模轉換器的技術解析與應用指南

深入剖析AD9119/AD9129:高性能RF數模轉換器的卓越之選

深度解析AD9177:高性能RF DAC的卓越之選

AD9213S-CSH:高性能12位、10.25 GSPS RF模數轉換器的技術解析

DAC2932:高性能雙12位數模轉換器的深度解析

DAC5672-EP:高性能14位數模轉換器的深度解析

AD9161/AD9162 11位、12 GSPS、RF數模轉換器技術手冊

高性能14位2.5 GSPS RF數模轉換器AD9739的深度解析

高性能14位2.5 GSPS RF數模轉換器AD9739的深度解析

評論