IDT74SSTVF16859:13 - 位至26 - 位寄存器緩沖器的技術解析

在電子設計領域,一款性能優良的寄存器緩沖器對于整個系統的穩定運行至關重要。今天我們來詳細探討IDT74SSTVF16859這款13 - 位至26 - 位的寄存器緩沖器,看看它有哪些獨特的特性和應用場景。

文件下載:74SSTVF16859NLG.pdf

產品特性

基本特性

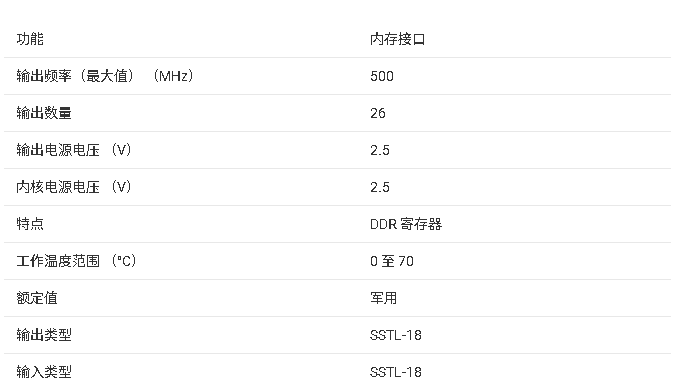

IDT74SSTVF16859是一款1:2的寄存器緩沖器,它完全符合或超越了JEDEC標準SSTVF16859。其工作電壓范圍靈活,對于PC1600、PC2100和PC2700,可在2.3V至2.7V下工作;對于PC3200,則能在2.5V至2.7V下運行。

電氣特性

- 輸入輸出:采用SSTL_2 Class I風格的數據輸入輸出,差分CLK輸入,RESET控制與LVCMOS電平兼容。

- 抗干擾性能:閂鎖性能超過100mA,ESD(靜電放電)防護能力強,按照MIL - STD - 883方法3015測試,ESD大于2000V;采用機器模型((C = 200 pF),(R = 0))測試,ESD大于200V。

封裝形式

該產品提供56引腳的VFQFPN和64引腳的TSSOP兩種封裝形式,方便不同設計需求的選擇。

應用場景

IDT74SSTVF16859與CSPT857C零延遲PLL時鐘緩沖器配合使用,能為DDR1 DIMMs提供完整的解決方案。在DDR1內存模塊的設計中,它可以有效處理數據的緩沖和傳輸,確保數據的穩定和準確。

功能描述

工作原理

SSTVF16859專為PC1600 - PC2700的2.3V - 2.7V VDD和PC3200的2.5V - 2.7V VDD設計,支持低待機操作。所有數據輸入和輸出都與JEDEC標準的SSTL_2電平兼容。

RESET功能

RESET是一個LVCMOS輸入,在電源啟動階段必須可預測地工作。在電源啟動時,RESET必須保持低電平,以確保在施加穩定時鐘之前輸出處于可預測的低電平狀態。當RESET處于低電平時,在施加穩定時鐘之前,它會禁用所有輸入接收器,重置所有寄存器,并強制所有輸出為低電平。當輸入保持低電平且施加穩定時鐘時,在RESET從低到高的轉換期間,輸出將保持低電平。

電氣特性

絕對最大額定值

了解器件的絕對最大額定值對于確保其安全可靠運行至關重要。IDT74SSTVF16859的電源電壓范圍為 - 0.5V至3.6V,輸入電壓范圍為 - 0.5V至VDD + 0.5V,輸出電壓范圍為 - 0.5V至VDDQ + 0.5V等。需要注意的是,超過這些額定值可能會對器件造成永久性損壞。

DC電氣特性

對于PC1600 - PC2700和PC3200,文檔分別給出了不同的DC電氣特性參數。包括控制輸入的電壓、輸出的高低電平電壓、輸入電流、靜態和動態工作電流以及輸入電容等。例如,在PC1600 - PC2700的工作條件下,當VDD = 2.3V,II = - 18mA時,控制輸入的V IK最大為 - 1.2V。

工作特性

在(TA = 25^{circ}C)的條件下,給出了電源電壓、參考電壓、終止電壓、輸入電壓等參數的范圍。例如,對于PC1600 - PC2700,參考電壓V REF在1.15V至1.35V之間。

時序要求

不同的內存標準(PC1600 - PC2700和PC3200)有不同的時序要求。包括時鐘頻率、脈沖持續時間、差分輸入的激活和非激活時間、建立時間和保持時間等。例如,PC1600 - PC2700的時鐘頻率最大為200MHz,PC3200的時鐘頻率最大為220MHz。

開關特性

開關特性參數如最大頻率、CLK和CLK到Q的傳播延遲等也有明確規定。例如,PC1600 - PC2700的f MAX為200MHz,PC3200的f MAX為220MHz。

測試電路和訂購信息

文檔還提供了測試電路和波形圖,以及詳細的訂購信息。測試電路中的負載電路、電壓和電流波形圖等有助于工程師進行實際的測試和驗證。訂購信息則明確了不同封裝和工藝的產品型號,方便工程師根據需求進行選擇。

總結

IDT74SSTVF16859是一款功能強大、性能穩定的寄存器緩沖器,適用于DDR1 DIMMs等應用場景。通過對其特性、功能、電氣特性等方面的了解,工程師可以更好地將其應用到實際設計中。在使用過程中,一定要嚴格遵守其額定值和時序要求,以確保系統的穩定運行。你在使用類似寄存器緩沖器時遇到過哪些問題呢?歡迎在評論區分享你的經驗。

發布評論請先 登錄

IDT74SSTVF16859:13 - 位至26 - 位寄存器緩沖器的技術解析

IDT74SSTVF16859:13 - 位至26 - 位寄存器緩沖器的技術解析

評論