在當今的電子設計領域,高性能模數轉換器(ADC)的需求日益增長。TI的ADS62C15作為一款雙通道11位、125 MSPS的ADC,憑借其出色的性能和豐富的特性,在眾多應用場景中展現出了強大的競爭力。今天,我們就來深入探討一下這款ADC的特點、工作原理以及應用注意事項。

文件下載:ads62c15.pdf

產品特性概覽

ADS62C15具有一系列令人矚目的特性,使其在同類產品中脫穎而出。

高采樣率與分辨率

- 最高采樣率可達125 MSPS,能夠滿足高速信號采集的需求。

- 11位分辨率且無失碼,保證了數據的準確性和完整性。

出色的信號性能

- 在Fin = 117 MHz時,SFDR可達82 dBc,SNR可達67 dBFS;使用SNRBoost技術,在20MHz帶寬下,SNR可提升至77.5 dBFS。

- 串擾低至92 dB,有效減少通道間的干擾。

靈活的輸出與增益選項

強大的數字處理功能

- 內置數字處理模塊,支持偏移校正、細增益校正、2/4/8抽取以及自定義可編程24抽頭低/高/帶通濾波器。

廣泛的時鐘兼容性

- 支持Sine、LVPECL、LVDS和LVCMOS時鐘,幅度低至400 mVPP。

- 具備時鐘占空比穩定器,確保時鐘信號的穩定性。

其他特性

- 內置參考,也支持外部參考。

- 采用64-QFN封裝(9mm × 9mm),體積小巧。

工作原理剖析

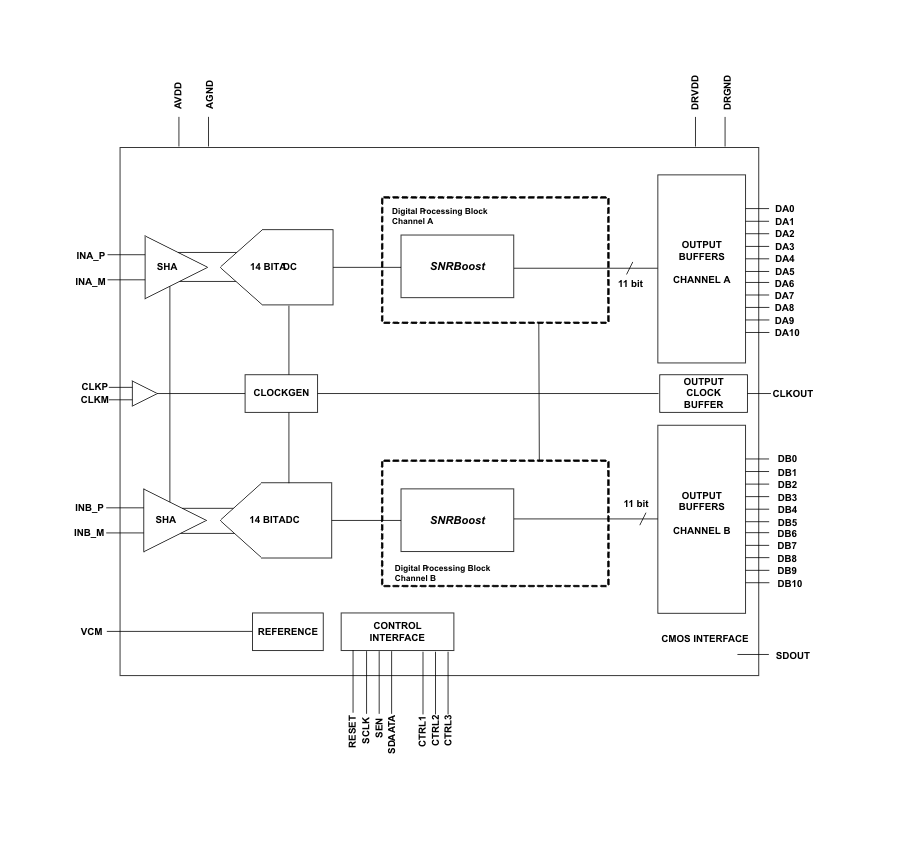

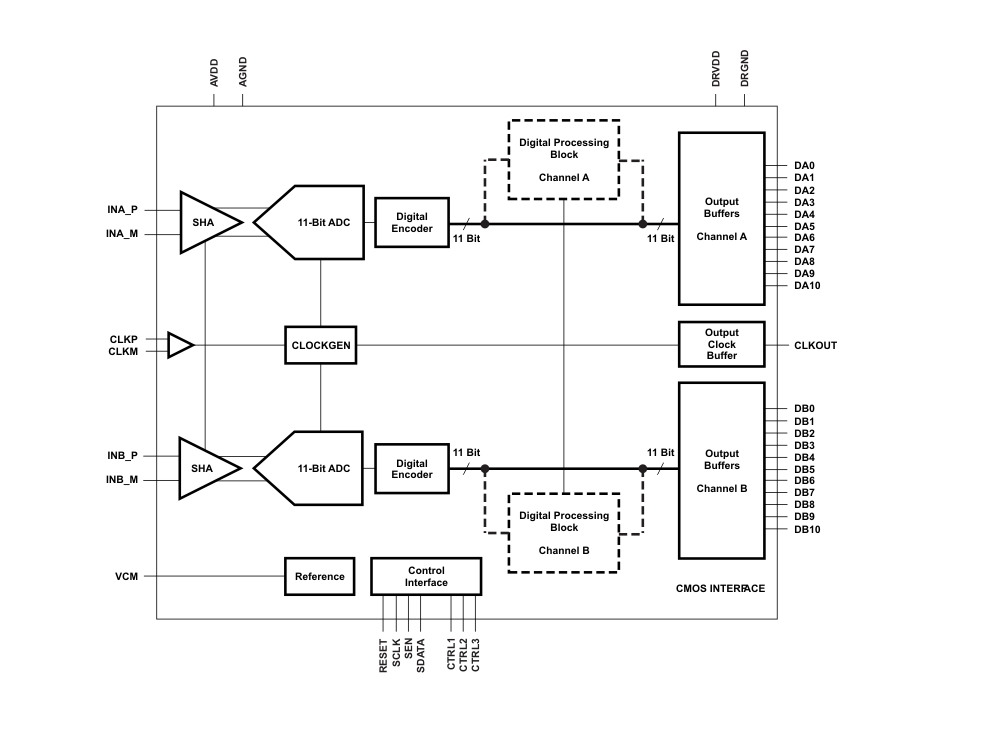

ADS62C15采用CMOS工藝和開關電容技術,是一款低功耗的11位雙通道流水線ADC。其轉換過程由外部輸入時鐘的上升沿觸發,信號被輸入采樣保持電路捕獲后,通過一系列小分辨率級依次轉換,輸出在數字校正邏輯塊中組合。每個時鐘沿,樣本在流水線中傳播,產生14個時鐘周期的數據延遲。輸出為11位數據,可采用DDR LVDS或CMOS格式,編碼方式為直偏移二進制或二進制補碼。

關鍵參數解讀

電氣特性

- 模擬輸入:差分輸入電壓范圍為2 VPP,輸入電阻大于1 MΩ,電容為7 pF,帶寬達450 MHz。

- 電源:模擬電源電流(AVDD)典型值為216 mA,不同輸出模式和負載下的總功耗有所差異。

- 直流精度:無失碼,DNL在±0.4 LSB以內,INL在±1 LSB以內,偏移誤差在±3 mV以內。

- 信號性能:不同輸入頻率下,SNR、SINAD、ENOB、SFDR等指標表現出色,且增益設置會對性能產生影響。

數字特性

- 數字輸入:高電平輸入電壓為2.4 V,低電平輸入電壓為0.8 V。

- 數字輸出:CMOS模式下,高電平輸出電壓為DRVDD,低電平輸出電壓為0 V;LVDS模式下,高電平輸出電壓為1375 mV,低電平輸出電壓為1025 mV。

時序特性

- 孔徑延遲典型值為1.8 ns,孔徑抖動為130 fs rms。

- 不同模式下的數據建立時間、保持時間、時鐘傳播延遲等時序參數各有不同。

配置與編程

ADS62C15可以通過并行接口控制、串行接口編程或兩者結合的方式進行配置。

并行接口控制

將RESET引腳接高電平(AVDD),SEN、SCLK、CTRL1、CTRL2和CTRL3引腳可直接控制ADC的某些模式。

串行接口編程

將RESET引腳置低,SEN、SDATA和SCLK引腳作為串行接口數字引腳,用于訪問ADC的內部寄存器。寄存器需先復位到默認值,可通過硬件復位(在RESET引腳施加高脈沖)或軟件復位(設置位 = 1)實現。

串行接口時序

SCLK頻率范圍為DC至20 MHz,SEN到SCLK的建立時間和保持時間均為25 ns,SDATA的建立時間和保持時間也為25 ns。

應用注意事項

模擬輸入

- 采用基于開關電容的差分采樣保持架構,INP和INM引腳需外部偏置在VCM引腳提供的1.5 V共模電壓附近。

- 為獲得最佳性能,模擬輸入應采用差分驅動,推薦在每個輸入引腳串聯一個<5 Ω的電阻,以抑制封裝寄生效應引起的振鈴。

- 可使用RF變壓器或差分放大器作為驅動電路,具體選擇取決于輸入頻率和應用需求。

參考

- 內置內部參考REFP和REFM,無需外部組件。

- 可通過編程串行接口寄存器位(REF)選擇內部或外部參考模式。在外部參考模式下,VCM引腳作為參考輸入,輸入電壓經內部緩沖和增益后生成REFP和REFM電壓。

SNRBoost技術

- 可克服量化噪聲導致的SNR限制,在小于Nyquist頻率(Fs/2)的任何帶寬內實現SNR提升。

- 通過選擇合適的SNRBoost系數,可將噪聲底的“浴盆”形狀定位在所需信號頻段內。

- 啟用該模式后,ADC延遲增加一個時鐘周期至15個時鐘周期。

時鐘輸入

- 時鐘輸入可采用差分(SINE、LVPECL或LVDS)或單端(LVCMOS)驅動方式,性能差異不大。

- 為獲得最佳性能,推薦采用差分驅動,并使用低抖動的時鐘源。

電源管理

- 具備全局電源關斷、通道待機和通道輸出緩沖器禁用三種電源管理模式,可通過串行寄存器位或控制引腳CTRL1至CTRL3設置。

- 電源上電時,AVDD和DRVDD的上電順序無要求,可使用單獨的電源或從單個電源派生。

輸出接口

- 并行CMOS接口:輸出緩沖器電源(DRVDD)可在1.8 V至3.3 V范圍內工作。建議使用CMOS輸出時鐘(CLKOUT)鎖存數據,并盡量減小數據和時鐘輸出引腳的負載電容。

- DDR LVDS接口:僅支持3.3 V DRVDD電源,11位數據和輸出時鐘以LVDS電平輸出。LVDS緩沖器電流可編程,且具備內部終端選項,可提高信號完整性。

數字處理塊

- 偏移校正:可通過串行寄存器位(OFFSET LOOP EN)啟用內部偏移校正算法,校正直流偏移至±10mV。校正時間常數可通過寄存器位(OFFSET LOOP TC)控制。

- 增益校正:可通過寄存器位(GAIN CORRECTION)對ADC通道增益進行精細校正,校正步長為0.05 dB,最大校正值為0.5 dB。

- 抽取濾波器:可對ADC輸出數據進行抽取,并選擇內置低通、高通或帶通濾波器。抽取率和濾波器類型可通過寄存器位(DECIMATION RATE)和(DECIMATION FILTER TYPE)選擇。

電路板設計要點

接地

使用單一接地平面,確保電路板的模擬、數字和時鐘部分分區清晰。

電源去耦

由于ADS62C15內部已包含去耦電容,外部去耦電容可適當減少。去耦電容應靠近轉換器電源引腳放置,推薦為模擬和數字電源引腳使用單獨的電源。

散熱

將封裝底部的暴露焊盤焊接到接地平面,以獲得最佳散熱性能。

總結

ADS62C15以其高性能、靈活性和豐富的功能,為電子工程師在無線通信、軟件定義無線電、醫療成像等領域的設計提供了強大的支持。在實際應用中,我們需要根據具體需求合理配置和使用該ADC,并注意電路板設計和信號處理等方面的細節,以充分發揮其性能優勢。希望通過本文的介紹,能幫助大家更好地理解和應用ADS62C15。你在使用類似ADC的過程中遇到過哪些問題呢?歡迎在評論區分享交流。

-

接口

+關注

關注

33文章

9519瀏覽量

157020 -

adc

+關注

關注

100文章

7511瀏覽量

555929 -

模數轉換器

+關注

關注

26文章

4013瀏覽量

130100 -

帶通濾波器

+關注

關注

18文章

269瀏覽量

44697

發布評論請先 登錄

高性能DAC與ADC轉換技術

TI推出業界最快速的雙通道14位元ADC -ADS62P49

雙通道11位125MSPS模數轉換器ADS62P15的詳細資料概述

ADS62P2X系列具有具有DDR LVDSMCOS輸出的雙通道12位的ADC的資料概述

ADS62C17雙通道、11位、200 MSPS模數轉換器數據表

ADS58C28雙通道、11位模數轉換器(ADC)數據表

ADS5553高性能、雙通道、14位、65 MSPS模數轉換器(ADC)數據表

ADS62PF49 雙通道反饋接收器產品總結

ADS62C17 雙通道 11 位 200MSPS 高速模數轉換器(ADC)產品手冊總結

?ADS62P2X 系列雙通道12位ADC數據手冊總結

ADS62P42 雙通道,14位,65 MSPS 的模擬轉數字轉換器(ADC)技術手冊

ADS62C15:高性能雙通道11位ADC的深度解析

ADS62C15:高性能雙通道11位ADC的深度解析

評論