高速低功耗ADC:AD7273/AD7274的技術(shù)剖析與應用指南

在電子設計領域,模數(shù)轉(zhuǎn)換器(ADC)是連接模擬世界和數(shù)字世界的關(guān)鍵橋梁。今天,我們來深入了解Analog Devices推出的兩款高性能ADC——AD7273和AD7274,它們在高速、低功耗方面表現(xiàn)出色,能滿足眾多應用場景的需求。

文件下載:AD7273.pdf

產(chǎn)品概述

AD7273和AD7274分別是10位和12位的高速、低功耗逐次逼近型ADC。它們采用單電源供電,電壓范圍為2.35V至3.6V,最高吞吐量可達3 MSPS。這兩款ADC內(nèi)部集成了低噪聲、寬帶寬的跟蹤保持放大器,能夠處理超過55 MHz的輸入頻率。

主要特性

- 高吞吐量與低功耗:在3 MSPS的吞吐量下,3V供電時功耗僅為11.4 mW,有效平衡了性能與功耗。

- 寬輸入帶寬:在1 MHz輸入頻率下,SNR可達70 dB,保證了信號轉(zhuǎn)換的質(zhì)量。

- 靈活的電源/串行時鐘速度管理:可根據(jù)實際需求調(diào)整,在低吞吐量時實現(xiàn)最大的電源效率。

- 無流水線延遲:確保數(shù)據(jù)實時處理,提高系統(tǒng)響應速度。

- 高速串行接口:兼容SPI?、QSPI?、MICROWIRE?和DSP,方便與各種微處理器或DSP進行接口。

- 寬溫度范圍:工作溫度范圍為 -40°C至 +125°C,適應不同的應用環(huán)境。

- 低功耗模式:掉電模式下典型電流僅為0.1 μA,進一步降低功耗。

- 小巧封裝:提供8引腳TSOT和8引腳MSOP兩種封裝,節(jié)省電路板空間。

技術(shù)規(guī)格

動態(tài)性能

在1 MHz正弦波輸入下,AD7274的信號噪聲失真比(SINAD)最小為68 dB,信噪比(SNR)為69.5 dB,總諧波失真(THD)最大為 -78 dB;AD7273的SINAD最小為61 dB,THD最大為 -72 dB。這些指標表明它們在處理高頻信號時具有良好的性能。

直流精度

兩款ADC的積分非線性(INL)和微分非線性(DNL)都控制在較小范圍內(nèi),保證了轉(zhuǎn)換結(jié)果的準確性。AD7274的INL最大為±1 LSB,DNL最大為±1 LSB;AD7273的INL最大為±0.5 LSB,DNL最大為±0.5 LSB。

模擬輸入

輸入電壓范圍為0至VREF,直流泄漏電流在不同溫度范圍內(nèi)有所不同。在 -40°C至 +85°C時,最大為±1 μA;在85°C至125°C時,最大為±5.5 μA。

參考輸入

外部參考電壓范圍為1.4 V至VDD,輸入電容在跟蹤模式下典型值為42 pF,保持模式下典型值為10 pF。

邏輯輸入輸出

邏輯輸入高電壓(VINH)和低電壓(VINL)根據(jù)電源電壓不同有所變化,輸入電流最大為±1 μA,輸入電容最大為2 pF。邏輯輸出高電壓(VOH)最小為VDD - 0.2 V,低電壓(VOL)最大為0.2 V。

轉(zhuǎn)換速率

AD7274的轉(zhuǎn)換時間最大為291 ns(14個SCLK周期,SCLK為48 MHz),AD7273的轉(zhuǎn)換時間最大為250 ns(12個SCLK周期,SCLK為48 MHz)。兩款ADC的最大吞吐量均可達3 MSPS。

電源要求

電源電壓范圍為2.35/3.6 V(最小/最大),正常模式下靜態(tài)電流和工作電流根據(jù)不同條件有所差異。部分掉電模式和完全掉電模式下的電流更小,以實現(xiàn)低功耗。

工作原理

AD7273/AD7274基于電荷再分配DAC的逐次逼近型ADC。在采集階段,采樣電容獲取輸入信號;轉(zhuǎn)換開始時,通過控制邏輯和電荷再分配DAC調(diào)整采樣電容上的電荷量,使比較器重新平衡,完成轉(zhuǎn)換。

操作模式

正常模式

適用于需要最快吞吐量的應用。在此模式下,AD7273/AD7274始終保持全功率運行,無需擔心上電時間。轉(zhuǎn)換在CS信號的下降沿啟動,為確保始終全功率運行,CS必須在下降沿后至少10個SCLK下降沿保持低電平。

部分掉電模式

適用于對吞吐量要求較低的應用。通過在SCLK的第二個和第10個下降沿之間將CS置高,可進入部分掉電模式,此時除偏置生成電路外,所有模擬電路均斷電。退出此模式需進行一次虛擬轉(zhuǎn)換。

完全掉電模式

適用于吞吐量要求更低的應用。先進入部分掉電模式,然后在下次轉(zhuǎn)換周期中,在第10個SCLK下降沿之前將CS置高,即可進入完全掉電模式。退出時同樣需要進行虛擬轉(zhuǎn)換,并等待約1 μs的上電時間。

串行接口

串行時鐘(SCLK)提供轉(zhuǎn)換時鐘并控制數(shù)據(jù)傳輸。CS信號啟動數(shù)據(jù)傳輸和轉(zhuǎn)換過程,下降沿將跟蹤保持器置于保持模式并使總線退出三態(tài),同時采樣模擬輸入并啟動轉(zhuǎn)換。

對于AD7274,完成轉(zhuǎn)換需要14個SCLK周期;對于AD7273,需要12個SCLK周期。如果在規(guī)定的SCLK周期數(shù)之前CS上升,轉(zhuǎn)換將終止,SDATA線返回三態(tài)。

應用提示

接地與布局

PCB設計應將模擬和數(shù)字部分分開,使用接地平面進行屏蔽。所有AGND引腳應連接到AGND平面,數(shù)字和模擬接地平面應在一處連接。避免在器件下方鋪設數(shù)字線路,電源線路應使用大走線以降低阻抗。

性能評估

推薦使用評估板進行性能評估,評估板配套軟件可進行交流(快速傅里葉變換)和直流(代碼直方圖)測試。

訂購指南

AD7273和AD7274提供多種型號和封裝選項,可根據(jù)溫度范圍、線性誤差和封裝類型進行選擇。此外,還提供評估板和控制板,方便進行開發(fā)和測試。

綜上所述,AD7273/AD7274以其高速、低功耗、靈活的操作模式和良好的性能,為電子工程師在設計中提供了優(yōu)秀的選擇。在實際應用中,合理選擇操作模式和優(yōu)化布局,能夠充分發(fā)揮它們的優(yōu)勢,滿足不同應用場景的需求。你在使用類似ADC時遇到過哪些問題呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

ad7273

+關(guān)注

關(guān)注

0文章

2瀏覽量

1126

發(fā)布評論請先 登錄

低功耗 10 位 ADC——MAX192 的深度剖析與應用

12 位高速 ADC AD9432:性能剖析與應用指南

MAX1183:高性能低功耗雙路10位ADC的技術(shù)剖析

低功耗高速ADC:AD7466/AD7467/AD7468的技術(shù)解析與應用指南

12 位高速 ADC:AD9634 深度剖析與應用指南

16位低功耗PulSAR ADC:AD7988-1/AD7988-5的技術(shù)剖析與應用指南

AD7768 - 1:高精度ADC的技術(shù)深度剖析與應用指南

AD4884:高性能雙通道16位SAR ADC的技術(shù)剖析與應用指南

AD4129 - 8:超低功耗16位Sigma - Delta ADC的技術(shù)解析與應用指南

STM32L071xx:超低功耗32位MCU的技術(shù)剖析與應用指南

SGM51610C:超小型低功耗16位ADC的技術(shù)剖析與應用指南

SGM58201:4通道、2kSPS、低功耗24位ADC的技術(shù)剖析與應用指南

SGM5208-14/SGM5209-14:低功耗14位ADC的技術(shù)剖析與應用指南

高速低功耗運放LTC6253 - 7:性能剖析與應用指南

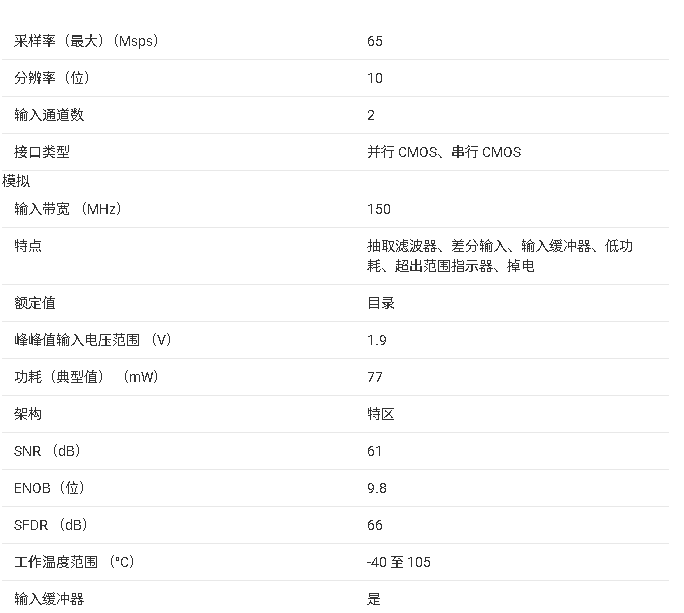

ADC3910D065 10 位高速低功耗 ADC 技術(shù)文檔總結(jié)

高速低功耗ADC:AD7273/AD7274的技術(shù)剖析與應用指南

高速低功耗ADC:AD7273/AD7274的技術(shù)剖析與應用指南

評論