近日,奕行智能宣布其論文《Dynamic Scheduling for AI Accelerators via TISA》(基于 Tile 級虛擬指令集實現 AI 加速器的動態調度)正式入選 ISCA 2026(International Symposium on Computer Architecture,國際計算機體系結構年會)。

ISCA 創立于 1973 年,是計算機體系結構領域最權威的學術會議之一,與 MICRO、HPCA 并稱"三大頂會"。谷歌 TPU 初代架構論文(ISCA 2017)發布于此,歷屆論文見證了算力架構從指令集變革到異構計算的每一次關鍵演進。

算力競爭范式轉移,動態調度恰逢其時

AI 算力競爭正從"誰算得更快"轉向"誰算得更省"。推理場景爆發后,Token 成本成為 AI 基礎設施商業價值的核心指標,提升算力利用率與能效已是決勝關鍵。

現有 AI 加速器普遍依賴傳統靜態調度:執行策略往往在編譯期一次性固化,無法響應運行時動態變化。隨著模型規模擴大,編譯復雜度高、硬件行為適配難、運行時變化導致流水線空泡,硬件潛能被浪費。奕行智能此次入選 ISCA 的論文,正是對這一行業痛點的系統性解答。

三位一體閉環,重新定義動態調度

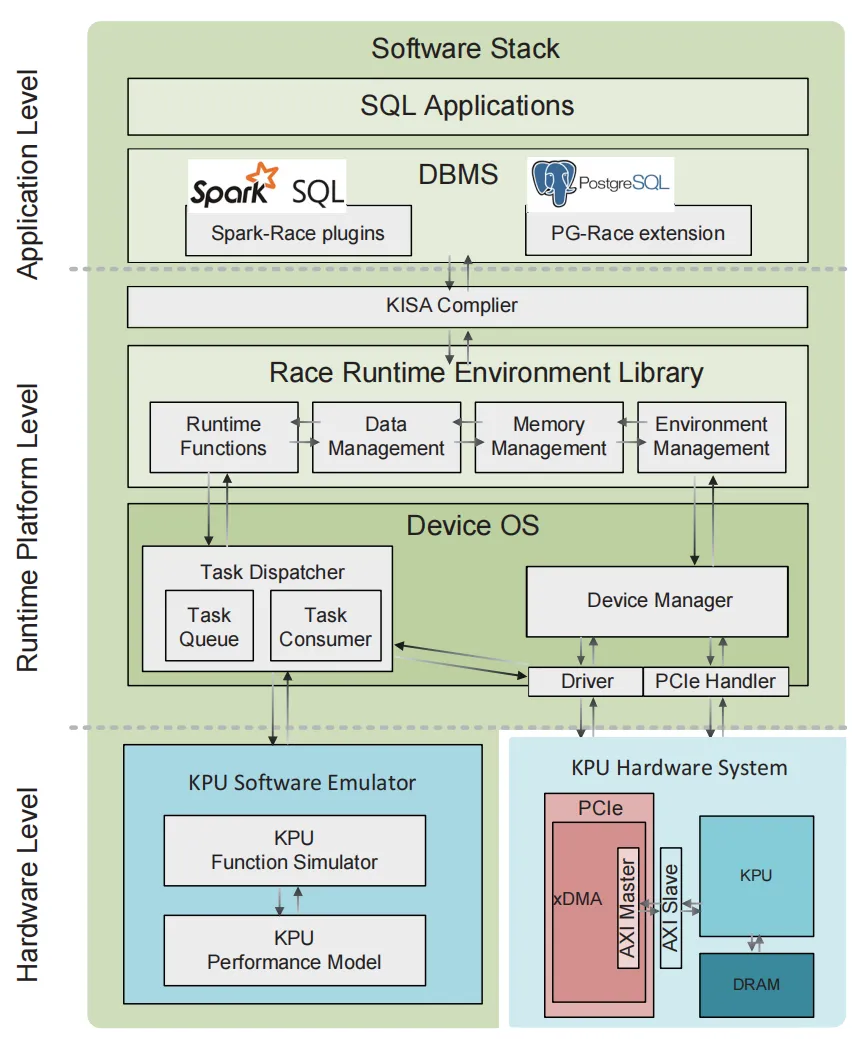

奕行智能入選頂會ISCA的論文,圍繞其獨家打造的 Tile 級動態調度架構展開,通過"虛擬指令+ 智能編譯器 + 硬件調度器"的三位一體閉環,將復雜的指令依賴、流水線管理和內存切分全部交由硬件自動完成,從根本上打破靜態優化的性能上限,也讓上層開發像"拼積木"一樣干凈簡潔。

具體而言,架構由三個核心組件協同構成:Tile 級虛擬指令集(VISA)在硬件底層與上層軟件生態之間架起統一接口,智能編譯器ACE 自動處理指令映射與優化,VISA 調度器則在硬件層實時感知運行狀態,動態平衡Tile 執行與資源分配,將算力利用率推向極限。三者協同,將"一次性規劃"升級為"運行時持續尋優",讓硬件并行潛能得到更充分的釋放。

數據說話:多模型全面驗證

論文在DeepSeek-R1、ResNet-50、BERT、GPT-J、LLaMA2 及 FlashAttention-3 等主流大模型與視覺模型上進行系統評測,結果表明:

- 相較基線方案,整體加速比達1.52–1.92×;

- 優于強靜態流水調度方案1.14–1.63×;

- FlashAttention-3 場景下,硬件利用率提升 +26.4%。

多平臺、多模型的評測結果充分驗證了動態調度架構的廣泛適用性與穩定優勢。

此次入選ISCA 2026,是國際頂級學術界對奕行智能技術原創性的有力認可。從語義感知編譯到運行時動態尋優,從打破靜態天花板到充分釋放硬件潛能,TISA 框架指向 AI 加速器架構創新的下一個范式。

-

加速器

+關注

關注

2文章

841瀏覽量

40205 -

AI

+關注

關注

91文章

40651瀏覽量

302307

發布評論請先 登錄

傳音相關研究成果入選計算機視覺頂會CVPR 2026

理想汽車馬赫100芯片論文入選ISCA 2026

地平線11篇論文強勢入選CVPR 2026

奕斯偉計算攜RISC-V創新成果亮相Embedded World 2026

由順序主導的計算機體系

后摩智能4篇論文入選人工智能頂會ICLR 2026

MediaTek多篇論文入選全球前沿國際學術會議

易控智駕榮獲計算機視覺頂會CVPR 2025認可

思必馳與上海交大聯合實驗室研究成果入選兩大頂級會議

后摩智能與高校合作研究成果榮獲ISCA 2025最佳論文獎

理想汽車八篇論文入選ICCV 2025

DPU核心技術論文再次登陸體系結構領域旗艦期刊《IEEE Transactions on Computers》

奕行智能論文入選國際計算機體系結構頂級會議 ISCA 2026

奕行智能論文入選國際計算機體系結構頂級會議 ISCA 2026

評論