AD4857:8通道同步采樣16位數(shù)據(jù)采集系統(tǒng)的剖析

在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)采集系統(tǒng)(DAS)是許多應(yīng)用的核心組件,其性能直接影響整個(gè)系統(tǒng)的精度和可靠性。AD4857作為一款功能強(qiáng)大的DAS,憑借其獨(dú)特的特性和多樣的應(yīng)用場(chǎng)景,在市場(chǎng)上占據(jù)了重要的地位。本文將深入剖析AD4857的各項(xiàng)特性、工作原理、應(yīng)用信息以及寄存器配置,為電子工程師在實(shí)際設(shè)計(jì)中提供全面的參考。

文件下載:AD4857.pdf

1. AD4857概述

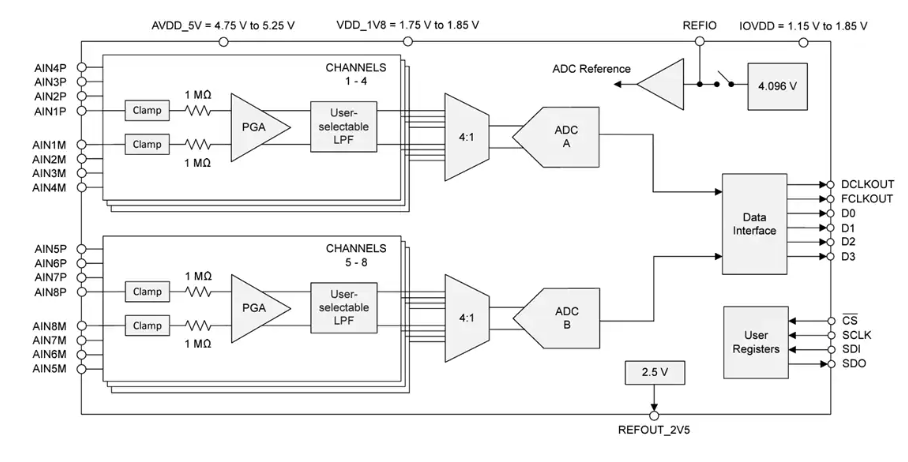

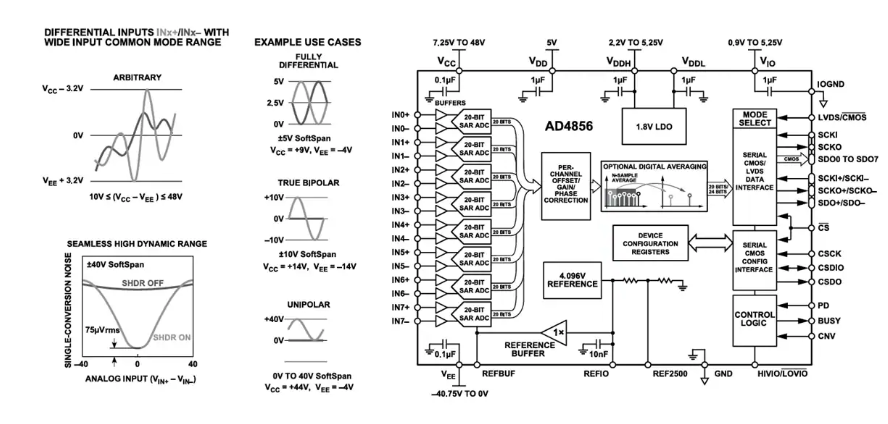

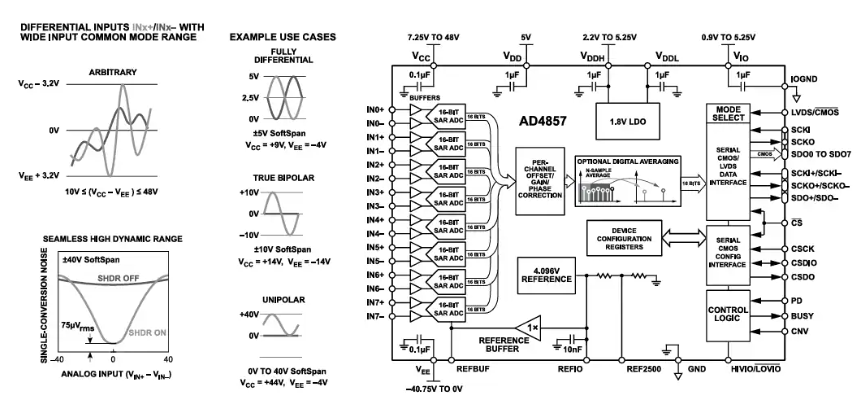

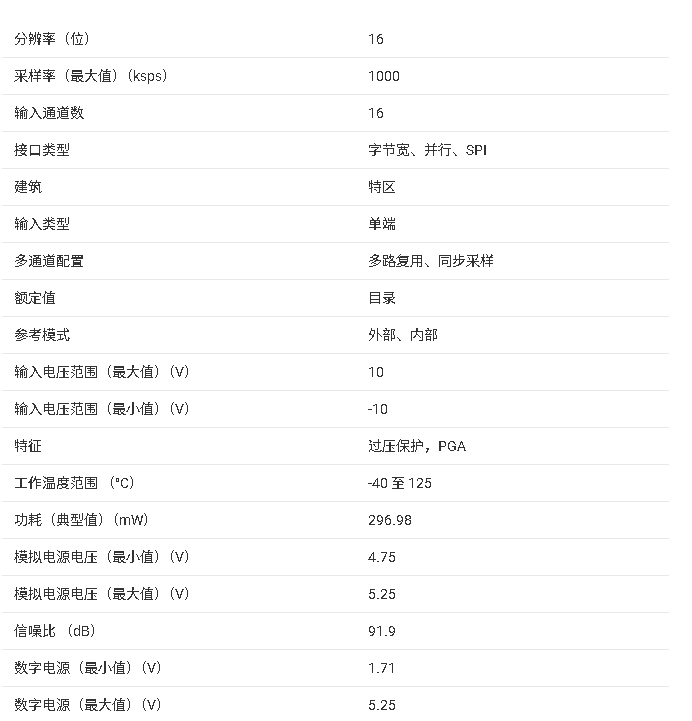

AD4857是一款全緩沖、8通道同步采樣、16位、1 MSPS的數(shù)據(jù)采集系統(tǒng),具備差分、寬共模范圍輸入的特點(diǎn)。它采用5V低壓電源、靈活的輸入緩沖電源以及精密低漂移的內(nèi)部參考和參考緩沖器,允許每個(gè)通道的SoftSpan范圍獨(dú)立配置,以匹配原生應(yīng)用信號(hào)的擺動(dòng),從而減少額外的外部信號(hào)調(diào)理。

1.1 主要特性

- 完整的16位數(shù)據(jù)采集系統(tǒng):能夠同時(shí)對(duì)8個(gè)內(nèi)部緩沖通道進(jìn)行采樣,每個(gè)通道的吞吐量可達(dá)1 MSPS。

- 差分、寬共模范圍輸入:在25°C時(shí),典型輸入泄漏電流僅為±75 pA,輸入信號(hào)靈活性高。

- 高動(dòng)態(tài)范圍:采用無縫高動(dòng)態(tài)范圍(SHDR)技術(shù),在啟用時(shí)可自動(dòng)優(yōu)化通道的輸入信號(hào)路徑增益,在不影響線性度的情況下,最小化每個(gè)樣本的轉(zhuǎn)換器噪聲。

- 低功耗:在1 MSPS的采樣率下,每個(gè)通道的功耗約為45 mW,且功耗隨吞吐量而變化。

- 數(shù)字靈活性:支持SPI CMOS(0.9 V至5.25 V)和LVDS串行輸入輸出,還可選擇16位數(shù)字平均的過采樣功能,以及可選的偏移、增益和相位校正。

1.2 應(yīng)用場(chǎng)景

AD4857適用于多種領(lǐng)域,包括自動(dòng)測(cè)試設(shè)備、航空航天、儀器儀表和控制系統(tǒng)、半導(dǎo)體制造以及測(cè)試測(cè)量等。

2. 工作原理

2.1 轉(zhuǎn)換器操作

AD4857的工作分為兩個(gè)階段:采集階段和轉(zhuǎn)換階段。在采集階段,每個(gè)通道的采樣保持電路中的采樣電容連接到各自的模擬輸入緩沖器,跟蹤差分輸入電壓。當(dāng)CNV引腳出現(xiàn)上升沿時(shí),所有采樣保持電路從跟蹤模式轉(zhuǎn)換到保持模式,同時(shí)對(duì)所有通道的輸入信號(hào)進(jìn)行采樣并啟動(dòng)轉(zhuǎn)換。在轉(zhuǎn)換階段,每個(gè)通道的采樣電容連接到一個(gè)16位電荷再分配電容數(shù)模轉(zhuǎn)換器(CDAC),通過逐次逼近算法,將采樣的輸入電壓與通道SoftSpan滿量程范圍的二進(jìn)制加權(quán)分?jǐn)?shù)進(jìn)行比較,最終輸出近似于每個(gè)通道采樣模擬輸入的數(shù)字代碼。

2.2 傳輸函數(shù)

AD4857將每個(gè)通道的滿量程電壓范圍數(shù)字化為 (2^{16}) 個(gè)離散電平。結(jié)合ADC主參考電壓REFBUF,每個(gè)通道的SoftSpan配置決定了其差分輸入電壓范圍、LSB大小和轉(zhuǎn)換結(jié)果的二進(jìn)制格式。轉(zhuǎn)換結(jié)果在所有雙極性SoftSpan范圍中以二進(jìn)制補(bǔ)碼格式輸出,在所有單極性SoftSpan范圍中以直二進(jìn)制格式輸出。

2.3 SoftSpan

每個(gè)通道可以獨(dú)立配置為16種SoftSpan范圍之一,用戶可根據(jù)所需的差分模擬輸入范圍選擇合適的SoftSpan范圍。默認(rèn)情況下,所有通道均為SoftSpan 15,對(duì)應(yīng)標(biāo)稱的±40 V雙極性輸入跨度。通過向相應(yīng)的寄存器地址寫入4位SoftSpan代碼,即可配置通道的不同范圍。

2.4 無縫高動(dòng)態(tài)范圍(SHDR)

SHDR是一種專有技術(shù),可在每個(gè)樣本的基礎(chǔ)上提供盡可能低的輸入?yún)⒖嫁D(zhuǎn)換噪聲。當(dāng)SHDR禁用時(shí),每個(gè)通道的SoftSpan范圍自動(dòng)定義一個(gè)固定的轉(zhuǎn)換器模擬信號(hào)增益,應(yīng)用于該通道的每個(gè)樣本。啟用SHDR后,轉(zhuǎn)換器根據(jù)每個(gè)樣本的差分電壓動(dòng)態(tài)調(diào)整模擬信號(hào)增益,對(duì)于接近所選SoftSpan范圍最大值的差分電壓,采用與SHDR禁用時(shí)相同的增益;對(duì)于幅值較低的樣本,轉(zhuǎn)換器自動(dòng)增加增益,從而降低這些樣本的輸入?yún)⒖嫁D(zhuǎn)換噪聲,提高動(dòng)態(tài)范圍。

2.5 數(shù)字處理特性

AD4857支持多種數(shù)字?jǐn)?shù)據(jù)后處理功能,包括過采樣、偏移、增益和相位校正。這些功能可通過控制寄存器進(jìn)行配置。

- 過采樣模式:默認(rèn)情況下,AD4857工作在非過采樣模式。啟用過采樣模式后,AD4857會(huì)對(duì)每個(gè)通道的多個(gè)轉(zhuǎn)換結(jié)果進(jìn)行數(shù)字平均,適用于需要更低噪聲和更高動(dòng)態(tài)范圍的應(yīng)用。

- 數(shù)字偏移校正:每個(gè)通道可以獨(dú)立編程,為每個(gè)轉(zhuǎn)換結(jié)果添加一個(gè)16位有符號(hào)數(shù)字偏移校正值,用于校正DAS模擬輸入上游的固定偏移誤差。

- 數(shù)字增益校正:每個(gè)通道可以獨(dú)立編程,為每個(gè)轉(zhuǎn)換結(jié)果應(yīng)用一個(gè)數(shù)字增益校正因子,用于校正DAS模擬輸入上游的固定增益誤差。

- 數(shù)字相位校正:在過采樣模式下,每個(gè)通道可以獨(dú)立編程,對(duì)過采樣的數(shù)字平均值應(yīng)用一個(gè)數(shù)字相位校正項(xiàng),用于補(bǔ)償DAS模擬輸入上游的相位誤差。

- 通道過范圍和欠范圍限制:每個(gè)通道的每個(gè)轉(zhuǎn)換結(jié)果都會(huì)與16位有符號(hào)的過范圍和欠范圍限制進(jìn)行比較,如果檢測(cè)到任何超出范圍的轉(zhuǎn)換結(jié)果,相應(yīng)的標(biāo)志位將在CH_OR_STATUS寄存器或CH_UR_STATUS寄存器中設(shè)置。

3. 應(yīng)用信息

3.1 緩沖模擬輸入

AD4857的每個(gè)通道可以在寬共模輸入范圍內(nèi)同時(shí)采樣其模擬輸入引腳之間的電壓差,高CMRR可衰減兩個(gè)輸入共有的不需要的信號(hào)。寬共模輸入范圍和高CMRR使得INx+和INx - 模擬輸入可以任意擺動(dòng),只要每個(gè)引腳保持在 ((V{EE}+3.2 ~V)) 和 ((V{CC}-3.2 ~V)) 之間。這種特性簡(jiǎn)化了信號(hào)鏈設(shè)計(jì),可接受多種信號(hào)擺動(dòng),包括傳統(tǒng)的模擬輸入信號(hào)類型。

3.2 模擬輸入驅(qū)動(dòng)電路

AD4857的緩沖輸入級(jí)對(duì)采樣過程具有高度的瞬態(tài)隔離能力。大多數(shù)阻抗小于10 kΩ的傳感器、信號(hào)調(diào)理放大器和濾波器網(wǎng)絡(luò)可以直接驅(qū)動(dòng)4 pF的模擬輸入電容。對(duì)于更高阻抗和慢建立電路,可在模擬輸入引腳和GND引腳之間添加一個(gè)680 pF的電容,以保持AD4857的完整直流精度。

3.3 模擬輸入過驅(qū)動(dòng)容限

驅(qū)動(dòng)任何通道的模擬輸入大于 (V{CC}) 電源,最大電流可達(dá)10 mA,不會(huì)影響其他通道的轉(zhuǎn)換結(jié)果。而驅(qū)動(dòng)模擬輸入小于 (V{EE}) 電源可能會(huì)破壞其他通道的轉(zhuǎn)換結(jié)果。在 ((V{C C}-V{E E})>44 ~V) 的應(yīng)用中,建議在每個(gè)INx+和INx - 引腳串聯(lián)一個(gè)外部電阻(例如100 Ω至1000 Ω),以限制故障條件下的閂鎖電流。

3.4 模擬輸入濾波

AD4857的真高阻抗模擬輸入可以適應(yīng)各種無源或有源信號(hào)調(diào)理濾波器。緩沖DAS輸入的模擬帶寬為11 MHz,對(duì)外部濾波器沒有特定的帶寬要求。常見的濾波器配置是簡(jiǎn)單的抗混疊和降噪RC濾波器,其極點(diǎn)位于采樣頻率的一半。

3.5 DAS參考

AD4857支持三種參考配置:內(nèi)部帶隙參考和參考緩沖器、外部參考和內(nèi)部參考緩沖器、外部參考和外部參考緩沖器。大多數(shù)應(yīng)用采用內(nèi)部帶隙參考和參考緩沖器,這是AD4857的默認(rèn)配置。對(duì)于需要更好初始精度和/或更低參考溫度漂移的應(yīng)用,可以禁用內(nèi)部帶隙參考,并用外部參考驅(qū)動(dòng)REFIO引腳。

3.6 電源考慮

AD4857需要五個(gè)電源: (V{CC}) 和 (VEE) (正負(fù)模擬輸入緩沖電源)、 (VDD) (5 V核心電源)、 (V{D D H}) (或 (V_{D D L}) )(1.8 V LDO或1.8 V核心電源)、 (VIO) (數(shù)字輸入和輸出電源)。所有五個(gè)電源都有內(nèi)部旁路電容,不需要額外的外部旁路。

3.7 時(shí)序和控制

AD4857的采樣和轉(zhuǎn)換由CNV引腳控制。CNV引腳的上升沿將所有通道的采樣保持電路從跟蹤模式轉(zhuǎn)換到保持模式,同時(shí)對(duì)所有通道的輸入信號(hào)進(jìn)行采樣并啟動(dòng)轉(zhuǎn)換。轉(zhuǎn)換器狀態(tài)由BUSY輸出指示,BUSY引腳在每次轉(zhuǎn)換開始時(shí)從低電平變?yōu)楦唠娖剑钡睫D(zhuǎn)換完成后再變?yōu)榈碗娖健?/p>

3.8 低功耗模式

AD4857支持多種低功耗模式,包括Nap模式和Power-Down模式。在Nap模式下,部分設(shè)備電路關(guān)閉,可降低轉(zhuǎn)換之間的功耗。在Power-Down模式下,設(shè)備的功耗極低,僅需1.3 mW的典型功耗。

3.9 通道睡眠

每個(gè)通道可以獨(dú)立進(jìn)入睡眠模式,以降低功耗。睡眠模式下,通道的輸入緩沖器和ADC處于低功耗待機(jī)狀態(tài),忽略轉(zhuǎn)換請(qǐng)求。

3.10 復(fù)位時(shí)序

AD4857可以在不循環(huán)電源的情況下執(zhí)行全局復(fù)位,這在從需要將整個(gè)系統(tǒng)重置為已知同步狀態(tài)的系統(tǒng)級(jí)事件中恢復(fù)時(shí)非常有用。

4. 數(shù)字接口

4.1 CMOS轉(zhuǎn)換數(shù)據(jù)輸出模式

AD4857支持CMOS和LVDS串行轉(zhuǎn)換數(shù)據(jù)輸出接口,可通過LVDS/CMOS引腳選擇。在CMOS轉(zhuǎn)換數(shù)據(jù)輸出模式下,應(yīng)用程序可以使用1到8條串行數(shù)據(jù)輸出通道,以優(yōu)化總線寬度和轉(zhuǎn)換數(shù)據(jù)吞吐量。

4.2 LVDS轉(zhuǎn)換數(shù)據(jù)輸出模式

在LVDS轉(zhuǎn)換數(shù)據(jù)輸出模式下,信息通過正負(fù)信號(hào)對(duì)進(jìn)行傳輸,位以差分方式編碼。LVDS總線在 (overline{CS}) 信號(hào)為低電平時(shí)啟用,為高電平時(shí)禁用并處于高阻狀態(tài),允許總線在多個(gè)設(shè)備之間共享。

4.3 數(shù)據(jù)包格式

AD4857提供兩種用戶可選的數(shù)據(jù)包大小:16位和24位。數(shù)據(jù)包數(shù)據(jù)格式取決于數(shù)據(jù)包大小、過采樣模式和測(cè)試模式配置。在非過采樣模式、過采樣模式和測(cè)試模式下,通道和狀態(tài)數(shù)據(jù)包的數(shù)據(jù)格式有所不同。

4.4 SPI寄存器配置總線

SPI寄存器配置總線允許數(shù)字主機(jī)讀取和寫入AD4857的內(nèi)存映射寄存器。該總線獨(dú)立于CMOS或LVDS轉(zhuǎn)換數(shù)據(jù)輸出總線。SPI寄存器配置總線支持3線和4線操作,可通過設(shè)置相應(yīng)的寄存器位進(jìn)行選擇。

5. 寄存器配置

AD4857具有可編程的用戶寄存器,用于配置設(shè)備和監(jiān)控其狀態(tài)。這些寄存器可以通過SPI寄存器配置總線進(jìn)行訪問。寄存器包括SPI配置寄存器、設(shè)備配置寄存器、通道配置寄存器等,每個(gè)寄存器都有特定的功能和位描述。

6. 總結(jié)

AD4857作為一款高性能的數(shù)據(jù)采集系統(tǒng),具有多種強(qiáng)大的特性和功能,適用于各種對(duì)精度和可靠性要求較高的應(yīng)用場(chǎng)景。電子工程師在設(shè)計(jì)過程中,可以根據(jù)具體需求靈活配置AD4857的各個(gè)參數(shù),充分發(fā)揮其優(yōu)勢(shì),提高系統(tǒng)的性能和穩(wěn)定性。在實(shí)際應(yīng)用中,還需要注意電源管理、信號(hào)調(diào)理、PCB布局等方面的問題,以確保AD4857能夠正常工作。你在使用AD4857的過程中,是否遇到過一些特殊的問題呢?歡迎在評(píng)論區(qū)分享你的經(jīng)驗(yàn)和見解。

-

工作原理

+關(guān)注

關(guān)注

4文章

302瀏覽量

38663 -

數(shù)據(jù)采集系統(tǒng)

+關(guān)注

關(guān)注

5文章

323瀏覽量

32141

發(fā)布評(píng)論請(qǐng)先 登錄

AD4856:8通道同步采樣20位250 kSPS數(shù)據(jù)采集系統(tǒng)的卓越之選

AD4855:8通道同步采樣16位250 kSPS數(shù)據(jù)采集系統(tǒng)的技術(shù)剖析

AD4854:高性能4通道同步采樣20位1MSPS數(shù)據(jù)采集系統(tǒng)解析

AD4851:高性能4通道同步采樣16位250kSPS數(shù)據(jù)采集系統(tǒng)

AD4852:4通道同步采樣20位250kSPS數(shù)據(jù)采集系統(tǒng)深度剖析

深入剖析ADuC812:高性能12位數(shù)據(jù)采集系統(tǒng)的卓越之選

MAX180/MAX181:8 通道 12 位數(shù)據(jù)采集系統(tǒng)的深度剖析

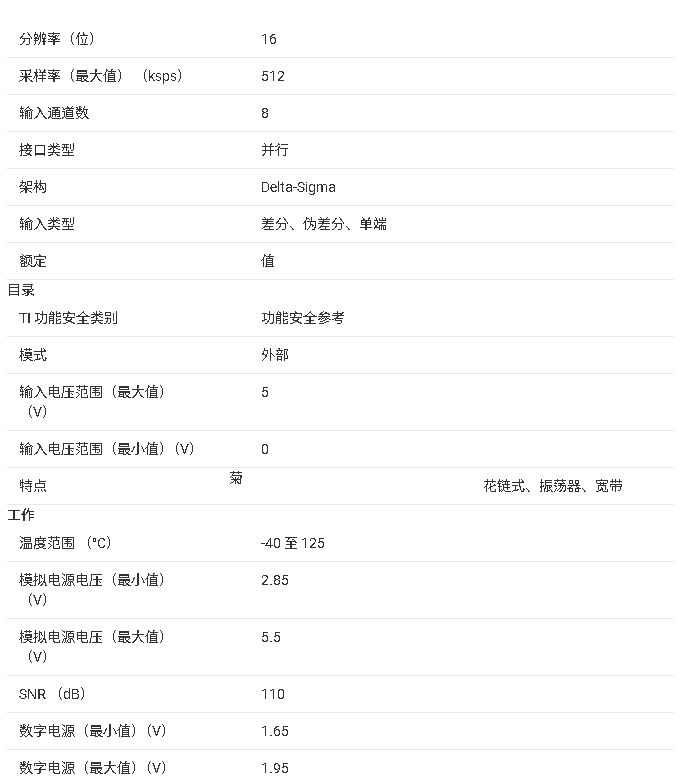

SGM51622S8/SGM51652S8:高性能8通道16位雙極性輸入同步采樣ADC

ADS8345:高性能16位8通道串行輸出采樣ADC的深度解析

ADS117L18 512kSPS、16位、8通道、同步采樣、寬帶寬、Δ-Σ ADC技術(shù)手冊(cè)

Texas Instruments ADS981x系列8通道數(shù)據(jù)采集系統(tǒng)技術(shù)解析

Analog Devices Inc. AD4856 8通道數(shù)據(jù)采集系統(tǒng) (DAS)數(shù)據(jù)手冊(cè)

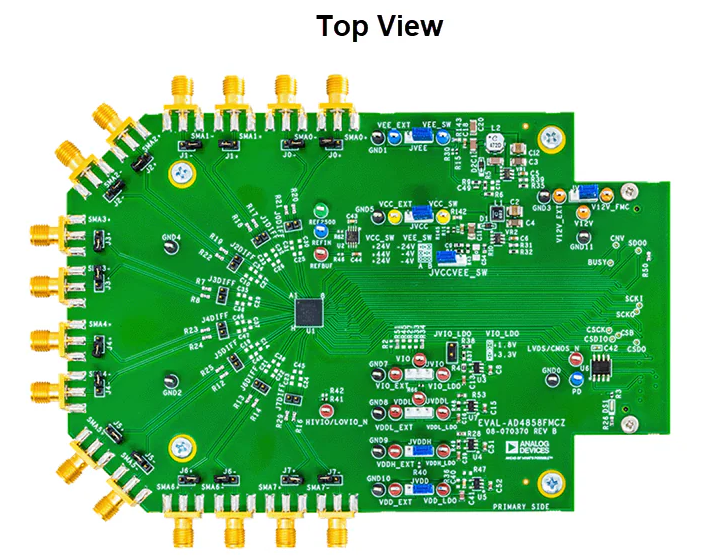

Analog Devices Inc. EVAL-AD4857FMCZ AD4857評(píng)估板數(shù)據(jù)手冊(cè)

Analog Devices Inc. AD4857 8通道數(shù)據(jù)采集系統(tǒng) (DAS)數(shù)據(jù)手冊(cè)

AD4857:8通道同步采樣16位數(shù)據(jù)采集系統(tǒng)的剖析

AD4857:8通道同步采樣16位數(shù)據(jù)采集系統(tǒng)的剖析

評(píng)論