AD4852:4通道同步采樣20位250kSPS數據采集系統深度剖析

在電子設計領域,數據采集系統(DAS)扮演著至關重要的角色,尤其是在需要高精度、高吞吐量和高動態范圍的應用中。今天,我們就來深入探討一款功能強大的DAS——AD4852。

文件下載:AD4852.pdf

一、AD4852簡介

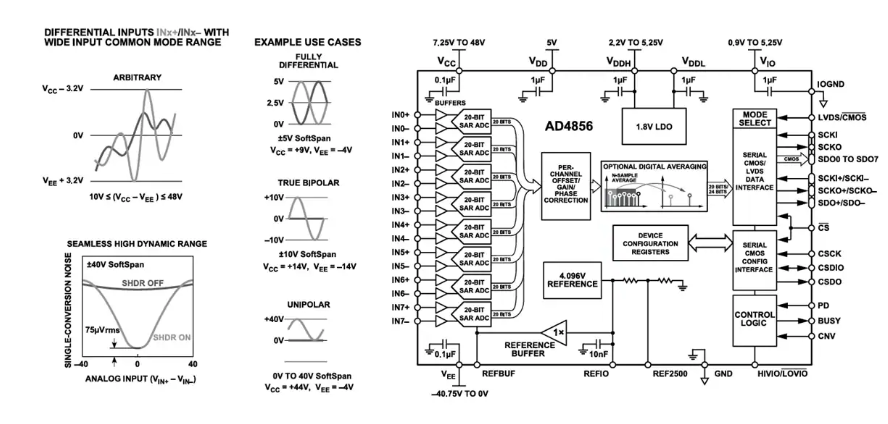

AD4852是一款全緩沖、4通道同步采樣、20位、250kSPS的數據采集系統,具備差分、寬共模范圍輸入的特性。它采用5V低壓電源和靈活的輸入緩沖電源,搭配精密低漂移的內部基準和基準緩沖器,使得每個通道的SoftSpan范圍能夠獨立配置,以匹配應用信號的擺動,從而最大程度減少額外的外部信號調理。

二、關鍵特性

2.1 高精度與高動態范圍

- 20位分辨率:能夠實現高精度的數據采集,滿足對數據精度要求較高的應用場景。

- 無縫高動態范圍(SHDR)技術:這是AD4852的一大亮點。啟用SHDR后,通道的輸入信號路徑增益會在每個采樣上自動優化,在不影響線性度的情況下,將每個采樣的轉換器噪聲降至最低。例如,在±40V范圍內,啟用SHDR可使單轉換動態范圍提高達15.6dB。

- 出色的AC性能:典型的SNR為97.2dB(±40V范圍),DR為111.4dB(±40V范圍),THD為 - 117dB(±40V范圍),CMRR為120dB,這些參數保證了在復雜信號環境下的高質量數據采集。

2.2 靈活的輸入配置

- 16種SoftSpan范圍:每個通道可獨立配置為16種SoftSpan范圍之一,涵蓋了從±0.625V到±40V的多種輸入范圍,能適應不同的應用需求。

- 寬共模輸入范圍:輸入共模范圍為 (V{EE}+3.2V) 到 (V{CC}-3.2V),且具有120dB的共模抑制比(CMRR),允許輸入信號在INx+和INx - 上任意擺動,增強了系統對不同信號的適應性。

2.3 低功耗設計

- 每通道36mW:在250kSPS的采樣頻率下,每通道功耗僅為36mW,且功耗會隨吞吐量縮放。此外,還提供了可選的休眠和掉電模式,可在非活動期間進一步降低功耗。

2.4 數字處理功能豐富

- 24位過采樣:可選的24位過采樣功能可進一步提高SNR和動態范圍,適用于對噪聲和動態范圍要求較高的應用。

- 通道偏移、增益和相位調整:允許對每個通道進行獨立的偏移、增益和相位調整,以校正系統級誤差。

2.5 靈活的數字接口

- SPI寄存器配置總線:支持0.9V到5.25V的SPI寄存器配置總線,方便進行設備配置和狀態監測。

- LVDS和CMOS轉換數據輸出:通過LVDS/CMOS引腳可選擇LVDS或CMOS轉換數據輸出模式,在CMOS模式下可使用1到4條數據線輸出,優化總線寬度和吞吐量。

三、工作原理

3.1 轉換操作

AD4852的工作分為采集和轉換兩個階段。在采集階段,每個通道的采樣保持電路中的采樣電容連接到各自的模擬輸入緩沖器,跟蹤差分輸入電壓 ((V{INx+}-V{INx-}))。當CNV引腳出現上升沿時,所有采樣保持電路從跟蹤模式轉換到保持模式,同時對所有通道的輸入信號進行采樣并啟動轉換。在轉換階段,每個通道的采樣電容連接到一個20位的電荷再分配電容數模轉換器(CDAC),通過逐次逼近算法將采樣的輸入電壓與通道SoftSpan滿量程范圍的二進制加權分數進行比較,最終輸出近似的數字代碼。

3.2 傳輸函數

AD4852將每個通道的滿量程電壓范圍數字化為 (2^{20}) 個離散電平。每個通道的SoftSpan配置決定了其差分輸入電壓范圍、LSB大小和轉換結果的二進制格式。對于雙極性SoftSpan范圍,轉換結果以二進制補碼格式輸出;對于單極性SoftSpan范圍,則以直二進制格式輸出。

3.3 SoftSpan配置

每個通道可以獨立配置為16種SoftSpan范圍之一,默認范圍為SoftSpan 15(±40V雙極性輸入跨度)。通過向相應的寄存器寫入4位SoftSpan代碼,即可配置通道的不同范圍。

3.4 無縫高動態范圍(SHDR)

SHDR是一種專有技術,它能在每個采樣上提供盡可能低的輸入參考轉換噪聲。禁用SHDR時,每個通道的SoftSpan范圍會自動定義一個固定的轉換器模擬信號增益,應用于該通道的每個采樣。啟用SHDR后,轉換器會根據每個采樣的差分電壓動態調整模擬信號增益,對于接近所選SoftSpan范圍最大值的差分電壓,增益與禁用SHDR時相同;對于幅值較低的采樣,轉換器會自動增加增益,從而降低這些采樣的輸入參考轉換噪聲,提高動態范圍。

3.5 數字處理特性

- 過采樣模式:默認情況下,AD4852工作在非過采樣模式。啟用過采樣模式后,AD4852會計算每個通道多個轉換結果的數字平均值,所有通道共享一個共同的過采樣比,只有每個通道的平均結果可供讀取。過采樣模式有助于降低噪聲和提高每個輸出數據字的動態范圍。

- 數字偏移校正:每個通道可以獨立編程,為每個轉換結果添加一個20位的有符號數字偏移校正值,用于校正DAS模擬輸入上游的固定偏移誤差。

- 數字增益校正:每個通道可以獨立編程,對每個轉換結果應用一個數字增益校正因子,以校正DAS模擬輸入上游的固定增益誤差。

- 數字相位校正:在過采樣模式下,每個通道可以獨立編程,對過采樣的數字平均值應用一個數字相位校正項,以補償DAS模擬輸入上游的相位誤差。

- 通道過范圍和欠范圍限制:每個通道的每個轉換結果都會與20位有符號的過范圍和欠范圍限制進行比較。如果檢測到任何超出范圍的轉換結果,相應的標志位會在CH_OR_STATUS寄存器或CH_UR_STATUS寄存器中設置。

四、應用信息

4.1 緩沖模擬輸入

AD4852的每個通道能夠在寬共模輸入范圍內同時采樣其模擬輸入引腳之間的電壓差,高CMRR可衰減兩個輸入共有的不需要的信號。寬共模輸入范圍和高CMRR使得INx+和INx - 模擬輸入能夠以任意關系擺動,只要每個引腳保持在 ((V{EE}+3.2V)) 和 ((V{CC}-3.2V)) 之間。此外,緩沖器 (V{CC}) 和 (V{EE}) 電源的寬工作范圍提供了進一步的輸入共模靈活性,可根據具體應用需求調整絕對輸入范圍。

4.2 模擬輸入驅動電路

AD4852的緩沖輸入級對采樣過程具有高度的瞬態隔離能力。大多數阻抗小于10kΩ的傳感器、信號調理放大器和濾波器網絡可以直接驅動4pF的模擬輸入電容。對于更高阻抗和慢穩定電路,可在模擬輸入引腳和GND引腳之間添加一個680pF的電容,以保持AD4852的全直流精度。

4.3 模擬輸入過驅動容限

在任何通道上,將模擬輸入驅動到大于 (V{CC}) 電源的電流高達10mA時,不會影響其他通道的轉換結果。但將模擬輸入驅動到小于 (V{EE}) 電源可能會破壞其他通道的轉換結果。在 ((V{CC}-V{EE})>44V) 的應用中,建議在每個INx+和INx - 引腳串聯一個外部電阻(如100Ω到1000Ω),以限制故障條件下的閂鎖電流。

4.4 模擬輸入濾波

AD4852的真正高阻抗模擬輸入可以適應各種無源或有源信號調理濾波器。緩沖的DAS輸入具有11MHz的模擬帶寬,對外部濾波器沒有特定的帶寬要求,因此外部輸入濾波器可以獨立于DAS進行優化,以減少信號鏈噪聲和干擾。常見的濾波器配置是簡單的抗混疊和降噪RC濾波器,其極點位于采樣頻率的一半。

4.5 DAS參考

AD4852支持三種參考配置:內部帶隙基準和基準緩沖器、外部基準和內部基準緩沖器、外部基準和外部基準緩沖器。大多數應用采用內部帶隙基準和基準緩沖器,這是AD4852的默認配置。對于需要更好初始精度和/或更低基準溫度漂移的應用,可以禁用內部帶隙基準,用外部基準驅動REFIO引腳。在極少數情況下,也可以禁用內部帶隙基準和內部基準緩沖器,用外部基準驅動REFBUF引腳。

4.6 電源考慮

AD4852需要五個電源:(V{CC}) 和 (V{EE})(正負模擬輸入緩沖電源)、(V{DD})(5V核心電源)、(V{DDH})(或 (V{DDL}))(1.8V LDO或1.8V核心電源)、(V{IO})(數字輸入和輸出電源)。所有五個電源都有內部旁路電容,不需要額外的外部旁路。電源沒有特定的排序要求,但需要注意遵守絕對最大額定值中描述的最大電壓關系。

4.7 定時和控制

AD4852的采樣和轉換由CNV引腳控制。CNV引腳的上升沿將所有通道的采樣保持電路從跟蹤模式轉換到保持模式,同時對所有通道的輸入信號進行采樣并啟動轉換。轉換開始后,除非重置DAS,否則無法提前終止。為了獲得最佳性能,應使用干凈、低抖動的信號驅動CNV引腳,并避免在CNV引腳上升沿之前的數據輸入和輸出線上發生轉換。轉換器狀態由BUSY輸出指示,BUSY在每次轉換開始時從低電平變為高電平,直到轉換完成后再變為低電平。

4.8 休眠模式和掉電模式

- 休眠模式:在轉換完成后,AD4852可以進入休眠模式,以降低轉換之間的功耗。在這種模式下,部分設備電路會關閉,包括與采樣模擬輸入信號相關的電路。通過在轉換之間保持CNV引腳高電平來啟用休眠模式。

- 掉電模式:當PD引腳置高,或設備配置寄存器中的PWRMODE位(Bits[1:0])設置為0x3時,AD4852進入掉電模式,后續的轉換請求將被忽略。在掉電模式下,AD4852僅消耗少量的待機電流,典型功耗為1.3mW。要退出掉電模式,需將PD引腳置低,并在啟動轉換前等待至少 (t{WAKE,MAX}=1ms)。

4.9 通道睡眠

AD4852的每個通道可以獨立進入睡眠模式,以降低功耗。啟用睡眠模式后,通道的輸入緩沖器和ADC將進入低功耗待機狀態,轉換請求將被忽略。默認情況下,所有通道的睡眠模式均禁用。

4.10 復位定時

AD4852可以在不循環電源的情況下執行全局復位,這在從需要將整個系統重置到已知同步狀態的系統級事件中恢復時非常有用。可以通過在沒有中間轉換的情況下將PD引腳置高兩次,或者使用設備配置寄存器中的PWR_MODE位(Bits[1:0])進入、退出并重新進入掉電模式來觸發全局復位。

五、數字接口

5.1 CMOS轉換數據輸出模式

在CMOS轉換數據輸出模式下,串行CMOS轉換數據輸出總線由一個串行時鐘輸入(SCKI)、一個串行時鐘輸出(SCKO)和四個串行數據輸出通道(SDO0到SDO3)組成。通信在預定義的數據事務窗口內進行,設備在窗口內輸出用戶可配置的數據包,包含轉換或過采樣結果、可選的通道配置和設備狀態信息。數據包大小可在20位、24位和32位之間選擇。

5.2 LVDS轉換數據輸出模式

在LVDS轉換數據輸出模式下,信息通過正負極性信號對以差分編碼的方式傳輸,這些信號通常使用具有100Ω特性阻抗的差分傳輸線進行路由。串行LVDS轉換數據輸出總線由差分串行時鐘輸入對(SCKI+和SCKI - )、差分串行時鐘輸出對(SCKO+和SCKO - )和差分串行數據輸出對(SDO+和SDO - )組成。通信同樣在預定義的數據事務窗口內進行,數據包格式和大小與CMOS模式類似。

5.3 數據包格式

AD4852提供三種用戶可選擇的數據包大小:20位、24位和32位。數據包數據格式取決于數據包大小、過采樣模式和測試模式配置。在非過采樣模式下,通道數據包包含20位轉換結果,狀態數據包包含設備狀態信息和16位CRC校驗碼。在過采樣模式下,通道數據包包含20位或24位平均轉換結果。在測試模式下,通道數據包由CHx_TESTPAT寄存器中的數據定義。

5.4 SPI寄存器配置總線

SPI寄存器配置總線允許數字主機對AD4852的內存映射寄存器進行讀寫操作。該總線獨立于CMOS或LVDS轉換數據輸出總線。上電或全局復位后,SPI寄存器配置總線默認工作在3線模式,可通過設置SPI配置A寄存器中的CSDO_EN位為1來啟用4線模式。SPI幀由CS下降沿開始,接著是16位的指令階段和可變長度的數據階段,最后以CS上升沿結束。

六、寄存器總結

AD4852具有可編程的用戶寄存器,用于配置設備和監測其狀態。這些寄存器可以通過SPI寄存器配置總線進行訪問。寄存器包括SPI配置寄存器、設備配置寄存器、通道配置寄存器等,每個寄存器都有特定的功能和位定義。

七、應用領域

AD4852的高性能和靈活性使其適用于多種應用領域,包括自動測試設備、航空航天、儀器儀表和控制系統、半導體制造、測試和測量等。在這些應用中,AD4852能夠提供高精度、高吞吐量的數據采集,滿足復雜信號處理的需求。

八、總結

AD4852作為一款功能強大的數據采集系統,具有高精度、高動態范圍、靈活的輸入配置、低功耗和豐富的數字處理功能等優點。其獨特的SHDR技術和多種工作模式使其能夠適應不同的應用場景,為電子工程師在設計高性能數據采集系統時提供了一個優秀的選擇。在使用AD4852時,需要根據具體應用需求合理配置其參數和工作模式,以充分發揮其性能優勢。同時,在PCB設計和電源管理等方面也需要注意相關的要求和建議,以確保系統的穩定性和可靠性。

你是否在實際項目中使用過類似的數據采集系統?在使用過程中遇到過哪些問題?歡迎在評論區分享你的經驗和見解。

-

高精度

+關注

關注

1文章

827瀏覽量

27099 -

數據采集系統

+關注

關注

5文章

323瀏覽量

32141

發布評論請先 登錄

ADAQ4381 - 4:四通道高精度數據采集模塊的深度剖析

AD4853:高性能4通道數據采集系統的深度解析

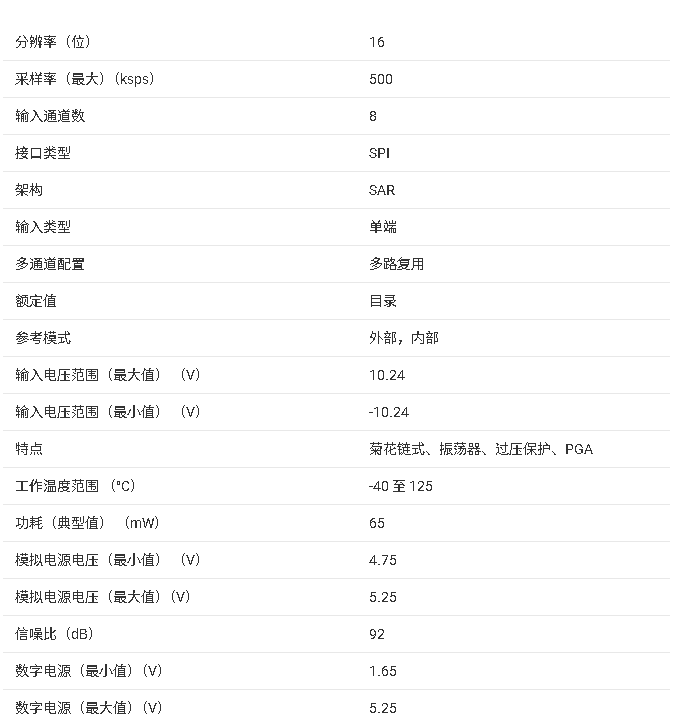

ADS8345:高性能16位8通道串行輸出采樣ADC的深度解析

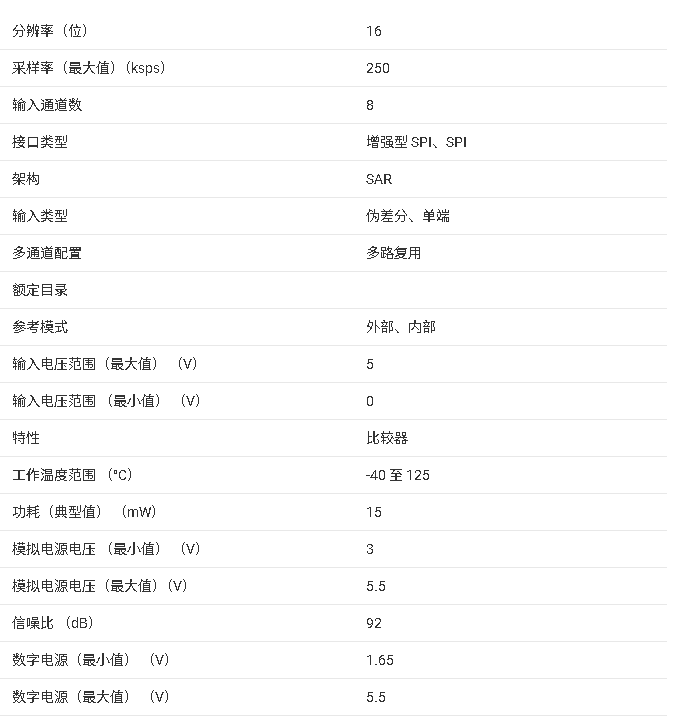

ADS8166 16位、250kSPS、8通道SAR ADC技術手冊

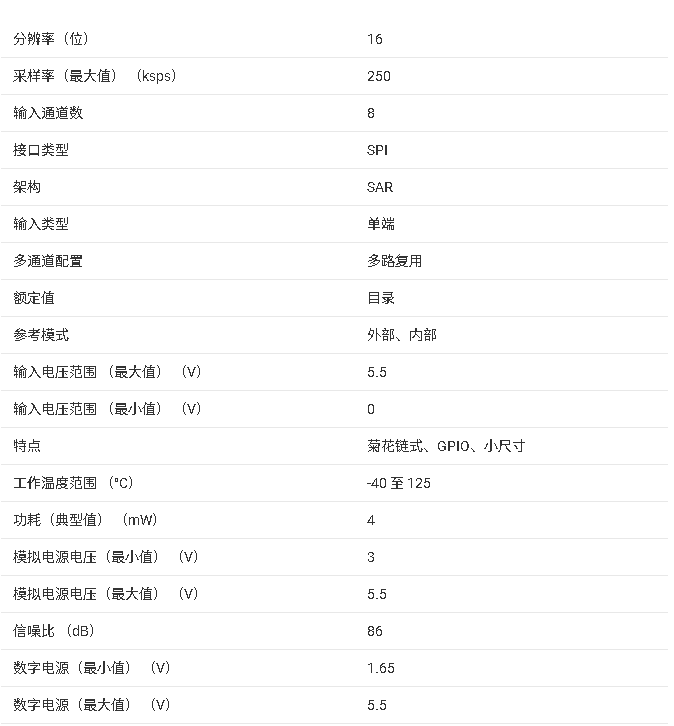

ADS7066 8通道、250kSPS、16位模數轉換器技術手冊

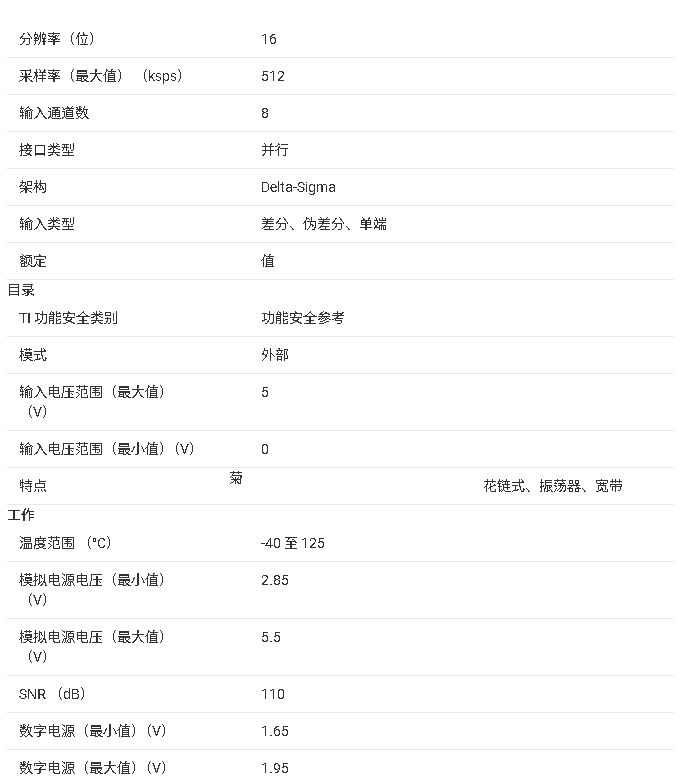

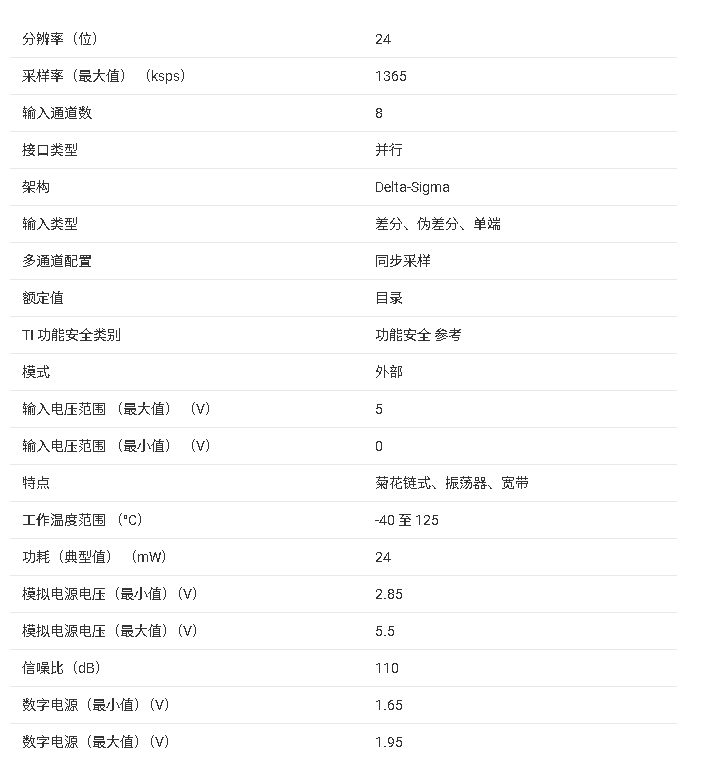

ADS117L18 512kSPS、16位、8通道、同步采樣、寬帶寬、Δ-Σ ADC技術手冊

Analog Devices Inc. AD4856 8通道數據采集系統 (DAS)數據手冊

AD4852:4通道同步采樣20位250kSPS數據采集系統深度剖析

AD4852:4通道同步采樣20位250kSPS數據采集系統深度剖析

評論