由于 RISC-V 是一個開放性的 ISA,它允許任何開發者自由設計和擴展定制處理器。基于 RISC-V 的處理器必須保持與不斷增長的支持工具和軟件生態系統的兼容性。

RISC-V 處理器驗證需求

RISC-V 處理器驗證需要一種能夠匹配 ISA 可配置和可擴展特性的解決方案,滿足以下特定需求:

能夠與用戶現有的環境協同工作,并且應利用諸如 RISC-V 驗證接口 (RVVI) 等開放標準接口,以實現高效和復用。

應支持行業最佳實踐,例如約束隨機激勵和功能覆蓋率。

解決方案必須應對處理器特定的挑戰,例如驗證 DUT(待測單元)在響應異步事件時的行為。

新思科技 ImperasDV 解決方案

新思科技推出的 ImperasDV 是滿足所有這些要求的解決方案。

ImperasDV 是一種針對基于 RISC-V 指令集架構(ISA)的定制處理器的前端設計驗證解決方案。它包括參考模型、驗證組件、功能覆蓋率、測試套件以及調試器等核心組件。

ImperasDV 使用 ImperasFPM(快速處理器模型)作為設計驗證的參考模型。該模型可以配置基本 ISA 和擴展指令,包括設計者定制的功能,以匹配待測處理器。

ImperasDV 可以用于 SystemVerilog/UVM 測試平臺,或任何具有 C 語言接口的平臺。它使用 RVVI-TRACE 接口連接到待測處理器,并提供架構狀態的持續比較和檢查。

ImperasFC 則是一個 RISC-V 指令集的 SystemVerilog 功能覆蓋模型,可以為 RISC-V ISA 中的每個擴展提供自動生成的功能覆蓋率模型。

ImperasTS 提供針對 RISC-V ISA 的復雜和可配置擴展集的測試套件,用來確保設計和 ISA 之間的兼容性和一致性。

ImperasDV 使用鎖步連續比較的設計驗證方法,這是一種協同仿真方法,其中 RTL 和參考模型以鎖步方式運行。同一個程序在 RTL 和 ImperasFPM 上并行執行,每條指令完成時,比較兩者的架構狀態,狀態不匹配會立即報告為錯誤。

通過這種全面的設計驗證方法,實現高效驗證,更快發現錯誤,立即報告,方便開發者在故障點進行調試。

ImperasDV 技術優勢

ImperasDV 擁有顯著的技術優勢,主要表現在以下幾個方面:

顯著縮短處理器設計驗證進度,高效的驗證方法能顯著減少整體驗證周期。

支持驗證最佳實踐,包括功能覆蓋率和約束隨機測試生成。

實現復雜功能的設計驗證,例如中斷、調試模式、特權模式、虛擬內存、多核、多發射以及亂序流水線等。

支持定制功能的設計驗證,可擴展以驗證用戶自定義的處理器特性。

采用鎖步連續比較方法,RTL 與參考模型協同仿真,指令完成后立即比較架構狀態。

驗證異步事件的專有同步技術可有效處理異步事件,減少錯誤來源。

硬件與軟件開發共享同一參考模型,提高一致性,支持跨領域驗證和開發。

端到端的驗證和仿真工具集

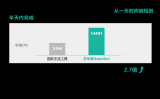

新思科技在驗證領域一直處于領先地位,為客戶提供一系列端到端的驗證和仿真工具集。ImperasDV 與新思科技其他驗證工具都可以完美結合。與 VCS 一起進行 RISC-V RTL 仿真,功能覆蓋率輸出會發送到調試和驗證管理平臺 Verdi。新思科技 VCS 與 ImperasDV 的結合降低了 RTL 風險并加速驗證進度。

結語

新思科技匯聚行業頂尖專家,不斷革新工具,始終走在最新技術應用的前沿,在 RISC-V 驗證領域也持續與合作伙伴保持深厚且值得信賴的關系,為合作伙伴提供卓越的產品和服務。

-

處理器

+關注

關注

68文章

20309瀏覽量

254106 -

新思科技

+關注

關注

5文章

972瀏覽量

52977 -

RISC-V

+關注

關注

49文章

2927瀏覽量

53414

原文標題:精準排錯!ImperasDV讓RISC-V處理器驗證更高效、更精準

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技邀您共赴2026玄鐵RISC-V生態大會

新思科技VC Formal解決方案在RISC-V驗證中的應用

新思科技ARC-V處理器驅動RISC-V市場無限機遇

重磅合作!Quintauris 聯手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

新思科技全棧工具鏈助力RISC-V設計高效進階

開芯院采用芯華章高性能數字仿真器GalaxSim,RISC-V 驗證獲近3倍效率提升

為什么RISC-V是嵌入式應用的最佳選擇

基于E203 RISC-V的音頻信號處理系統 -協處理器的乘累加過程

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

2025新思科技RISC-V科技日活動圓滿結束

芯華章RISC-V敏捷驗證方案再升級

開芯院采用芯華章P2E硬件驗證平臺加速RISC-V驗證

直播預約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

新思科技ImperasDV解決方案讓RISC-V處理器驗證效率翻倍

新思科技ImperasDV解決方案讓RISC-V處理器驗證效率翻倍

評論