DS1094L:多相擴頻經濟振蕩器的技術解析與應用指南

在電子設計領域,時鐘發生器的性能對于系統的穩定性和電磁兼容性至關重要。DS1094L作為一款多相擴頻經濟振蕩器,為開關模式電源等應用提供了出色的解決方案。本文將深入剖析DS1094L的特性、工作原理、電氣參數以及應用要點,幫助電子工程師更好地理解和應用這款產品。

文件下載:DS1094L.pdf

一、DS1094L概述

DS1094L是一款硅振蕩器,可產生四個多相、擴頻方波輸出。其輸出頻率范圍為2MHz至31.25kHz,支持兩相、三相或四相模式。通過對內部主振蕩器進行0%、2%、4%或8%的抖動處理,能夠顯著降低系統級的電磁干擾(EMI)輻射。該產品非常適合作為開關模式電源的時鐘發生器,其輸出可用于DC - DC電路,實現電壓的高效升降轉換。

二、主要特性

2.1 多相輸出

支持兩相、三相或四相輸出,滿足不同應用場景的需求。

2.2 頻率可編程

輸出頻率可在2MHz至31.25kHz之間進行編程,靈活性高。

2.3 擴頻抖動

抖動輸出可有效降低EMI輻射,提高系統的電磁兼容性。

2.4 無需外部定時組件

內部集成了必要的定時功能,簡化了設計。

2.5 非易失性配置

配置設置具有非易失性,斷電后數據不丟失。

2.6 可編程選項

支持用戶編程和工廠預編程兩種方式。

2.7 寬工作溫度范圍

工作溫度范圍為 - 40°C至 + 85°C,適用于各種惡劣環境。

三、電氣參數

3.1 直流電氣特性

- 電源電壓(VCC):3.0V至3.6V。

- 輸入邏輯電平:輸入邏輯1(SDA、SCL)為0.7 x VCC至VCC + 0.3V;輸入邏輯0(SDA、SCL)為 - 0.3V至0.3 x VCC。

- 輸出電壓:高電平輸出電壓(OUT1 - 4)在IOH = - 4mA、VCC = min時為2.4V;低電平輸出電壓(OUT1 - 4)在IOL = 3.5mA時為0.4V。

3.2 交流電氣特性

- 主振蕩器頻率(fMOSC):1MHz至2MHz。

- 輸出頻率容差(?fOUT):在VCC = 3.3V、TA = + 25°C時為 - 2.5%至 + 2.5%。

- 電壓頻率變化(?fOUT):在TA = + 25°C時為 - 0.5%至 + 0.5%。

- 溫度頻率變化(?fOUT):在VCC = 3.3V時,0°C至 + 70°C為 - 1.1%至 + 1.1%, - 40°C至 + 85°C為 - 2.5%至 + 1.1%。

四、工作原理

4.1 主振蕩器

主振蕩器負責產生輸出的時序和頻率,其頻率fMOSC可在1MHz至2MHz之間以100kHz的步長進行編程。通過DAC寄存器進行編程,公式為fMOSC = 1MHz + (DAC值 x 100kHz),DAC值范圍為0至10(十進制)。

4.2 預分頻器

預分頻器將主振蕩器頻率fMOSC除以1、2、4或8,得到輸出頻率fOSC,計算公式為fOSC = fMOSC / 2^PRESCALER,其中PRESCALER取值為0至3。

4.3 相位發生器

四個振蕩器輸出(OUT1至OUT4)可配置為兩相、三相或四相模式,通過PRESCALER寄存器中的Ph1和Ph0位進行選擇。

4.4 三角波發生器

用于對主振蕩器頻率進行抖動處理,增加擴頻功能。抖動量和抖動頻率均可編程,分別由PRESCALER寄存器中的J1、J0和D1、D0位控制。

五、2 - 線串行接口

DS1094L通過2 - 線串行接口進行編程,包括SDA(數據輸入/輸出)和SCL(時鐘輸入)。該接口支持讀寫控制寄存器,默認從地址為B0h,可通過ADDR寄存器中的3個地址位(A2、A1、A0)進行更改,最多允許8個DS1094L共享同一2 - 線總線。

5.1 數據傳輸定義

- 主設備:控制總線上的從設備,產生SCL時鐘脈沖、起始和停止條件。

- 從設備:根據主設備的請求發送和接收數據。

- 總線空閑:SDA和SCL均處于高電平的狀態。

- 起始條件:SDA從高電平變為低電平,同時SCL保持高電平。

- 停止條件:SDA從低電平變為高電平,同時SCL保持高電平。

- 重復起始條件:用于連續數據傳輸。

- 位寫入:SDA在SCL低電平時進行數據轉換,數據在SCL高電平期間保持有效。

- 位讀取:主設備在讀取位之前需釋放SDA總線。

- 確認(ACK和NACK):第9位用于確認數據傳輸。

5.2 通信流程

- 單字節寫入:主設備生成起始條件,寫入從地址字節(R/W = 0)、內存地址、數據字節,最后生成停止條件,并讀取從設備的確認信息。

- 單字節讀取:使用虛擬寫入周期,主設備生成起始條件,寫入從地址字節(R/W = 0)、要讀取的寄存器內存地址,生成重復起始條件,寫入從地址字節(R/W = 1),讀取寄存器并發送NACK,最后生成停止條件。

六、應用要點

6.1 SDA和SCL上拉電阻

SDA為開漏輸出,需要上拉電阻來實現高邏輯電平。SCL可使用開漏輸出加電阻或CMOS輸出驅動器。上拉電阻值應確保上升和下降時間符合交流電氣特性要求。

6.2 獨立運行

如果DS1094L獨立運行(無2 - 線主設備),SDA和SCL不應懸空,建議使用上拉電阻,以防止引腳浮動到未知電壓。

6.3 電源去耦

為了獲得最佳性能,建議在IC電源引腳使用去耦電容,典型值為0.01μF和0.1μF,應選擇高質量的陶瓷表面貼裝電容,并盡量靠近IC的VCC和GND引腳安裝,以減小引線電感。

七、總結

DS1094L作為一款高性能的多相擴頻經濟振蕩器,具有豐富的功能和良好的電氣性能。其可編程的輸出頻率、多相輸出模式以及擴頻抖動功能,使其在開關模式電源等應用中具有顯著優勢。電子工程師在設計過程中,應充分了解其工作原理和電氣參數,合理選擇上拉電阻和去耦電容,以確保系統的穩定性和可靠性。在實際應用中,你是否遇到過類似振蕩器的使用問題?又是如何解決的呢?歡迎在評論區分享你的經驗。

-

開關模式電源

+關注

關注

1文章

76瀏覽量

10138

發布評論請先 登錄

DS1099低頻率雙輸出經濟型振蕩器:設計與應用全解析

低功耗DS1090:低頻率擴頻經濟振蕩器的詳細解析

探索DS1080L:低抖動擴頻晶體倍增器的卓越性能

深入解析DS32kHz:高精度溫度補償晶體振蕩器

高性能超低抖動振蕩器LMK61XX:技術解析與設計指南

高性能超低抖動振蕩器LMK61XX:技術解析與應用指南

高性能超低抖動振蕩器LMK61XX:技術解析與設計指南

LMK62XX高性能低抖動振蕩器:技術解析與應用指南

CDC6Cx-Q1低功耗LVCMOS輸出BAW振蕩器:技術解析與應用指南

汽車時鐘MC - K系列時鐘振蕩器:設計與應用指南

CD4098B:高性能CMOS雙單穩態多諧振蕩器的技術解析與應用指南

CD4098B:CMOS 雙單穩態多諧振蕩器的技術解析與應用指南

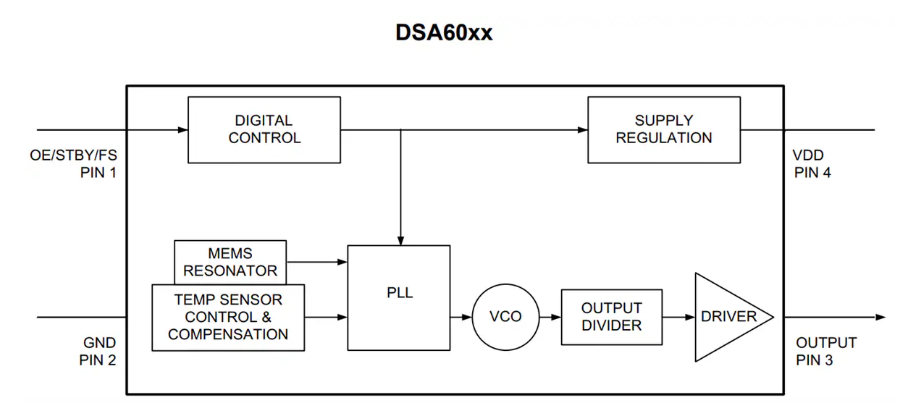

?Microchip DSA60XX MEMS振蕩器技術解析與應用指南

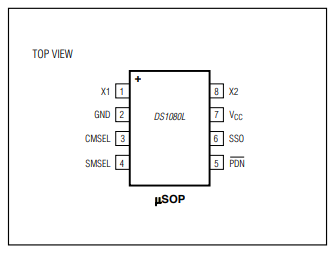

DS1080L擴頻晶振倍頻器技術手冊

32.768KHz 振蕩器:應用、技術解析及未來發展趨勢

DS1094L:多相擴頻經濟振蕩器的技術解析與應用指南

DS1094L:多相擴頻經濟振蕩器的技術解析與應用指南

評論