高密度疊層母排 (Laminated Busbar) 雜散電感優化指南:中壓系統設計的結構工程精髓及其在SiC模塊應用中的核心作用

功率電子系統的范式轉移與寄生參數的系統性瓶頸

在當前高功率、中壓能量轉換領域,從傳統的硅 (Si) 絕緣柵雙極型晶體管 (IGBT) 向碳化硅 (SiC) 金屬氧化物半導體場效應晶體管 (MOSFET) 的過渡,代表了一場深刻的底層技術范式轉移 。SiC半導體材料具備卓越的物理與電氣特性,包括更寬的禁帶寬度、極高的擊穿電場強度以及卓越的熱耐受能力 。這些材料層面的優勢使得SiC MOSFET能夠實現極低的導通電阻 (RDS(on)?) 和微乎其微的寄生結電容,從而使其開關速度能夠達到同等電壓等級硅器件的十倍以上 。因此,基于SiC的逆變器系統可以在顯著提高的開關頻率下運行,這不僅極大地提升了系統的功率密度和能量轉換效率,還使得被動磁性元件的體積和重量得以大幅度縮減 。

然而,SiC器件所具備的這種非凡的開關速度,也為系統級動態設計引入了極其嚴峻的挑戰。極高的開關速度直接轉化為瞬態過程中極高的電壓變化率 (dv/dt) 和電流變化率 (di/dt) 。在傳統的硬開關轉換器拓撲結構中,這種極高的 di/dt 與功率分配架構中固有的寄生雜散電感之間會發生劇烈的相互作用,從而引發嚴重的系統性能退化 。這種相互作用最致命的表現形式是跨越半導體器件兩端產生巨大的瞬態電壓過沖,其數學物理關系由基礎電感方程 Vovershoot?=Lstray??dtdi? 所嚴格支配 。

這種由寄生電感引發的電壓尖峰會直接疊加在穩態直流 (DC) 母線電壓之上,危險地逼近甚至突破功率器件的最大擊穿電壓額定值。為了防止災難性的雪崩擊穿失效,結構與電氣設計工程師往往被迫做出妥協:要么選擇具有更高電壓額定值的功率模塊(這不可避免地會導致更高的導通損耗和制造成本),要么通過增加外部柵極電阻 (RG?) 來人為地減緩器件的開關速度,而這種做法直接犧牲了引入SiC技術本應帶來的高頻高效優勢 。此外,雜散電感與SiC MOSFET固有的輸出電容 (Coss?) 之間的諧振相互作用,會引發持續時間長、頻率極高的振蕩(Ringing)現象 。這種高頻振蕩不僅會產生強烈的電磁干擾 (EMI),使得系統難以通過嚴格的電磁兼容性合規審查,還會進一步加劇動態開關損耗,導致器件發熱嚴重 。 傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

基本半導體代理商傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

由此可見,對功率電路中雜散電感的深度優化,已不再是系統設計中一個處于邊緣地位的機械附屬考量,而是全面釋放SiC技術潛力的最核心、最緊迫的結構工程先決條件 。在這一背景下,高密度疊層母排 (Laminated Busbar) 作為一種代表當前最高技術水平的功率傳輸接口,被廣泛應用于高功率、中壓逆變器系統中,以徹底打破寄生電感的瓶頸 。通過在幾何結構上強制使相反方向的電流路徑無限靠近,疊層母排能夠實現互感磁場的最大化抵消,從而提供系統所能達到的最低互連電感,最終確保SiC器件實現最佳的電氣性能與轉換效率 。疊層母排的結構工程設計,在根本上決定了整個逆變器系統的電氣穩定性、熱管理效率以及電磁兼容性邊界 。

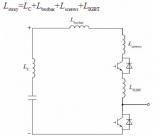

雜散電感的電磁學發生機理與疊層結構的數學建模

為了對高功率分配系統進行精準的結構優化,必須首先建立對雜散電感電磁學生成機制的嚴謹理論認知。在任何高頻電氣回路中,雜散電感 (Lstray?) 都是一種非故意的但又物理上無法避免的特性,它源自于導體、印刷電路板 (PCB) 走線、元器件引腳以及內部鍵合線的物理幾何形態 。逆變器電流換流回路 (Current Commutation Loop, CCL) 的總雜散電感,是功率模塊內部封裝寄生電感 (Lp?)、分立元件等效電感以及母排外部互連電感的總和 。

疊層母排之所以能夠將外部互連電感降至最低,依賴于其特有的高密度復合拓撲結構。與傳統的線束、圓形導體或單層厚重銅排截然不同,疊層母排由多層高導電率金屬(通常為紫銅或鋁)通過超薄、高介電強度的絕緣材料壓合而成,形成一個高度緊湊的“三明治”式層疊結構 。

互感抵消原理與電磁場解析

疊層母排抑制雜散電感的最核心機制在于互感 (Mutual Inductance) 抵消效應的最大化。對于一個典型的雙平面疊層母排電路,其總等效雜散電感 (Leq?) 可以通過以下解析方程嚴謹表達:

Leq?=Lp?+Ln??2M

在該方程中,Lp? 代表正極導電銅排的自感,Ln? 代表負極導電銅排的自感,而 M 則是這兩層相互重疊的平行銅排之間的互感 。

自感的大小主要取決于單一導體自身的幾何尺寸(長度、寬度和厚度)。然而,當正極和負極銅排在結構上被設計為相互平行層疊,且中間僅被極薄的介電材料隔開時,流經這兩層導體的電流在宏觀上是完全鏡像的——即電流幅值完全相等,但流動方向絕對相反 。根據安培環路定律 (Ampere's Law) 以及右手螺旋定則,這兩股反向電流會在其周圍空間激發出極性完全相反的磁通量矢量。由于兩層銅排之間的幾何間隔距離(絕緣層厚度)相對于它們的寬度和長度而言極其微小,這些極性相反的磁場幾乎占據了相同的物理空間體積,從而在空間中發生強烈的矢量相加,實現了磁場能量的相互抵消 。

這種深度的磁場抵消效應會促使互感 (M) 的數值無限趨近于正負極自感 (Lp? 和 Ln?) 的算術平均值。隨著 2M 的值不斷逼近 Lp?+Ln? 的總和,整個母排的總等效電感 Leq? 便會呈現出漸進趨零的態勢。通過三維有限元分析 (3-D FEA) 模擬以及電磁學解析推導,可以得出平行板疊層母排的等效雜散電感近似公式為:

Leq?≈wμ0?μr??l?d?

在這個近似表達式中,μ0? 代表真空磁導率,μr? 代表層間絕緣介質的相對磁導率,l 代表電流換流回路的有效物理長度,w 代表母排導電板的物理寬度,而 d 則是分隔正負極導電板的絕緣介質層的厚度 。

這一基礎的比例關系為疊層母排的結構工程設計確立了不可動搖的最高準則:

- 最小化極間絕緣距離 (d): 在不違背中壓系統介電擊穿閾值的前提下,絕緣層的厚度必須被壓縮到物理材料科學所允許的理論極限 。

- 最大化導體寬度 (w): 更寬的導電板能夠將高頻電流密度均勻地分散到更廣闊的橫向表面積上,從而有效降低局部區域的磁場強度集中現象 。

- 最小化回路長度 (l): 直流母線 (DC-link) 支撐電容器組與 SiC MOSFET 功率端子之間的物理距離必須經過嚴酷的結構優化,以形成盡可能短的電流換流回路 (CCL) 。

頻域特性:趨膚效應與鄰近效應的動態干預

在配備 SiC MOSFET 的中壓高頻應用中,母排的頻域特性絕不能被視作恒定不變的靜態參數。SiC 器件極高的 di/dt 瞬變直接等效于向系統中注入了包含極高頻率(甚至延伸至兆赫茲 MHz 級別)的豐富諧波內容 。在如此高頻的電磁環境下,假設電流在母排導體截面上呈現均勻分布的經典直流理論將徹底失效,取而代之的是由高頻電磁場引發的趨膚效應 (Skin Effect) 和鄰近效應 (Proximity Effect) 。

趨膚效應會迫使高頻交變電流不斷向導體的外表面區域擠壓,這種物理現象實質上急劇縮減了電流流過的有效橫截面積,導致導體的交流 (AC) 電阻在極高頻下呈現指數級上升。與此同時,鄰近效應——由相鄰且流過反向電流的極板之間強烈的交叉磁場驅動——會迫使電流密度高度集中在正極板和負極板相互正對的內表面上。盡管從電磁學的角度來看,鄰近效應有助于進一步壓縮有效磁回路的空間截面積(從而在微觀層面上能夠邊緣性地降低極高頻率下的雜散電感),但這導致電流密度的極度不均勻分布,使得局部區域的 I2R 熱損耗急劇放大 。

因此,在進行母排結構優化時,必須在銅排的厚度與高頻電流分布規律之間尋找精確的平衡點。單純為了增加載流截面積而一味加厚銅排,在極高頻應用中是徒勞的,因為超出趨膚深度限制的厚度部分根本沒有電流流過,它不僅無法帶來任何電氣性能的提升,反而會徒增系統的重量、熱容負擔以及制造成本。

SiC MOSFET 開關瞬態的動態耦合與電磁干擾(EMI)機制

為了將抽象的雜散電感理論置于實際應用語境中,必須深入剖析雜散電感如何與當代工業級 SiC MOSFET 模塊的開關行為發生劇烈的動態耦合。

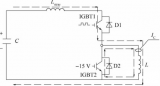

關斷瞬態:電壓過沖與 RBSOA 威脅

在器件的關斷過程 (Turn-off Transient) 中,電感效應表現出最具破壞性的一面。關斷過程可細分為幾個特征階段:包括關斷延遲階段(柵源電容 CGS? 和柵漏電容 CGD? 開始放電)、米勒平臺階段(漏源電壓 VDS? 開始急劇上升)以及后續的電流換流階段(負載電流從 SiC MOSFET 強制轉移至續流二極管或反并聯同步整流管)。

在電流急劇下降的階段,主功率回路中由于雜散電感的存在,會依據法拉第電磁感應定律產生一個強烈的正向感應電動勢。這個由 Lstray??di/dt 引發的電壓尖峰會直接疊加在額定的直流母線電壓之上,使得器件兩端承受的實際瞬態電壓遠超其穩態運行值。這一現象構成了對 SiC MOSFET 反向偏置安全工作區 (Reverse Bias Safe Operating Area, RBSOA) 的直接威脅 。一旦瞬態峰值電壓突破器件的雪崩擊穿極限,模塊將面臨不可逆的物理損壞。

開通瞬態:損耗博弈的悖論

有趣的是,雜散電感在開關周期中扮演著一把雙刃劍的角色。在開通瞬態 (Turn-on Transient) 期間,較大的回路電感 (Lloop?) 會依據楞次定律,從本質上阻礙電流的快速上升。由于電感兩端的電壓降與電流的變化率成正比,這一感應電壓降會在電流上升期間瞬間抵消一部分施加在 MOSFET 上的漏源電壓 (VDS?)。結果是,較高的雜散電感在物理上人為地減少了開通期間電壓與電流的重疊面積,從而導致開通開關能量損耗 (Eon?) 呈現出反常的下降趨勢 。

然而,這種開通損耗的減少絕對不是一種值得追求的設計目標。因為在關斷階段,情況完全反轉。電流的快速切斷產生的正向電壓尖峰,迫使 MOSFET 在承受高電壓的同時切斷高電流,這極大地惡化了關斷開關能量損耗 (Eoff?) 。在總體能量平衡中,由電壓過沖和伴隨的寄生振蕩所引發的 Eoff? 劇增,其帶來的熱懲罰遠遠超過了 Eon? 的虛假減少。因此,通過高度優化的疊層母排來最小化整體回路電感,仍然是最大化總開關效率并確保器件安全運行的絕對先決條件 。

高頻振蕩(Ringing)與 EMI 挑戰

除此之外,雜散電感與器件自身寄生參數的相互作用是電磁干擾 (EMI) 的核心根源。寄生電感與 SiC MOSFET 固有的輸出電容 (Coss?) 會構成一個高Q值的 LC 諧振諧振腔(Tank Circuit)。在開關動作的瞬間,由于極高的 dv/dt 激勵,這一 LC 諧振腔會被激發,在關斷電壓波形上產生持續時間長、幅度劇烈的高頻振蕩 (Ringing) 現象 。

相較于傳統的硅基 IGBT,SiC MOSFET 具有極其微小的輸出電容 (Coss?)。根據諧振頻率公式 f=1/(2πLC

?),極小的 Coss? 會導致振蕩頻率大幅度向極高頻頻段偏移,通常進入數十兆赫茲 (MHz) 的區間 。這種高頻 EMI 輻射極具穿透力和破壞性,傳統的專為低頻硅基 IGBT 系統設計的無源 EMI 濾波器在這種極高頻分量面前通常完全失效,除非對其進行徹底的重構 。這也進一步凸顯了從物理源頭(即母排結構)抑制雜散電感,遠比在事后添加龐大且昂貴的 EMI 濾波器更為明智和關鍵。

結構工程精髓:換流回路(CCL)的拓撲優化設計

一項無懈可擊的高壓大功率結構設計,絕不能僅僅停留在基礎的平行導電板概念上,它必須深度契合逆變器特定電路拓撲的嚴苛物理與電氣約束。結構設計的核心宏觀目標,是由半導體功率模塊端子與直流鏈路電容器陣列的空間物理排布所共同主導的 。

多電平 CCL 架構與電磁對稱性法則

在標準的兩電平電壓源逆變器中,主電流換流回路相對簡單,它由直流母線電容器、正極母排層、上橋臂 SiC MOSFET、下橋臂 SiC MOSFET(或續流二極管)以及負極母排層構成 。然而,隨著中壓應用(如 1000V 至 1500V 系統)的不斷推進,多電平轉換器拓撲——例如中性點鉗位 (NPC) 或有源中性點鉗位 (ANPC) 逆變器——正成為行業標準,以有效降低單個開關管承受的電壓應力 。

多電平拓撲在結構上要求使用高度復雜的多層疊層母排,通常是三層(正極、中性點/零線、負極)甚至五層結構 。在這樣的三層結構中,換流回路會根據不同的開關狀態發生動態的重疊和切換。正極輸出支路的雜散電感 (Lbus+?)、零線支路的雜散電感 (Lbus0?) 以及負極支路的雜散電感 (Lbus??) 之間存在著持續且復雜的電磁耦合相互作用 。

多層母排設計中最為致命的結構性挑戰,在于維持絕對的電磁對稱性。在多相并聯支路或復雜的橋臂結構中,任何微小的非對稱雜散電感都會引發災難性的系統失衡。具體而言,電感的不均等會導致在并聯運行的相同 SiC 模塊之間出現截然不同的瞬態電壓過沖,更嚴重的是,它會破壞動態電流的均流特性。這種不平衡會迫使系統中某一個模塊長期承受更高的熱應力和電壓應力,導致其在功率循環中加速老化,最終使整個系統的可靠性出現木桶效應式的崩塌 。

為了實現真正的電磁對稱,母排的物理走線必須進行嚴密的幾何鏡像設計,確保所有并聯換流路徑的物理長度和截面體積絕對一致。此外,對于母排上為方便端子螺栓連接而不可避免開設的安裝孔、切口和開縫設計,必須經過精細的工程評估。因為這些物理空洞會強制電流偏離直線路徑發生繞流,從而在局部區域摧毀了正負極磁場的抵消效應,導致該局部的雜散電感出現離散的、脈沖式的尖峰激增 。

連接點間距的微觀幾何學與電容陣列分布策略

功率模塊端子與電容器排連接節點之間的離散幾何間距,在物理層面上直接決定了換流回路所包圍的總空間面積。以嚴密的三維 FEA 仿真為支撐的解析推導明確證明,系統雜散電感與連接點之間的絕對物理距離呈現出高度的正比例線性關系 。基于此,結構布局的最高準則必須是將高頻去耦電容器組極度密集地簇擁在 SiC 模塊的功率端子周圍,不留任何冗余的布線空間。

在電容陣列的排布策略上,采用分布式布置多個小容量電容器并聯的結構,其電感抑制效果在物理學上具有壓倒性優勢,遠勝于采用單一的、具有同等容量的巨型電容器。實證研究數據顯示,當以三電容器并聯陣列取代單電容器結構時,換流回路的整體雜散電感可銳減 25% 。這種并聯拓撲通過將高頻瞬態 di/dt 需求有效分散到多個并聯的物理支路中,巧妙利用了并聯電感等效值大幅降低的基礎電路原理 。同時,分布式并聯電容的部署強制電流在母排的整個寬度上更均勻地分布,有效遏制了因電流在單一注入點過度集中而引發的局部毀滅性熱斑(Thermal Hot-spots)現象 。

中壓高頻運行環境下的絕緣協調與局部放電(PD)深度抑制

雖然通過極盡所能地縮減電介質層的厚度 (d) 是降低疊層母排寄生電感的最有效數學途徑 (Leq?∝d/w),但這種在幾何尺寸上的極致壓縮,直接且粗暴地對系統的介電完整性構成了巨大威脅。在中等電壓級別(從常見的 1200V 延伸至數千伏的高鐵牽引與智能電網系統)的應用環境中,電氣絕緣系統無時無刻不在承受著極端且高頻重復的電壓應力考驗 。

SiC時代局部放電(PD)的致命威脅

對于現代疊層母排而言,其最隱蔽且最致命的首要失效模式往往并非由于瞬時過壓導致的直接介電擊穿,而是局部放電 (Partial Discharge, PD) 效應的長期、潛伏性侵蝕。局部放電是指在絕緣介質內部微小的氣隙、空洞、層間剝離處,或者在導體極板邊緣那些電場線高度集中的尖銳區域,發生的局部微小電氣放電現象 。

引入 SiC MOSFET 技術使得局部放電的環境條件發生了質的惡化。傳統針對硅基設備采用的基于 50/60 Hz 低頻正弦波的局部放電測試標準,對于 SiC 系統而言已完全失效且不具備參考價值。SiC 逆變器在運行中產生的是高頻、單極性的方波電壓,伴隨著動輒超過 50 V/ns 甚至 100 V/ns 的極端 dv/dt 轉換速率。這種極端的邊沿跳變向介電材料內部注入了巨大的位移電流 。這種高頻、高強度的重復電應力會大幅拉低局部放電起始電壓 (Partial Discharge Inception Voltage, PDIV),并急劇加速聚合物絕緣材料的碳化和物理侵蝕進程,最終不可避免地演變為正負極導電板之間的災難性短路故障 。

此外,在諸如多電飛機 (More-Electric Aircraft, MEA) 等嚴苛的航空航天應用中,環境因素引入了額外的危害維度。根據帕邢定律 (Paschen's Law),在飛機處于高海拔飛行時所面臨的低氣壓環境下,空氣的擊穿電壓閾值會出現斷崖式的下跌 。這意味著在非增壓艙區域運行的功率轉換器,其母排裸露邊緣發生電暈放電的風險呈指數級上升 。

協同設計的藝術:電感與 PDIV 的平衡邊界

為了消解超低電感(必然要求絕緣層極薄)與超高 PDIV(必然要求絕緣層極厚)之間不可調和的物理學矛盾,結構工程師必須實施一套全方位的電氣-材料-機械協同設計戰略:

- 高階介電材料體系的遴選: 在中壓 SiC 的高頻高應力環境下,傳統的 FR4 環氧玻纖板或常規的聚對苯二甲酸乙二醇酯 (PET) 薄膜往往因耐熱老化和抗電場能力不足而敗下陣來 。工程師必須轉向具有卓越介電強度、優異高溫耐受性且具有極低相對介電常數 (μr?) 的尖端材料,如聚酰亞胺 (Polyimide, PI) 薄膜、特殊配方的摻雜環氧樹脂,乃至于具有極強抗等離子體侵蝕能力的無機駐極體 (Electret) 絕緣材料 。無機材料的引入顯著提升了材料抵抗局部放電微電弧燒蝕的物理壽命 。

- 邊緣工程學與電場梯度均化: 在微觀電磁學中,電場強度 (E) 會在導體的尖角和銳利邊緣處發生極度集中的畸變。如果疊層母排直接采用未經處理的、沖壓剪切后邊緣粗糙的原始銅排,那么在這些邊緣極易發生電暈放電,其起始電壓遠低于母排中央平坦區域的理論擊穿極限。結構優化的鐵律要求,所有導體的外圍邊緣、端子切口、螺栓孔洞必須經過精密的機械加工倒角處理(Radiusing),以最大限度地鈍化和平滑電場梯度 。

- 全密封灌封與爬電距離重構: 為了增加表面爬電距離并徹底消除正負極板交界處最脆弱邊緣區域的微小氣隙,母排必須進行徹底的絕緣封裝。采用先進的邊緣密封技術——諸如熱壓熱塑性絕緣粘合劑或在周邊邊緣灌注高性能絕緣樹脂——將高電場集中區域與外部環境中的環境濕度和低壓空氣徹底物理隔離,從而實現 PDIV 閾值的大幅度躍升 。

通過嚴密的數學物理建模與材料科學的結合,實現既完全避免局部放電又無需犧牲動態電感性能的完美母排是可能的。最新的工程實例表明,針對 3 電平中壓轉換器深度優化的母排,在模擬 0.2 個標準大氣壓的高空惡劣條件下,其實測 PDIV 能夠比系統額定電壓高出 43%,而與此同時,其寄生雜散電感被不可思議地控制在僅為 12.0 nH 的微小水平 。

工業級與車規級 SiC 模塊的實證分析:基于高功率模塊的性能全景解析

脫離了具體功率模塊實際特性的母排設計只能停留在理論沙盤上。為了準確界定疊層母排電感優化的邊界條件,必須對當今尖端工業級 SiC MOSFET 模塊的封裝寄生參數與開關動態進行深入的實證解析。

以碳化硅功率器件領軍企業基本半導體(BASiC Semiconductor)的 BMF 系列 1200V 中壓大功率模塊為例,我們可以觀察到當模塊電流從數十安培跨越至數百安培時,模塊封裝技術與系統母排設計的極度耦合關系。

表 1:BASiC Semiconductor 1200V SiC MOSFET 模塊開關及寄生電感特性全景數據表

| 模塊型號 | 封裝類型 | 額定電流 (ID?) | 導通電阻 (RDS(on)? Typ. @ 25°C) | 上升/下降時間 (tr? / tf? @ 25°C) | 開關能量損耗 (Eon? / Eoff? @ 25°C) | 寄生電感參數 (Lp? / 測試 Lσ?) |

|---|---|---|---|---|---|---|

| BMF008MR12E2G3 | Pcore?2 E2B | 160 A (@ 80°C) | 8.1 mΩ | 39 ns / 26 ns | 2.3 mJ / 0.7 mJ | Lp?=8 nH, Lσ?=30 nH |

| BMF60R12RB3 | 34 mm | 60 A (@ 80°C) | 21.2 mΩ | 28.7 ns / 35.7 ns | 1.7 mJ / 0.8 mJ | Lσ?=40 nH |

| BMF80R12RA3 | 34 mm | 80 A (@ 80°C) | 15.0 mΩ | 35.4 ns / - | 2.4 mJ / 1.0 mJ | Lσ?=40 nH |

| BMF120R12RB3 | 34 mm | 120 A (@ 75°C) | 10.6 mΩ | 96 ns / 39 ns | 6.9 mJ / 3.0 mJ | Lσ?=40 nH |

| BMF160R12RA3 | 34 mm | 160 A (@ 75°C) | 7.5 mΩ | 95 ns / 41 ns | 8.9 mJ / 3.9 mJ | Lσ?=40 nH |

| BMF240R12E2G3 | Pcore?2 E2B | 240 A (@ 80°C) | 5.5 mΩ | 40.5 ns / 25.5 ns | 7.4 mJ / 1.8 mJ | Lσ?=20 nH |

| BMF240R12KHB3 | 62 mm | 240 A (@ 90°C) | 5.3 mΩ | 37 ns / 36 ns | 11.8 mJ / 2.8 mJ | Lσ?=30 nH |

| BMF360R12KHA3 | 62 mm | 360 A (@ 75°C) | 3.3 mΩ | 107 ns / 34 ns | 12.5 mJ / 6.6 mJ | Lσ?=30 nH |

| BMF540R12KHA3 | 62 mm | 540 A (@ 65°C) | 2.2 mΩ | 89 ns / 39 ns | 37.8 mJ / 13.8 mJ | Lσ?=30 nH |

| BMF540R12MZA3 | Pcore?2 ED3 | 540 A (@ 90°C) | 2.2 mΩ | 101 ns / 41 ns | 15.2 mJ / 11.1 mJ | Lσ?=30 nH |

(注:上述數據提煉自 BASiC Semiconductor 的目標與初步規格書,開關參數通常在極其嚴苛的雙脈沖動態測試標準下測得,如典型的 VDS?=800V, 額定 ID?, 且 VGS?=+18V/?4V 或 ?5V。其中 Lσ? 指代在進行動態特性提取時系統外部測試回路所被強制規定的最大允許雜散電感,而 Lp? 則是功率模塊封裝內部不可避免的本征電感參數。針對部分 62mm 模塊,其絕緣規范同樣嚴苛,如 BMF240R12KHB3 和 BMF360R12KHA3 明確標定了高達 32.0 mm 的爬電距離和 8.7 mm 的電氣間隙,這進一步印證了前文所述介電設計面臨的巨大空間壓力。)

性能維度矩陣深層解析

對上述實證數據的匯總與透視,揭示了模塊功率容量、底層封裝架構與外部母排電感容忍度之間錯綜復雜的二階與三階物理映射關系。

1. 電流密度縮放與容性負載爆炸帶來的 di/dt 深淵: 隨著 SiC 模塊額定電流從基礎的 60A (BMF60R12RB3) 一路狂飆至巨無霸級別的 540A (BMF540R12MZA3) ,為了處理如此龐大的電流通流能力,模塊內部不可避免地并聯了數量眾多的 SiC 裸芯片 (Bare Die)。這種并聯直接導致了模塊總柵極電荷 (QG?) 和輸入結電容 (Ciss?) 呈倍數級爆炸。數據表明,60A 模塊的 Ciss? 尚停留在可控的 3.85 nF ,而 540A 旗艦模塊的 Ciss? 則飆升至驚人的 33.6 nF ;相應的總柵極電荷 QG? 也從 168 nC 跨越式增長至 1320 nC 。

然而,最令結構工程師不寒而栗的是,盡管內部硅片面積和容性負載急劇增加,這些 SiC 模塊的開關速度——尤其是決定系統 dv/dt 和 di/dt 惡劣程度的下降時間 (tf?)——依然保持在極度駭人的快水平。例如,BMF540R12KHA3 模塊能夠在區區 39 ns 的極短時間內瞬間切斷高達 540A 的主級大電流 。進行基礎物理換算可知,其原生的、未經任何緩沖抑制的 di/dt 竟然超過了 13.8 kA/μs。如果我們在這個系統中沿用傳統設計的、具有 100 nH 雜散電感的普通母排,那么根據感應電壓方程,該瞬間產生的電壓尖峰將高達 V=(100×10?9)?(13.8×109)=1380V。將這 1380 V 的尖峰無情地疊加在 800V 的穩態直流母線上,瞬態絕對峰值電壓將飆升至 2180 V,這將瞬間徹底擊穿并焚毀耐壓僅為 1200V 的 SiC MOSFET 。

這種物理現實無情地證明:隨著功率密度的攀升,系統留給母排雜散電感的容錯空間正在呈指數級萎縮。這一點在半導體原廠極其嚴苛的測試條件中得到了最直觀的印證:對于較小電流的 34mm 封裝模塊 (60A-160A),原廠允許測試回路電感 (Lσ?) 放寬至 40 nH ;但在測試采用先進 Pcore?2 E2B 封裝、具備極高開關能量密度的 240A 模塊 (BMF240R12E2G3) 時,原廠測試條件竟然強制要求外部 Lσ? 被死死壓制在 20 nH 的超低紅線內 。這即是對終端工程師發出的最強烈的工程設計警告。

2. 內部封裝電感 (Lp?) 倒逼外部疊層母排的極限挑戰: 系統的極限性能永遠受制于短板。在當代功率電子中,互連總電感的絕對下限是由功率模塊自身的內部封裝電感 (Lp?) 所劃定的基準線。以 BASiC 的 BMF008MR12E2G3 為例,該模塊采用了革命性的 Pcore?2 E2B 封裝架構,通過完全摒棄傳統的長鋁線鍵合 (Wire-bonding) 轉向直接引線或燒結等先進工藝,成功將其內部寄生電感 Lp? 鎮壓在了不可思議的 8 nH 。

這一封裝領域的重大突破,將極度沉重的壓力完全傳導給了外部疊層母排的設計者。假設一個模塊本身僅有 8 nH 的內部電感,如果系統工程師為其匹配了一塊設計粗糙、具有 50 nH 電感的外部母排,那么模塊封裝所付出的巨大成本和技術進步將被外部互連的愚蠢所徹底抹殺。因此,結構工程師的使命被重新定義:疊層母排在換流回路中貢獻的電感量,必須在物理上與模塊極其微小的內部 Lp? 達到等量齊觀的同一量級(即進入個位數或 10 納亨以內的微觀領域)。

3. 開關損耗的熱動力學分歧: 通過橫向比對表格中的開關能量數據,可以清晰地識別出溫度波動對開關動態特性的深遠影響。例如,隨著結溫 (Tvj?) 從理想的 25°C 攀升至 175°C 惡劣工況下,幾乎所有模塊的開關損耗都出現了明顯的惡化。以 BMF240R12KHB3 為例,其開通損耗 Eon? 從 11.8 mJ 微增至 11.9 mJ,但其關斷損耗 Eoff? 卻從 2.8 mJ 躍升至 3.1 mJ 。這一數據特征進一步強化了前文的理論論斷:即由寄生電感在關斷瞬間引發的電壓尖峰與電流拖尾相互疊加,在高溫高壓環境下對 Eoff? 構成了最為致命的懲罰,也由此鎖死了系統熱管理設計的最終紅線。

突破物理極限:緩沖電路集成與混合母排協同架構

當平行金屬板的幾何尺寸壓縮與介電材料的極限變薄已經觸及了物理學定律的硬性天花板,且無法再進一步榨取電感降低的紅利時,必須引入主動的電氣-結構協同整合戰略,以進一步在微觀層面上縮小“有效”高頻換流回路的面積 。

吸收電路與去耦電容器的嵌入式集成

壓制殘余系統雜散電感的最前沿且最立竿見影的技術手段,是將緩沖電路 (Snubber Circuits) 或超高頻去耦電容器在物理結構上直接并聯并嵌入到疊層母排的銅層網絡中 。

盡管大容量、大體積的主直流鏈路薄膜電容器組能夠提供充沛的體量級能量儲備,但受制于其龐大卷繞結構帶來的較高內部等效串聯電感 (ESL) 以及其距離 SiC 模塊不可忽視的物理距離,它們必然構成一個具有明顯響應延遲的“宏觀換流回路 (Macro-commutation Loop)”。為了打破這種延遲,通過在結構上將具有極低 ESL 的高頻多層陶瓷電容器 (MLCC) 或專用的薄膜緩沖電容器緊貼著 SiC 模塊的 DC+ 和 DC- 功率端子直接貼裝,系統便奇跡般地開辟出了一個極其緊湊的“微觀換流回路 (Micro-commutation Loop)” 。

在關斷瞬態最為關鍵且狂暴的幾納秒內(即 VDS? 急劇上升、電流急劇下降的階段),洶涌的高頻諧波瞬態電流能夠智能地繞過具有較高電感阻抗的主母排宏觀回路,直接灌入并被吸收于這些本地化的微型去耦電容器中 。當前最尖端的混合母排 (Hybrid Busbar) 結構,甚至采用將印刷電路板 (PCB) 緩沖網絡直接焊接或機械壓合到大功率層壓銅排之上的方式,以此作為這些高頻去耦電容的物理載體 。

這種微觀層面的結構與電氣協同,帶來的工程實效是顛覆性的。權威的實驗室測試數據毫不留情地證明了這一論斷:在靠近模塊端子處僅僅策略性地并聯一顆容量僅為 0.1 μF 的高頻緩沖電容,就能將整個換流回路的有效寄生電感極其暴烈地砍掉 46.4%。電感的銳減隨即帶來了振蕩尖峰的被抹平,這種立竿見影的抑制效果最終轉化為系統總動態開關損耗高達 30.8% 的顯著下降 。但需要格外警惕的是,在設計這類緩沖網絡時,必須對阻容網絡中阻尼電阻自身的寄生電感進行最嚴格的核算與控制,因為過大的電阻寄生電感將直接抵消零極點配置所帶來的阻尼抑制效應,使得系統依然深陷致命的高頻振蕩泥潭無法自拔 。

基于熱-電雙重拓撲的結構重塑

最后,絕不能忽視疊層母排在高功率逆變器熱管理拓撲架構中所扮演的核心角色。SiC MOSFET 模塊,尤其是如同 BMF540R12MZA3 這類需要常態化處理 540A 恐怖電流的龐然大物,由于不可避免的高頻動態開關動作以及龐大的電流引起的 I2R 歐姆熱,會在端子根部產生密度極其驚人的局部極端熱通量。此時,疊層母排內部那些寬闊、連續的純銅或純鋁導電平面,自然而然地蛻變為性能卓絕的高效均熱板 (Thermal Spreaders) 。

通過將大電流下的焦耳熱生成模型與 3D FEA 電磁模型進行多物理場耦合分析,結構工程師能夠精準定位系統熱斑,并針對性地在高電流密度核心區局部增加銅排厚度,或設計特殊的導熱凸臺。這種精巧的結構規劃能夠將淤積在半導體端子根部的極高熱量,通過低熱阻路徑順暢地向外引導至專門配備的風冷散熱器或高流量液冷冷板中 。這種身兼二職的結構二元性設計——它在電學上是承擔著納米級電感響應的終極高速公路,在熱學上又是維持系統熱力學平衡的骨干導熱橋梁——完美詮釋了高功率密度逆變器結構集成的至高境界 。

全局綜合與結構工程設計導則

碳化硅技術的爆發式發展,已經將半導體底層固體物理學的性能邊界,與功率分配系統中宏觀機械結構工程的精密程度不可逆轉地捆綁在了一起。疊層母排早已不再是一件僅僅用于連接正負極的被動金屬導電線束,而是主動定義并最終決定逆變器系統轉換效率、開關穩定性、以及全生命周期運行壽命的最核心瓶頸元件。

基于對電磁場理論、介電絕緣力學機制以及前沿 SiC 大功率模塊實證開關動態的 Exhaustive 綜合分析,面向中壓 SiC 系統的疊層母排最優設計,必須堅定不移地貫徹以下具有絕對約束力的結構工程戰略導則:

- 換流回路 (CCL) 物理面積的絕對極小化: 結構布局必須在三維空間中被“暴力”優化,迫使直流鏈路的儲能電容器組在物理距離上最大限度地逼近半導體模塊的功率端子。因為在基礎物理學中,電流活動開關路徑所包圍的幾何面積,直接且唯一地決定了基礎雜散電感的底數 。

- 通過鏡像幾何平面最大化互感磁場抵消效應: 承載相反方向大電流的正負極導電層 (DC+ 和 DC-) 必須在空間上呈現完美的平行與重疊幾何態勢。模塊的輸入端子應設計為居中對齊、上下重疊,這不僅提供了最短的有效傳導路徑,更引發了最大程度的電磁場抵消,從而驅動 2M 互感變量去無情地抵消單層導體的自感 。

- 強制推行無差別的電磁物理對稱性: 在應對多電平 (如 3-Level NPC/ANPC) 復雜拓撲或面對龐大的多模塊并聯陣列時,各并聯支路的電流路徑走向必須實現絕對的物理和幾何等效。任何微小的非對稱雜散電感分配,都將直接導致動態電流均流機制的崩潰,進而引發并聯模塊間嚴重的局部過熱和致命的電壓應力過載 。

- 高頻高壓局部放電 (PD) 與極低電感的博弈與共決: 在中壓絕緣設計中,必須在極限降低介電厚度(以追求微納級電感)與抵抗高 dv/dt 誘發的嚴重局部放電之間做出最精妙的取舍。強行采用具有極高介電常數和抗電弧侵蝕能力的無機駐極體絕緣材料,嚴酷地要求對所有鋒利的金屬切割邊緣進行大半徑倒角圓滑處理,并采用真空灌封技術對母排邊界進行氣密性包裹,是在惡劣中壓環境(特別是航空低氣壓)下維持系統長久可靠性的唯一出路 。

- 去耦電容的分層架構與微觀環路集成: 大型主 DC-link 電容必須降級為宏觀儲能池,而在 SiC 模塊端子的毫米級范圍內,必須強制集成具備極低 ESL 特性的高頻吸收/去耦電容器。這種物理上的微環路構建能夠將致命的高頻開關諧波就地分流,以腰斬級別的幅度拉低有效換流回路電感,并帶來瞬態開關損耗的斷崖式下降 。

審核編輯 黃宇

-

雜散電感

+關注

關注

0文章

33瀏覽量

6612 -

疊層母排

+關注

關注

0文章

6瀏覽量

1395

發布評論請先 登錄

MPO分支光纜:高密度光纖布線的核心組件

疊層固態電容:小型化封裝,釋放PCB更多空間

哪種工藝更適合高密度PCB?

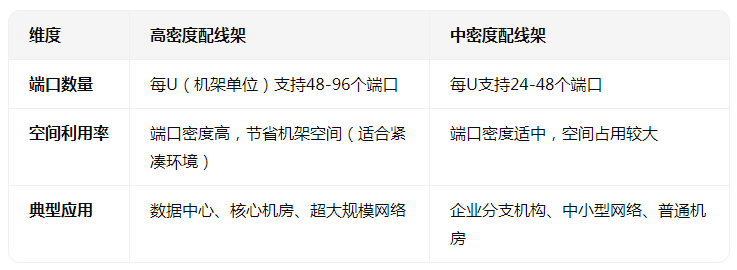

高密度配線架和中密度的區別有哪些

?協作機器人關節模組空間緊張?高密度MLCC與功率電感方案?

貼片電感代理-疊層電感的實際應用

高密度配線架和中密度的區別

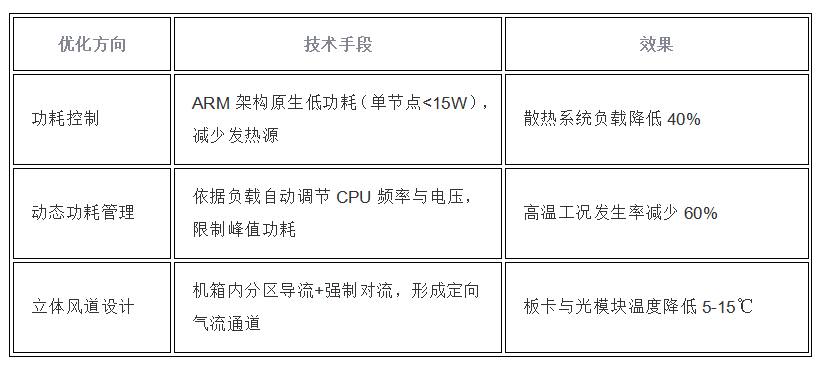

高密度ARM服務器的散熱設計

基于疊層組裝和雙腔體結構的高密度集成技術

高密度疊層母排 (Laminated Busbar) 雜散電感優化指南

高密度疊層母排 (Laminated Busbar) 雜散電感優化指南

評論