在FPGA開發(fā)中,時序收斂往往是項目后期最令人頭疼的環(huán)節(jié)。許多工程師都有過這樣的經(jīng)歷:RTL仿真通過,綜合布線后卻出現(xiàn)大量時序違例,為了滿足時序不得不反復(fù)修改代碼、調(diào)整約束,甚至重構(gòu)設(shè)計。一次偶然的高速DDR接口調(diào)試,讓我深刻體會到,時序問題遠不止“跑慢一點”那么簡單,它涉及器件結(jié)構(gòu)、時鐘特性、約束策略和工具理解的方方面面。

一、問題的浮現(xiàn):看似正確的設(shè)計為何時序違例?

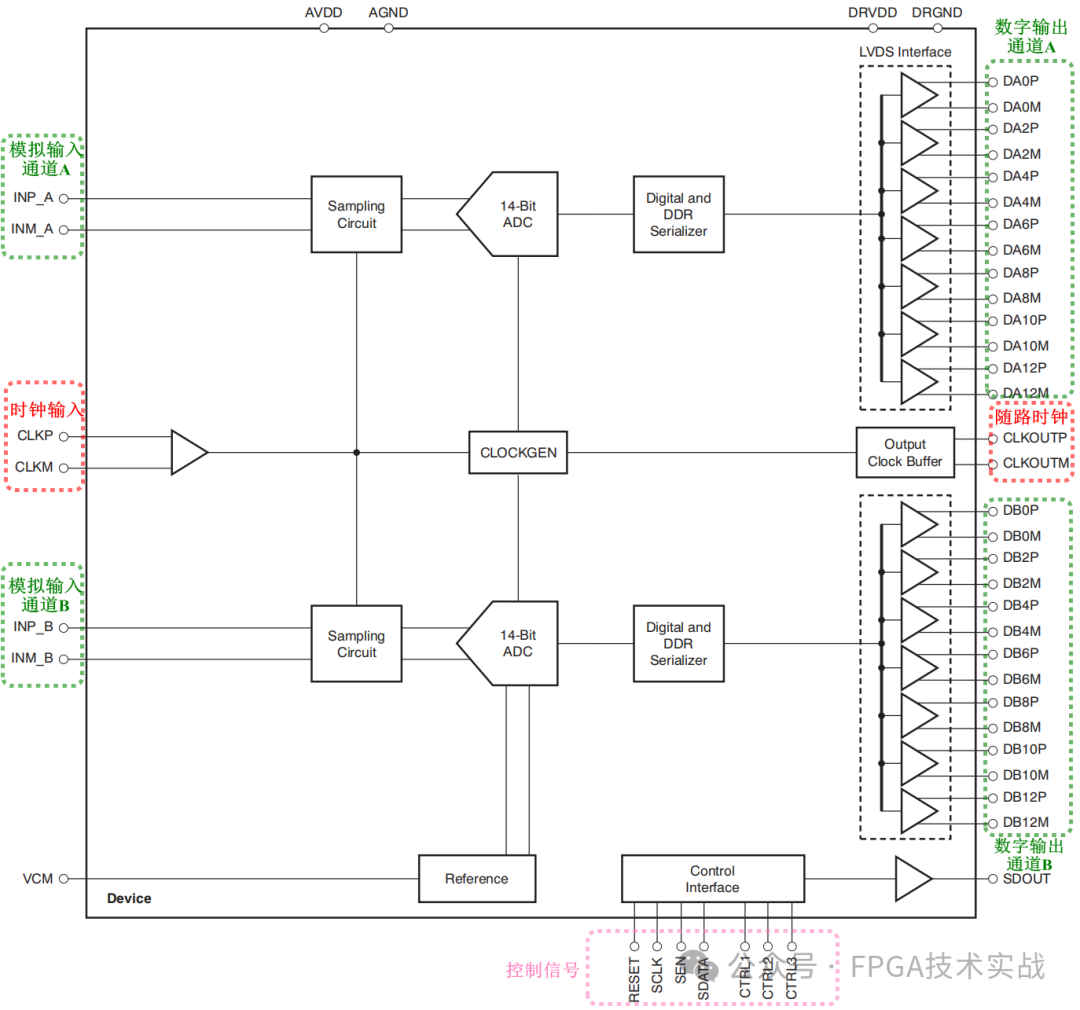

某項目需要實現(xiàn)一個基于Xilinx FPGA的高速數(shù)據(jù)采集系統(tǒng),前端采用JESD204B接口的ADC,后端通過DDR4緩存數(shù)據(jù)。按照常規(guī)流程完成代碼編寫和功能仿真后,進入Vivado實現(xiàn)階段。結(jié)果在時序報告中,發(fā)現(xiàn)setup違例嚴重,關(guān)鍵路徑集中在JESD204B物理層到用戶邏輯的數(shù)據(jù)轉(zhuǎn)換模塊,以及DDR4控制器與用戶接口的跨時鐘域部分。

起初懷疑是代碼風(fēng)格問題,但優(yōu)化RTL后改善有限。進一步分析時序報告,發(fā)現(xiàn)許多違例路徑涉及從PLL輸出的時鐘,但時鐘約束并不完整;同時,跨時鐘域的異步FIFO被工具誤判為需要嚴格時序的路徑,導(dǎo)致不必要的約束過緊。

二、時序分析的底層邏輯

FPGA時序分析的核心在于靜態(tài)時序分析(STA),它基于器件的物理特性和設(shè)計網(wǎng)表,計算所有路徑的建立時間和保持時間裕量。理解STA需要從基本電路層面把握數(shù)字電路的功能和時序參數(shù):觸發(fā)器的setup/hold時間、組合邏輯的傳播延遲、時鐘偏斜等。

FPGA內(nèi)部資源豐富,包含查找表、觸發(fā)器、塊RAM、DSP、時鐘管理單元(如MMCM/PLL)和高速收發(fā)器。每種資源的時序特性各不相同,設(shè)計時必須考慮其在芯片上的實際位置和布線延遲。Vivado等工具通過分析這些物理信息,生成詳盡的時序報告,但前提是開發(fā)者必須提供正確的約束,告訴工具時鐘頻率、相位關(guān)系、I/O延時等關(guān)鍵參數(shù)。

三、時序約束:被低估的關(guān)鍵環(huán)節(jié)

時序約束是連接設(shè)計意圖與工具分析的橋梁,但往往被輕視。常見的問題包括:

時鐘約束不全:主時鐘、衍生時鐘(PLL分頻、計數(shù)時鐘)、高速收發(fā)器時鐘未正確定義,或時鐘組關(guān)系未指明,導(dǎo)致工具無法準確計算跨時鐘域路徑。

I/O約束缺失或錯誤:輸入輸出延時(input/output delay)未根據(jù)外部器件時序建模,導(dǎo)致接口時序悲觀或過于樂觀。特別是DDR接口,需要精確約束數(shù)據(jù)和時鐘的對齊關(guān)系。

多周期路徑處理不當:對于邏輯上不需要單周期完成的路徑(如慢速控制信號、跨時鐘域的同步握手),若不使用多周期約束(set_multicycle_path),工具會按最嚴格條件分析,造成虛假違例。

虛假路徑濫用:盲目設(shè)置虛假路徑(set_false_path)可能掩蓋真實時序問題,而該設(shè)的未設(shè)(如異步復(fù)位釋放后的路徑)則徒增工作量。

以JESD204B接口為例,其核心時鐘由收發(fā)器恢復(fù),必須正確約束收發(fā)器輸出時鐘作為生成時鐘,并指定與參考時鐘的關(guān)系。否則,工具會將恢復(fù)時鐘視為獨立時鐘,導(dǎo)致跨時鐘域路徑被過度約束。

四、系統(tǒng)級時序收斂的方法論

解決時序問題不能僅靠“打補丁”,需要系統(tǒng)性的收斂流程:

早期約束介入:在設(shè)計初期就創(chuàng)建完整的時序約束,包括所有時鐘、I/O延時和例外路徑。結(jié)合初步綜合結(jié)果進行時序評估,避免后期大規(guī)模返工。

報告深度解讀:Vivado的時序報告包含路徑詳細信息、邏輯級數(shù)、器件延時占比等。分析違例路徑是組合邏輯過深,還是布線擁塞,或是時鐘偏斜過大,對癥下藥。

優(yōu)化策略分層:

RTL級:控制邏輯級數(shù),合理流水,避免大扇出。

綜合級:使用綜合選項(如retiming、flatten hierarchy)優(yōu)化網(wǎng)表。

實現(xiàn)級:調(diào)整物理優(yōu)化選項(如布局布線努力等級、重定時),嘗試不同策略(如性能探索模式)。

時鐘與復(fù)位設(shè)計:異步時鐘域必須使用可靠的CDC(時鐘域交叉)處理(如異步FIFO、握手協(xié)議);復(fù)位信號需考慮同步釋放,避免亞穩(wěn)態(tài)傳播。

增量式設(shè)計:對于大型系統(tǒng),采用增量編譯可保留已有布局布線結(jié)果,縮短收斂周期,但需注意修改范圍對時序的影響。

五、從工具到設(shè)計:構(gòu)建時序穩(wěn)健的系統(tǒng)

那次調(diào)試最終通過補充收發(fā)器時鐘約束、修正多周期路徑、優(yōu)化跨時鐘域邏輯解決了問題。但更深層的體會是,F(xiàn)PGA時序分析不是孤立的技術(shù),它貫穿于器件選型、架構(gòu)設(shè)計、RTL編碼、約束編寫和調(diào)試驗證的每一個環(huán)節(jié)。

掌握時序分析與優(yōu)化,意味著能夠洞察FPGA底層資源的工作方式,理解工具如何解析約束,并具備從系統(tǒng)層面權(quán)衡性能與資源的視野。中際賽威劉老師根據(jù)課綱分析,對于從事高速接口、復(fù)雜數(shù)字信號處理的工程師而言,這是一項必備的核心能力。唯有系統(tǒng)性地學(xué)習(xí)器件原理、靜態(tài)時序分析理論和工程實踐方法,才能在面對日益增高的設(shè)計頻率時游刃有余。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22421瀏覽量

636631 -

接口

+關(guān)注

關(guān)注

33文章

9526瀏覽量

157097 -

采集系統(tǒng)

+關(guān)注

關(guān)注

0文章

181瀏覽量

22014 -

時序

+關(guān)注

關(guān)注

5文章

407瀏覽量

38881

發(fā)布評論請先 登錄

破解快遞分揀痛點!光子精密顏色傳感器賦能高速分揀提質(zhì)增效

光伏一次調(diào)頻設(shè)備/一次調(diào)頻裝置|光伏一次調(diào)頻涉網(wǎng)試驗/光伏電站一次調(diào)頻建設(shè)改造方案

光伏一次調(diào)頻設(shè)備,光伏電站一次調(diào)頻建設(shè)改造方案

一次消諧器對電力系統(tǒng)的核心貢獻

宇樹人形機器人的配置,核心代碼,調(diào)試方法,二次開發(fā)接口

5G網(wǎng)絡(luò)通信有哪些技術(shù)痛點?

跨越協(xié)議鴻溝:RS485轉(zhuǎn)ETHERCAT網(wǎng)關(guān)在電力電動機保護中的破局之道

RFID珠寶管理方案:破解珠寶行業(yè)管理痛點的智能之道

ADC和FPGA之間LVDS接口設(shè)計需要考慮的因素

STM32H747 USB接口,插拔第一次連接的上,之后就再也連接不上,為什么?

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設(shè)計

FPGA調(diào)試方式之VIO/ILA的使用

智多晶XSBERT讓高速串行接口調(diào)試化繁為簡

一次消諧裝置與二次消諧裝置區(qū)別、一次消諧器與二次消諧器的區(qū)別

FPGA時序收斂的痛點與解決之道——從一次高速接口調(diào)試談起

FPGA時序收斂的痛點與解決之道——從一次高速接口調(diào)試談起

評論