在電子系統(tǒng)設(shè)計(jì)中,晶振負(fù)載電容匹配是確保時(shí)鐘信號(hào)穩(wěn)定傳輸?shù)暮诵沫h(huán)節(jié)。負(fù)載電容(CL)作為晶振諧振電路的關(guān)鍵參數(shù),直接影響晶振的起振條件、頻率穩(wěn)定性及抗干擾能力。本文將從理論推導(dǎo)、工程實(shí)踐及案例分析三個(gè)維度,聊聊晶振負(fù)載電容匹配的底層邏輯與實(shí)施方法。

一、負(fù)載電容匹配的理論基礎(chǔ)

1.晶振等效電路與諧振條件

晶振的等效電路可簡(jiǎn)化為電感L、電容C和電阻R的串聯(lián)模型。當(dāng)輸入信號(hào)頻率與晶體固有頻率一致時(shí),電路發(fā)生共振,產(chǎn)生穩(wěn)定的正弦波輸出。其諧振頻率公式為:

其中,L為晶體等效電感,C為等效電容,R為等效電阻。負(fù)載電容CL需與晶體內(nèi)部電容C形成諧振,否則會(huì)導(dǎo)致頻率偏移或起振失敗。

2.負(fù)載電容的物理意義

負(fù)載電容是晶振輸出端與地之間的等效電容,包含PCB走線電容、芯片引腳電容及外部并聯(lián)電容。其值需滿足:

- 最小負(fù)載電容(CLmin)?:確保晶振在最低溫度下仍能起振;

- 最大負(fù)載電容(CLmax)?:防止高頻噪聲耦合,避免信號(hào)失真。

二、負(fù)載電容匹配的工程推導(dǎo)

1.負(fù)載電容與晶振參數(shù)的關(guān)系

負(fù)載電容CL需與晶振的標(biāo)稱電容C、等效電感L及電阻R匹配。其關(guān)系可表示為:

其中,C為晶體內(nèi)部電容,L為等效電感,R為等效電阻。該公式表明,負(fù)載電容需根據(jù)晶振的內(nèi)部參數(shù)動(dòng)態(tài)調(diào)整,以實(shí)現(xiàn)諧振。

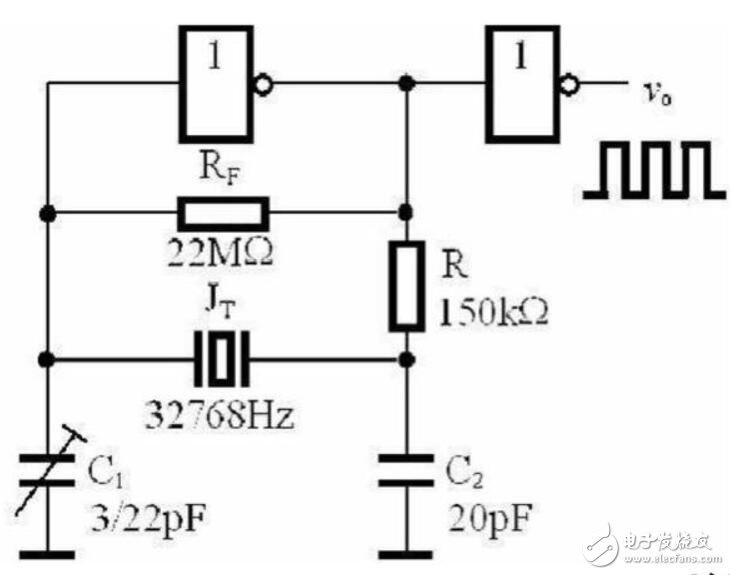

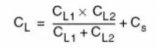

2.負(fù)載電容的計(jì)算方法

- 步驟1:確定晶振標(biāo)稱參數(shù)?

從晶振數(shù)據(jù)手冊(cè)中獲取標(biāo)稱頻率f、等效電感L、等效電阻R及標(biāo)稱電容C。

- 步驟2:計(jì)算理論負(fù)載電容?

根據(jù)諧振頻率公式,計(jì)算理論負(fù)載電容CL:

- 步驟3:調(diào)整實(shí)際負(fù)載電容?

實(shí)際負(fù)載電容需考慮PCB走線電容(通常為5~10pF)及芯片引腳電容(約2~5pF)。例如,某晶振標(biāo)稱電容為30pF,若PCB走線電容為8pF,芯片引腳電容為3pF,則需通過并聯(lián)電容補(bǔ)足19pF(30 - 8 - 3 = 19pF)。

3.負(fù)載電容的容差控制

負(fù)載電容的容差需控制在±10%以內(nèi),以確保頻率穩(wěn)定性。例如,某晶振標(biāo)稱負(fù)載電容為30pF,實(shí)際容差需控制在±3pF以內(nèi),否則會(huì)導(dǎo)致頻率偏移超過允許范圍。

三、負(fù)載電容匹配的注意事項(xiàng)

1.避免過驅(qū)動(dòng)或欠驅(qū)動(dòng)

驅(qū)動(dòng)功率過大會(huì)導(dǎo)致晶振內(nèi)部電場(chǎng)過強(qiáng),引發(fā)壓電材料疲勞;過小則無法維持穩(wěn)定振蕩。例如,某晶振標(biāo)稱驅(qū)動(dòng)功率為100μW,實(shí)際驅(qū)動(dòng)功率需控制在80~120μW之間。

2.溫度補(bǔ)償設(shè)計(jì)

溫補(bǔ)晶振(TCXO)需在-40℃~85℃范圍內(nèi)保持頻率穩(wěn)定。例如,某工業(yè)級(jí)晶振通過內(nèi)置溫度傳感器與補(bǔ)償電路,將溫度對(duì)頻率的影響從±10ppm降至±1ppm。

3. EMI抑制措施

晶振輸出需通過濾波電路抑制高頻噪聲。例如,某5G模塊采用π型濾波器(L1=10nH,C1=100pF,C2=10pF),將輸出噪聲從-40dBm降至-60dBm。

結(jié)語(yǔ)

晶振負(fù)載電容匹配是電子系統(tǒng)穩(wěn)定性的基石。從理論推導(dǎo)到工程實(shí)踐,工程師需綜合考慮晶振參數(shù)、PCB布局及環(huán)境因素。未來,隨著智能化與小型化技術(shù)的發(fā)展,負(fù)載電容匹配將向更高效、更可靠的方向發(fā)展,為智能硬件提供堅(jiān)實(shí)的時(shí)鐘保障。

-

晶振

+關(guān)注

關(guān)注

35文章

3608瀏覽量

73681 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

508瀏覽量

30051 -

負(fù)載電容

+關(guān)注

關(guān)注

0文章

155瀏覽量

11166

發(fā)布評(píng)論請(qǐng)先 登錄

晶振的負(fù)載電容設(shè)計(jì)

晶振負(fù)載電容的重要性

晶振負(fù)載電容外匹配電容計(jì)算與晶振振蕩電路設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

晶振外匹配電容應(yīng)該怎樣選取

晶振的 “負(fù)載電容” 到底是什么

HCI杭晶電子-技術(shù)篇:晶振外掛負(fù)載電容與晶振負(fù)載關(guān)系

晶振負(fù)載電容匹配:從理論推導(dǎo)到工程實(shí)踐

晶振負(fù)載電容匹配:從理論推導(dǎo)到工程實(shí)踐

評(píng)論