在電子電路中,晶振是最常見的時鐘源之一。為了使晶振正常起振并穩定運行,必須根據其負載電容(Load Capacitance, 簡稱 CL)合理設計電路中的外掛負載電容。不恰當的電容匹配會導致晶振起振困難、頻率偏差增大,甚至系統不穩定。

本文將詳細解析晶振負載電容的含義、外掛電容的計算方法,以及電路設計中的實際注意事項。

一、什么是晶振的負載電容(CL)?

晶振廠商在數據手冊中通常會標出一個標稱負載電容值 CL,比如 18pF、20pF、12pF 等,這代表晶體在該電容負載下被調校以達到其標稱振蕩頻率。

??換句話說,只有在等效負載電容 = CL 的情況下,晶振才能輸出精確的頻率。

二、外掛電容如何影響負載電容?

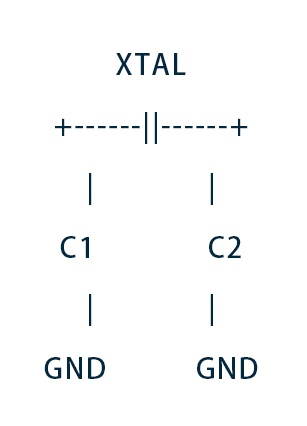

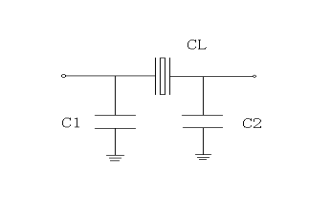

晶振電路常見如下形式:

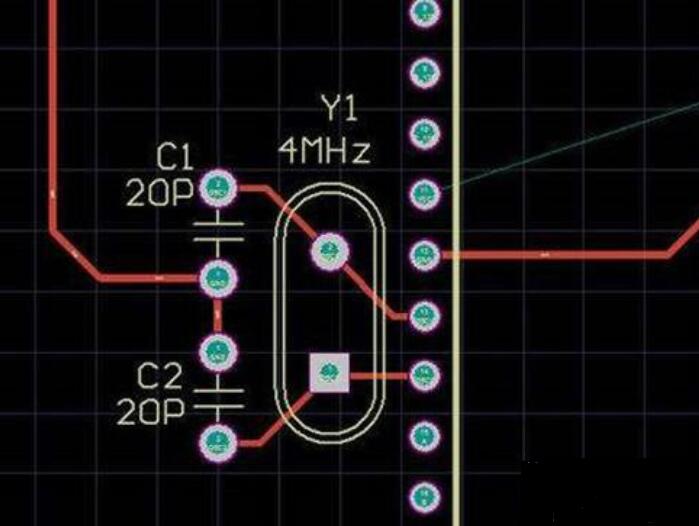

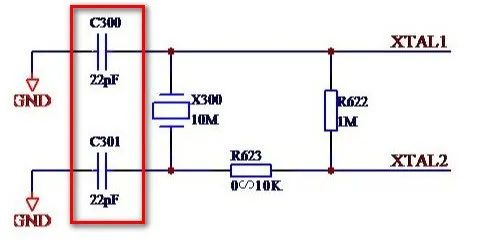

?C1 和 C2 是外掛到地的兩個電容(一般是貼片電容);

?XTAL 兩端分別接至晶振的兩個引腳;

?實際上,晶振的等效負載電容 CL 是由 C1 和 C2 通過串聯,再考慮 PCB 板和封裝引入的寄生電容 Cp得到的。

三、計算公式:如何根據 CL 推算外掛電容值?

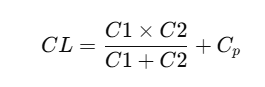

等效負載電容(CL)的公式如下:

其中:

?C1、C2:外接到地的電容;

?Cp:PCB 板上走線、封裝等引入的寄生電容(通常為 2pF ~ 5pF,可通過仿真或經驗估算);

?CL:晶振 datasheet 中給出的標稱負載電容。

【舉例說明】

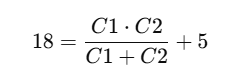

假設晶振規格為CL = 18pF,PCB 寄生電容 Cp ≈ 5pF,要反推合適的 C1 和 C2:

1.先代入公式:

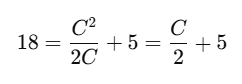

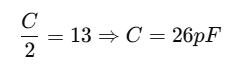

2.假設 C1 = C2 = C,公式簡化為:

3.解得:

?所以,推薦外掛電容 C1 = C2 =27pF(標準值)。

四、為什么外掛電容不匹配會引發問題?

1.頻率偏移:如果外掛電容過小或過大,會使晶振偏離其標稱頻率,造成系統時鐘偏差;

2.起振困難或不穩定:負載過重會降低增益,可能導致晶振無法起振或頻率抖動;

3.功耗增加:不合適的負載會導致晶振電路能量消耗增加;

4.EMI增加:振蕩不穩定時可能產生雜散頻率,影響系統電磁兼容性。

五、設計建議與工程實踐

1. 認真查看晶振 datasheet

?明確 CL 值;

?明確建議的電路拓撲;

?查是否推薦外掛電容值范圍。

2. 考慮實際板子環境

?使用 PCB 仿真或經驗估算 Cp;

?若使用高速或精密時鐘(如通信系統、MCU主頻>100MHz),建議做精確計算或測試。

3. 使用對稱電容

?一般建議 C1 = C2,使頻率居中、噪聲均衡;

?若有特殊匹配需求,也可不對稱設計。

4. 調試時可用貼片電容陣列

?可通過貼片電容(如10pF、15pF、22pF、27pF等)試配;

?利用頻譜儀或示波器檢查輸出穩定性和頻率準確性。

六、常見問題FAQ

| 問題 | 解答 |

| 若 CL=12pF,外掛電容該選多大? | 假設 Cp=5pF,則 C1=C2≈14pF |

| 為什么有些MCU不要外掛電容? | 有些晶振電路內部已集成負載電容(如STM32),無需外接 |

| 外掛電容不匹配會燒晶振嗎? | 通常不會燒壞,但可能起振失敗或頻率錯誤 |

結語

晶振的外掛負載電容設計是一個小而關鍵的細節,直接影響時鐘系統的穩定性與準確性。理解 CL 與 C1/C2 之間的計算關系,并根據實際 PCB 寄生電容調整參數,是實現穩定起振和精準頻率的關鍵。

在高速數字系統、通信設備或對時鐘要求極高的系統中,合理選擇和匹配晶振負載電容是一項必須認真對待的工程任務。

杭晶有專業的實驗室,有多名20年+的應用工程師,可以為客戶提供免費的專業匹配測試服務。如果您有這方面需求,請隨時與我們銷售或技術人員聯系。

-

晶振

+關注

關注

35文章

3599瀏覽量

73666 -

石英晶體

+關注

關注

0文章

194瀏覽量

39869 -

晶體振蕩器

+關注

關注

9文章

750瀏覽量

33362

發布評論請先 登錄

HCI杭晶電子-技術篇:晶振外掛負載電容與晶振負載關系

HCI杭晶電子-技術篇:晶振外掛負載電容與晶振負載關系

評論