Cypress CY14B108K/CY14B108M:8M位nvSRAM與實時時鐘的完美結合

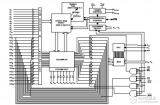

在電子設備的設計中,非易失性靜態隨機存取存儲器(nvSRAM)與實時時鐘(RTC)的組合常常是關鍵的一環。Cypress的CY14B108K和CY14B108M系列產品,將8M位的nvSRAM與功能完備的RTC集成于一體,為工程師們帶來了高性能、高可靠性的解決方案。今天,我們就來深入了解一下這兩款產品。

產品概述

CY14B108K和CY14B108M分別提供1024K×8(CY14B108K)和512K×16(CY14B108M)的存儲容量,具有25ns和45ns的快速訪問時間。其內部采用了QuantumTrap技術,實現了數據的非易失性存儲,同時具備無限次的讀寫和召回操作,以及高達100萬次的存儲操作,數據保留時間長達20年。此外,該系列產品還集成了功能豐富的RTC,包括看門狗定時器、可編程鬧鐘、電容或電池備份等功能,適用于工業溫度范圍。

功能特性

非易失性存儲

CY14B108K/CY14B108M采用了獨特的架構,將SRAM存儲單元與非易失性QuantumTrap單元配對在同一物理單元中。數據可以在SRAM和非易失性單元之間進行快速轉移,實現存儲(STORE)和召回(RECALL)操作。在存儲和召回操作期間,SRAM的讀寫操作將被禁止,以確保數據的完整性。

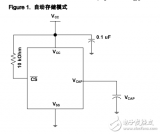

自動存儲(AutoStore)

AutoStore是QuantumTrap技術的一大特色,默認情況下該功能是啟用的。在正常工作時,設備會從VCC引腳獲取電流,為連接到VCAP引腳的電容充電。當VCC引腳的電壓下降到VSWITCH以下時,設備會自動斷開VCAP引腳與VCC的連接,并利用電容存儲的電荷進行一次存儲操作,將SRAM中的數據保存到非易失性單元中。需要注意的是,如果沒有連接電容到VCAP引腳,則必須使用軟件序列禁用AutoStore功能,否則可能會導致數據損壞。

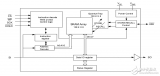

硬件存儲(HSB)

HSB引腳用于控制和確認存儲操作。當HSB引腳被拉低時,設備會在tDELAY時間后有條件地啟動存儲操作。只有在自上次存儲或召回周期以來發生過對SRAM的寫入操作時,才會真正開始存儲周期。在存儲操作進行期間,HSB引腳會被拉低,表示設備處于忙碌狀態。

軟件存儲和召回

通過特定的軟件地址序列,可以實現數據從SRAM到非易失性存儲器的存儲操作,以及從非易失性存儲器到SRAM的召回操作。具體來說,需要按照特定的順序從六個特定地址位置執行CE或OE控制的讀周期,以啟動存儲或召回周期。

實時時鐘(RTC)

CY14B108K/CY14B108M的RTC功能提供了精確的時鐘,支持閏年跟蹤和可編程的高精度振蕩器。時鐘和鬧鐘寄存器以BCD格式存儲數據,內部采用雙緩沖機制,防止在讀寫操作期間訪問過渡性的內部時鐘數據。此外,RTC還具備看門狗定時器、鬧鐘功能、電源監控和中斷功能等。

電氣特性

工作范圍

該系列產品適用于工業溫度范圍(-40°C至+85°C),工作電壓范圍為2.7V至3.6V。

直流電氣特性

在不同的工作條件下,產品的直流電氣特性表現良好。例如,平均VCC電流在不同的訪問時間和工作模式下有所不同,待機電流較低,輸入和輸出的泄漏電流也在合理范圍內。

交流電氣特性

交流電氣特性方面,產品具有快速的讀寫周期時間、地址訪問時間和輸出使能到數據有效時間等。同時,在不同的操作模式下,也有相應的切換波形和時間參數。

PCB設計注意事項

由于RTC晶體振蕩器是一個低電流、高阻抗的電路,其晶體引腳對電路板上的噪聲非常敏感。因此,在PCB設計時,需要注意以下幾點:

- 晶體布局:將晶體盡可能靠近Xin和Xout引腳放置,保持晶體與RTC之間的走線長度相等且盡可能短,以減少噪聲耦合的可能性。

- 走線寬度:Xin和Xout走線寬度應小于8mil,以減小走線電容。

- 屏蔽保護:為晶體電路提供一個保護環,防止相鄰信號的噪聲耦合。

- 信號隔離:在RTC走線附近布線時,要注意與其他高速信號保持至少200mil的距離,避免噪聲干擾。

- 銅平面設計:在相鄰的PCB層創建一個隔離的實心銅平面,位于晶體電路下方,以防止來自其他信號層的噪聲耦合。

總結

Cypress的CY14B108K/CY14B108M系列產品為電子工程師們提供了一個高性能、高可靠性的nvSRAM與RTC解決方案。其豐富的功能特性、良好的電氣特性和詳細的設計指導,使得該系列產品在工業控制、數據記錄、儀器儀表等領域具有廣泛的應用前景。不過,在使用過程中,也需要注意AutoStore Disable功能存在的問題,避免數據損壞。希望通過本文的介紹,能幫助工程師們更好地了解和應用這兩款產品。

大家在實際設計中有沒有遇到過類似產品的使用問題呢?歡迎在評論區分享你的經驗和見解。

-

Cypress

+關注

關注

11文章

139瀏覽量

84854 -

RTC

+關注

關注

2文章

653瀏覽量

71797 -

nvSRAM

+關注

關注

0文章

19瀏覽量

18753

發布評論請先 登錄

CY14B116M更改為CY14B108 M可以嗎? 這兩款芯片有何不同?我如何使用CY14B116M?

CY14E256LA和CY14B101LA零件的模具是否有任何差異?

CY14B256LA非易失性存儲問題

無法寫入CY14B108K的最后2個區塊

CY7B923用作ECL時鐘源

連接CY7B923和CY7B933(HOTlink器件)至定

連接CY7B923和CY7B933(HOTlink器件)至寬

如何用Cypress的CY7B923 CY7B933替換Am

在CY37032 CPLD中,用CY7B933 HOTLin

SRAM 8 Mbit (1024K x 8/512K x 16) nvSRAM帶實時時鐘

SRAM CY14B101Q1, CY14B101Q2, CY14B101Q3 1 Mbit (128 K × 8) Serial SPI nvSRAM

SRAM 1-Mbit (128 K × 8) 串行 SPI nvSRAM,帶實時時鐘

Cypress CY14B108K/CY14B108M:8M位nvSRAM與實時時鐘的完美結合

Cypress CY14B108K/CY14B108M:8M位nvSRAM與實時時鐘的完美結合

評論