在芯片制造過程中,可能會引入物理缺陷,這些缺陷在電氣層面的表現稱為故障。常見的故障模型包括固定型故障(例如引腳固定連接到電源或地)、跳變故障、路徑延時故障(如門級端口信號上升下降過慢)、以及靜態電流型故障(表現為異常高電流泄漏)。若某個故障能在電路中向后傳播并導致芯片輸出與預期不符,則稱為失效。值得注意的是,并非所有故障都會引發失效,只有那些最終影響到功能正確性的故障才會導致實際問題。

掃描測試Scan是可測性設計(DFT)中廣泛使用的一種方法,其核心是在電路中使用帶Scan功能的寄存器,并將它們連接成一條或多條掃描鏈。

簡單說Scan 就是給芯片加一套 “測試專用通路”,讓芯片內部變得可測、可控、可量產篩片,是現代芯片必做的 DFT 技術。

Scan基本原理

Scan 寄存器:

帶Scan功能的寄存器,如下圖多了SI/SE兩個Pin:

SI是Scan in,是Scan鏈的輸入端;

SE - Scan Enable,Scan使能;

另外Q,在Scan mode下復用為SO,Scan Out Pin

考慮一個只有三個寄存器和一個與門的“芯片”,邏輯功能如下圖:

Scan鏈/掃描鏈:

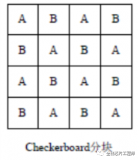

Scan串鏈后,如下圖,可以看到三個寄存器通過SI/SO穿成 了一條鏈,也叫掃描鏈:

把寄存器拉平,就變成了下圖,看著更有“鏈”的感覺:

Scan測試:

Scan有兩種測試模式,Shift和Capture模式;

通過Scan鏈從SI端口,以較低頻率的測試時鐘將測試向量逐位移入內部寄存器,并從SO Pin移出來, 并比較輸出的數據是否符合預期:

/* Scan模式下,Clk會切換到頻率較低的Scan CLK*/

通過Scan鏈的shift測試,可以覆蓋寄存器的基本功能;

那還有組合邏輯的測試,怎么覆蓋呢?通過Shift + Capture組合來測試,如下圖分三步測試;

1. 通過shift模式,給三個寄存器移入1,1,0的值;

2. 啟動Capture模式,即:關閉寄存器的SE,給一個cycle的時鐘,這樣寄存器可以Capture到組合邏輯的輸出結果;

3. 再通過Shift模式,將寄存器的結果輸出,和預期結果比對,即可判斷電路是否有誤

上圖的例子,我們假設圖中A點生產過程中被Tie 0了,那最終SO輸出的結果就是110,而不是預期的111,這樣就可以檢測到生產中的錯誤了。

當然,實際芯片的邏輯是相當復雜的,組合邏輯錐也非常復雜,還會現在有自動化工具,可以自動生成測試pattern,并分析測試覆蓋率,覆蓋覆蓋率不達標,也可以通過一些手段增加覆蓋率,比如組合邏輯錐太復雜導致測試困難時,可以通過增加旁路寄存器作用DFT的觀測點;另外現在芯片寄存器數量也非常龐大,通常一顆芯片寄存器會串成多條寄存器鏈,來縮短測試時間;

Scan基本作用

DFT Scan測試主要用來做芯片制造過程引入的缺陷(如金屬短路、斷路、孔缺失、晶體管異常等),是芯片量產檢測、定位缺陷、保障良率的核心手段,核心作用如下:

?解決芯片內部難觀測、難控制問題

?把芯片內部寄存器串成掃描鏈(Scan Chain),讓外部測試儀能像 “讀 / 寫移位寄存器” 一樣,可控、可觀測芯片內部幾乎所有節點

?實現高效、基本全覆蓋的邏輯測試,能夠覆蓋幾乎所有組合邏輯 + 時序電路(檢fault率,可以達到99.999%)

?支撐量產自動化測試(ATE)

?提供標準、可自動化的測試方式,芯片出廠前快速篩出壞片,保證交付質量。

?測試失敗時可定位故障位置,幫助工藝 / 設計端分析失效原因,持續改善良率。

/*聲明:本文中電路圖和時序圖僅為說明基本原理,未經嚴謹的審核和測試,僅供參考 */

-

芯片

+關注

關注

463文章

54267瀏覽量

468287 -

測試

+關注

關注

9文章

6317瀏覽量

131578 -

DFT

+關注

關注

2文章

237瀏覽量

24093

發布評論請先 登錄

芯片測試覆蓋率99%就夠了嗎?給DFT設計提個醒

讓你徹底理解DFT

幫你理解DFT中的scan technology

Nvidia is hiring-Senior DFT Engineer

什么是DFT,DFT是什么意思

一文讀懂DC/AC SCAN測試技術

DFT分步法原理分析

SoC芯片設計中的可測試性設計(DFT)

芯片設計測試中scan和bist的區別

DFT如何產生PLL 測試pattern

芯片DFT Scan測試原理

芯片DFT Scan測試原理

評論