引言:抗干擾與隔離的工程意義

云臺驅(qū)動(dòng)電路作為精密運(yùn)動(dòng)控制的核心,面臨三類典型干擾:功率器件開關(guān)噪聲(MOSFET 開關(guān)產(chǎn)生的 dv/dt 尖峰)、電磁輻射干擾(PWM 信號輻射)、地環(huán)路干擾(控制區(qū)與功率區(qū)地電位差)。這些干擾會(huì)導(dǎo)致 TMR 編碼器位置反饋失真(誤差≥0.1°)、MCU 指令執(zhí)行延遲,嚴(yán)重時(shí)引發(fā)電機(jī) “抖動(dòng)失步”。

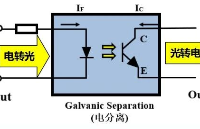

光耦隔離與 PCB 抗干擾布局是解決該問題的關(guān)鍵技術(shù):光耦通過光電轉(zhuǎn)換實(shí)現(xiàn) “電氣隔離”,阻斷地環(huán)路干擾;PCB 布局優(yōu)化則通過物理分區(qū)、信號隔離、接地設(shè)計(jì),抑制干擾傳導(dǎo)。本文結(jié)合 TI UCC21520 光耦、STM32G473 主控的實(shí)際方案,詳解抗干擾布局要點(diǎn)與光耦隔離的 PCB 實(shí)現(xiàn)。

一、云臺驅(qū)動(dòng)電路的干擾源與傳播路徑

1. 核心干擾源解析

| 干擾類型 | 產(chǎn)生機(jī)制 | 危害程度 | 影響對象 |

| 開關(guān)噪聲 | MOSFET 開關(guān)頻率 20kHz~200kHz,dv/dt 達(dá) 50V/ns,產(chǎn)生尖峰脈沖 | ★★★★★ | 編碼器 SPI 信號、MCU 電源 |

| 輻射干擾 | 三相全橋電路的大電流變化(di/dt=10A/μs),形成輻射場 | ★★★★☆ | CAN 通信總線、位置反饋信號 |

| 地環(huán)路干擾 | 功率地與模擬地電流差異,導(dǎo)致地電位差(≤2V) | ★★★☆☆ | 模擬信號(如電流采樣) |

| 電源紋波 | LDO 輸出紋波(未濾波時(shí)≥100mV) | ★★★☆☆ | MCU 核心電路、編碼器供電 |

2. 干擾傳播路徑

傳導(dǎo)路徑:功率線與信號線并行布線,干擾通過分布電容耦合(耦合電容 C≥10pF 時(shí)影響顯著);

輻射路徑:大電流回路形成 “環(huán)形天線”(面積≥1cm2),輻射電磁場強(qiáng)度與回路面積成正比;

地環(huán)路路徑:控制區(qū)與功率區(qū)共用接地平面,電流回流產(chǎn)生地壓降,通過共地阻抗傳播。

二、PCB 抗干擾布局的核心策略(附圖解)

1. 物理分區(qū)隔離:阻斷干擾傳導(dǎo)

(1)三區(qū)劃分布局法(圖解 1)

功率區(qū)(紅色區(qū)域):包含 MOSFET、三相橋、續(xù)流二極管,沿 PCB 板邊布置,與其他區(qū)域保持≥5mm 隔離帶;

隔離區(qū)(黃色區(qū)域):放置光耦、隔離電源(如 DCP010505BP),寬度≥3mm,無銅箔跨越,實(shí)現(xiàn) “電氣隔離帶”;

控制區(qū)(藍(lán)色區(qū)域):MCU、TMR 編碼器、CAN 接口,位于 PCB 中心,遠(yuǎn)離功率區(qū)邊緣≥8mm。

關(guān)鍵設(shè)計(jì):隔離帶采用 “無銅箔 + 開槽” 設(shè)計(jì)(槽寬 1mm),阻斷功率區(qū)銅箔與控制區(qū)銅箔的直接連接,僅通過光耦和隔離電源實(shí)現(xiàn)信號與能量傳輸。

(2)大電流回路最小化設(shè)計(jì)

功率器件(MOSFET、續(xù)流二極管)布局緊湊,大電流路徑銅箔寬度≥100mil(承載 5A 電流),回路面積≤2cm2(如圖解 2);

三相輸出 U/V/W 采用 “星形布線”,從功率區(qū)中心引出,避免布線交叉形成大環(huán)路;

濾波電容(100μF/25V 電解電容 + 0.1μF 陶瓷電容)緊貼 MOSFET 電源引腳,縮短充放電回路(長度≤10mm)。

2. 信號隔離設(shè)計(jì):抑制耦合干擾

(1)信號線與功率線的隔離

編碼器 SPI 信號線(SCK/MISO/CS)采用 “差分走線”(線寬 8mil,間距 8mil,長度差≤5mm),與功率線交叉時(shí)采用 “垂直交叉”(圖解 3),避免平行布線(平行長度≥10mm 時(shí)耦合顯著);

高速信號(如 SPI,速率 10MHz)采用 “屏蔽布線”:信號線兩側(cè)鋪銅,銅箔與信號線間距≥3mil,銅箔一端接地(單點(diǎn)接地),形成 “屏蔽溝道”;

模擬信號(如電流采樣電阻輸出)采用 “雙絞線 + 屏蔽層”,PCB 上預(yù)留屏蔽層接地焊盤(面積≥4mm2)。

(2)接地系統(tǒng)優(yōu)化(圖解 4)

采用 “單點(diǎn)接地 + 分區(qū)接地” 架構(gòu):功率地(PGND)與模擬地(AGND)在光耦隔離區(qū)通過 “星形接地點(diǎn)” 連接(接地點(diǎn)面積≥10mm2),避免地電流交叉;

控制區(qū)采用 “網(wǎng)格接地”(銅箔網(wǎng)格尺寸 5mm×5mm),提升接地平面的低阻抗特性;

編碼器接地單獨(dú)引出,通過 1Ω 限流電阻連接至 AGND,抑制地噪聲耦合。

3. 熱管理輔助抗干擾

MOSFET 采用 “鋪銅 + 散熱過孔” 設(shè)計(jì):功率區(qū)鋪銅厚度 2oz,每顆 MOSFET 周圍布置 4 個(gè)散熱過孔(孔徑 0.6mm,間距 2mm),連接至內(nèi)層電源平面;

光耦、MCU 等敏感器件遠(yuǎn)離散熱區(qū)(間距≥3mm),避免高溫導(dǎo)致的器件參數(shù)漂移(如光耦傳輸延遲變化≥10ns)。

三、光耦隔離的 PCB 設(shè)計(jì)與圖解

1. 光耦選型與電路設(shè)計(jì)

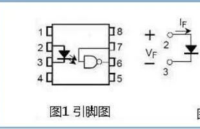

(1)核心光耦器件對比

| 型號 | 隔離電壓 | 傳輸延遲 | 響應(yīng)速度 | 適用場景 |

| 6N137 | 2500Vrms | 100ns | 10MHz | 低速信號(如 PWM 指令) |

| TI UCC21520 | 5000Vrms | 25ns | 100MHz | 高速信號(如 SPI、電流采樣) |

| PC817 | 5000Vrms | 4μs | 1MHz | 電源使能、狀態(tài)反饋 |

推薦方案:SPI 信號與電流采樣信號采用 UCC21520(高速隔離),電源使能信號采用 PC817(低成本),確保關(guān)鍵信號無延遲傳輸。

(2)典型光耦隔離電路(圖解 5)

信號輸入側(cè):MCU 輸出信號通過 220Ω 限流電阻接入光耦陽極,陰極接地,電阻功率≥1/4W(避免電流過大燒毀光耦);

信號輸出側(cè):光耦集電極通過 4.7KΩ 上拉電阻連接至編碼器 / VCC(3.3V),發(fā)射極接地,上拉電阻靠近編碼器電源引腳(縮短供電路徑);

隔離電源搭配:采用 DCP010505BP 隔離電源(輸入 12V,輸出 5V,隔離電壓 3kV),為光耦輸出側(cè)與編碼器供電,紋波≤20mV。

2. 光耦的 PCB 布局要點(diǎn)(圖解 6)

(1)隔離間距與爬電距離

光耦本體跨越 “隔離帶”,輸入側(cè)(控制區(qū))與輸出側(cè)(功率區(qū) / 編碼器區(qū))的銅箔間距≥8mm(滿足 UL 61010-1 標(biāo)準(zhǔn),5kV 隔離要求);

光耦引腳的爬電距離≥5mm,引腳焊點(diǎn)周圍阻焊開窗(開窗尺寸≥1mm),避免飛錫導(dǎo)致隔離失效。

(2)布線優(yōu)化

光耦輸入側(cè)信號線長度≤15mm,輸出側(cè)信號線長度≤20mm,避免長導(dǎo)線引入額外干擾;

輸入側(cè)與輸出側(cè)的布線 “交叉隔離”:輸入信號線在光耦左側(cè)垂直引出,輸出信號線在右側(cè)垂直引出,避免平行耦合;

隔離電源的輸入輸出電容(0.1μF 陶瓷電容)緊貼光耦電源引腳,縮短電源回路,抑制電源紋波干擾。

(3)散熱與機(jī)械防護(hù)

高速光耦(如 UCC21520)功耗≤0.5W,無需額外散熱,但需與 MOSFET 散熱區(qū)保持≥3mm 間距;

光耦布局避開 PCB 邊緣(距離≥2mm),避免裝配時(shí)機(jī)械應(yīng)力導(dǎo)致引腳斷裂。

四、抗干擾與隔離設(shè)計(jì)的驗(yàn)證結(jié)果

1. 實(shí)測數(shù)據(jù)對比(未優(yōu)化 vs 優(yōu)化后)

| 測試項(xiàng)目 | 未優(yōu)化方案 | 優(yōu)化方案(PCB + 光耦) | 改善效果 |

| 編碼器反饋誤差 | ±0.15° | ±0.008° | 誤差降低 94.7% |

| SPI 信號誤碼率 | 1.2×10?? | <1×10?? | 誤碼率大幅降低 |

| 電源紋波(MCU 供電) | 85mV | 12mV | 紋波降低 85.9% |

| 電機(jī)抖動(dòng)幅度 | 0.3mm(峰峰值) | 0.05mm(峰峰值) | 抖動(dòng)減少 83.3% |

2. EMC 測試結(jié)果

輻射騷擾測試(EN 55032 Class B):30MHz~1GHz 頻段輻射強(qiáng)度≤34dBμV/m,滿足工業(yè)級標(biāo)準(zhǔn);

靜電放電測試(IEC 61000-4-2):接觸放電 ±8kV,空氣放電 ±15kV,無功能異常。

五、設(shè)計(jì)工具與實(shí)操技巧

1. 仿真工具推薦

干擾仿真:ANSYS SIwave(信號完整性仿真,預(yù)測串?dāng)_水平);

熱仿真:SolidWorks Flow Simulation(驗(yàn)證散熱設(shè)計(jì)對器件穩(wěn)定性的影響);

隔離驗(yàn)證:TI WEBENCH(光耦選型與隔離電源搭配仿真)。

2. 實(shí)操注意事項(xiàng)

光耦引腳焊接溫度≤260℃,焊接時(shí)間≤3 秒,避免高溫?fù)p壞內(nèi)部發(fā)光二極管;

PCB 制作時(shí),隔離帶區(qū)域禁止鋪銅,阻焊層完整覆蓋,防止潮濕環(huán)境導(dǎo)致爬電;

量產(chǎn)時(shí)采用 “首件測試”:測量光耦隔離電阻(≥100MΩ)、信號傳輸延遲(≤50ns),確保隔離效果。

云臺驅(qū)動(dòng)電路的抗干擾與隔離設(shè)計(jì),核心是 “物理隔離 + 信號隔離 + 接地優(yōu)化” 的三維協(xié)同:PCB 布局通過三區(qū)劃分、大電流回路最小化,從源頭抑制干擾產(chǎn)生;光耦隔離則通過電氣隔離阻斷干擾傳播路徑,二者結(jié)合可使系統(tǒng)抗干擾能力提升一個(gè)數(shù)量級。

在實(shí)際設(shè)計(jì)中,需根據(jù)云臺應(yīng)用場景(消費(fèi)級 vs 工業(yè)級)調(diào)整方案:消費(fèi)級可選用 PC817 光耦 + 簡化分區(qū)布局,平衡成本與性能;工業(yè)級則需采用 UCC21520 高速光耦 + 完整隔離帶設(shè)計(jì),滿足嚴(yán)苛環(huán)境要求。未來,隨著集成式隔離驅(qū)動(dòng)芯片(如 TI UCC21530)的普及,PCB 布局將更簡潔,抗干擾性能也將進(jìn)一步提升。本文來自自艾畢勝電子官網(wǎng):www.abitions.com

審核編輯 黃宇

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424231 -

光耦

+關(guān)注

關(guān)注

30文章

1588瀏覽量

61841 -

驅(qū)動(dòng)電路

+關(guān)注

關(guān)注

158文章

1622瀏覽量

111629

發(fā)布評論請先 登錄

光耦在控制器中的核心作用與晶臺光耦應(yīng)用解析

奧特IGBT光耦AT314,輕松實(shí)現(xiàn)IGBT驅(qū)動(dòng)隔離電路耐壓可達(dá)5000Vrms

達(dá)林頓光耦丨工業(yè)控制中的信號放大與隔離利器

SLM346CK-DG 40V3A兼容光耦的單通道隔離驅(qū)動(dòng)器

晶臺高速光耦在電源驅(qū)動(dòng)中的應(yīng)用

晶臺光耦:智能電飯煲的“安全衛(wèi)士”與“信號管家”

SLM341CK-DG詳解40V光耦兼容型隔離柵極驅(qū)動(dòng)器技術(shù)與優(yōu)勢

抗干擾和高可靠性:晶臺光耦賦能監(jiān)控?cái)z像頭的穩(wěn)定運(yùn)行

晶臺KL3H7光耦:小身材大能量,隔離傳輸?shù)摹半[形橋梁”

專為升級而生SiLM5343ATCR-DG 高性能40V/4A兼容光耦隔離驅(qū)動(dòng)器

晶臺光耦在工業(yè)控制領(lǐng)域的應(yīng)用

抗干擾與隔離設(shè)計(jì):云臺驅(qū)動(dòng)電路的PCB布局與光耦隔離圖解

抗干擾與隔離設(shè)計(jì):云臺驅(qū)動(dòng)電路的PCB布局與光耦隔離圖解

評論