TPS7N59:高性能低噪聲LDO穩壓器的設計與應用

在電子設備的電源管理領域,低壓差線性穩壓器(LDO)扮演著至關重要的角色。今天,我們就來深入探討一款名為TPS7N59的10A、低輸入電壓、低噪聲、高精度、超低壓差LDO穩壓器。

文件下載:tps7n59.pdf

1. 關鍵特性解讀

1.1 電氣性能卓越

- 寬輸入電壓范圍:TPS7N59的輸入電壓范圍為0.7V至6.0V,這使得它能夠適應多種不同的電源環境,為設計帶來了極大的靈活性。

- 低輸出電壓噪聲:輸出電壓噪聲僅為2.5μVRMS,如此低的噪聲水平對于對噪聲敏感的應用(如RF放大器、雷達傳感器等)來說至關重要,能夠有效保證信號的純凈度。

- 高精度輸出:在負載、線路和溫度變化的情況下,仍能保持1%(最大)的高精度輸出,確保了電源的穩定性和可靠性。

- 低壓差特性:在10A輸出電流時,典型壓差僅為150mV,這意味著在輸入輸出電壓差較小時,也能正常工作,減少了功率損耗,提高了效率。

- 高電源抑制比(PSRR):在不同頻率下都表現出了優異的PSRR性能,如在1kHz時為 - 84dB,10kHz時為 - 64dB,100kHz時為 - 49dB,1MHz時為 - 30dB,能夠有效抑制電源中的紋波和噪聲。

1.2 其他特性亮點

- 出色的負載瞬態響應:在10mA至10A的負載階躍變化時,輸出電壓變化僅為±20mV,能夠快速響應負載的變化,保證輸出電壓的穩定。

- 可調輸出電壓范圍:輸出電壓可在0.5V至5.2V之間進行調節,滿足了不同負載對電壓的需求。

- 可調軟啟動浪涌控制:通過調節軟啟動時間,可以有效減少啟動時的浪涌電流,保護電路和負載。

- BIAS軌設計:BIAS軌可連接3V至12V的外部電源,為電路提供了額外的靈活性。

- 開漏電源良好(PG)輸出:方便監測穩壓器的輸出狀態,確保系統的正常運行。

- 緊湊封裝:采用4mm × 4mm、24引腳的WQFN封裝,節省了電路板空間,適合小型化設計。

2. 應用領域廣泛

TPS7N59憑借其卓越的性能,在多個領域都有廣泛的應用,包括但不限于:

- 硬件加速器與GPU卡/模塊:為這些高性能設備提供穩定、低噪聲的電源,確保其正常運行。

- 光通信與銅纜CPE:滿足對電源精度和噪聲要求較高的通信設備需求。

- 高性能計算:為服務器、工作站等設備提供可靠的電源支持。

- 超聲掃描儀:在醫療設備中,低噪聲的電源對于保證圖像質量至關重要。

- 實驗室和現場儀器:為高精度儀器提供穩定的電源,確保測量結果的準確性。

- 傳感器、成像和雷達:滿足這些對噪聲敏感的應用對電源的嚴格要求。

3. 詳細技術分析

3.1 功能概述

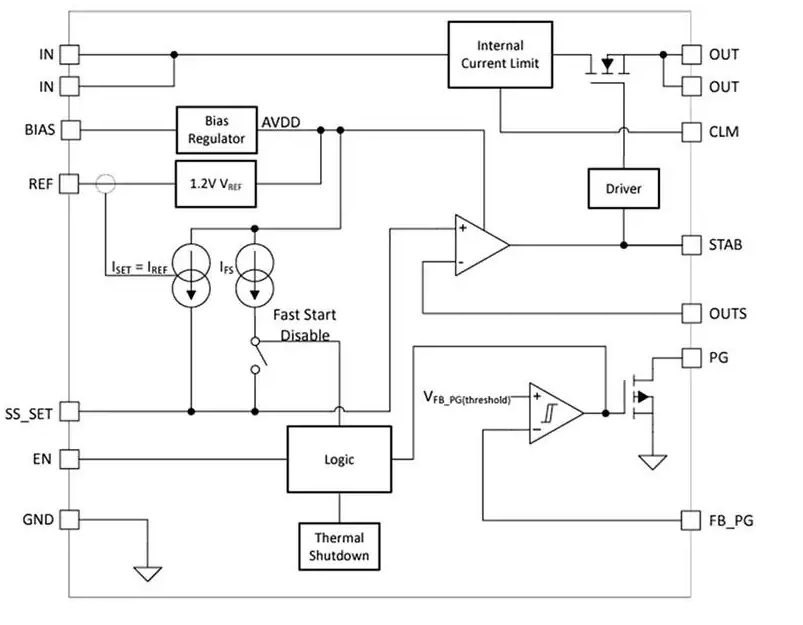

TPS7N59主要由電流參考和單位增益LDO緩沖器兩個主要部分組成,同時還具備一些輔助功能,如可調軟啟動浪涌控制、精密使能和PG引腳等。

- 電流參考:由REF引腳控制,通過一個外部電阻設置輸出電壓,同時還能設置啟動時間和過濾參考電壓產生的噪聲。

- 單位增益LDO緩沖器:采用單位增益配置,確保輸出電壓的穩定性和低噪聲特性。SNS引腳僅用于遠程感測負載。

3.2 功能框圖與工作原理

通過功能框圖可以清晰地看到,TPS7N59內部包含了多個關鍵模塊,如UVLO、電流限制、熱關斷等,這些模塊協同工作,確保了穩壓器的安全可靠運行。

3.3 特性詳細描述

- 輸出電壓設置與調節:通過內部的低噪聲電流參考和外部電阻(RREF)來設置輸出電壓,公式為VOUT = IREF × RREF。同時,通過在RREF上并聯一個外部電容(CREF),可以有效衰減帶隙噪聲,實現低噪聲輸出。

- 低噪聲、超高電源抑制比(PSRR):采用高精度、低噪聲的電流參考和先進的CMOS誤差放大器,在整個輸出電壓范圍內都能保持低噪聲特性,并且提供了寬頻帶的PSRR。

- 可編程軟啟動:通過控制CREF電容,可以實現對啟動時浪涌電流的有效控制,同時還能縮短某些應用的啟動時間。

- 精密使能和UVLO:該穩壓器具有三個獨立的欠壓鎖定(UVLO)電壓,分別用于輸入電源、偏置電源和用戶可編程的使能引腳,確保在電壓不足時及時關閉輸出,保護設備安全。

- 電源良好(PG)引腳:通過比較SNS引腳電壓和內部參考電壓,來指示LDO是否準備好提供電源,方便系統進行監測和控制。

- 主動放電:在設備禁用時,通過內部的下拉MOSFET對輸出電容和REF電容進行主動放電,確保快速放電。

- 熱關斷保護:當晶體管結溫超過設定值時,熱關斷保護電路會自動關閉LDO,當溫度下降到一定程度后,再重新開啟,保證了設備的安全性。

3.4 設備功能模式

- 正常運行模式:當輸入電壓大于標稱輸出電壓加上壓差、偏置電壓大于標稱輸出電壓加上3.2V、輸出電流小于電流限制、結溫小于熱關斷溫度且使能引腳電壓超過閾值時,設備進入正常運行模式。

- 壓差運行模式:當輸入電壓低于標稱輸出電壓加上指定壓差,但其他條件滿足正常運行要求時,設備進入壓差運行模式,此時輸出電壓會跟蹤輸入電壓減去壓差。

- 禁用模式:當輸入電壓低于UVLO閾值、偏置電壓低于BIAS(UVLO)閾值或使能引腳電壓低于閾值時,設備進入禁用模式。

- 電流限制模式:當輸出電流大于或等于最小電流限制時,設備進入電流限制模式,采用折返式電流限制保護。

4. 應用與實現要點

4.1 精密使能(外部UVLO)

通過使用電阻分壓器,可以設置外部欠壓鎖定(UVLO)電壓,防止設備在輸入電源電壓不足時啟動,同時還能實現多個電源的簡單排序。在設計時,需要根據公式計算正確的電阻值。

4.2 欠壓鎖定(UVLO)操作

TPS7N59在輸入和偏置電壓上都采用了欠壓鎖定(UVLO)電路,確保在所有電壓都大于上升UVLO電壓時才啟用輸出。在實際應用中,需要注意向下的線路瞬態可能會觸發UVLO,但由于能量不足可能導致內部電路不完全放電的問題。

4.3 壓差電壓(VDO)

壓差電壓是指輸入輸出電壓之間的最小差值,當輸入電壓下降到或低于設定的壓差時,設備將無法正常調節輸出電壓。為了保證設備的性能,需要保持足夠的工作裕量。

4.4 輸入和輸出電容要求

為了確保設備的穩定性和性能,建議在輸出端使用22μF或更大的陶瓷電容(實際電容值15μF或更大),在輸入端使用10μF或更大的陶瓷電容(實際電容值5μF或更大)。同時,要盡量減小輸入和輸出電容的ESR和ESL,以避免負載行為對電源的影響。

4.5 推薦電容類型

推薦使用低ESR和低ESL的陶瓷電容,如X7R、X5R和COG額定的陶瓷電容,這些電容在溫度和電源電壓變化時具有較好的電容穩定性。不建議使用Y5V額定的電容,因為其電容值變化較大。

4.6 軟啟動、噪聲降低(NR/SS引腳)和電源良好(PG引腳)

NR/SS引腳具有控制軟啟動時間和降低噪聲的雙重功能。通過控制CNR/SS電容,可以實現對軟啟動時間的調節,同時降低輸出電壓噪聲。在設計時,需要注意NR/SS和REF引腳的泄漏會直接影響參考電壓的精度。

4.7 優化噪聲和PSRR

通過合理選擇CNR/SS和COUT電容以及增加工作裕量,可以有效優化設備的固有噪聲和PSRR性能。在低頻范圍內,CNR/SS電容對噪聲的抑制作用更為明顯;在高頻范圍內,COUT電容則更為重要。

4.8 可調操作

通過一個外部電阻(RREF)可以方便地設置輸出電壓,根據公式計算所需的電阻值。同時,文檔中還提供了不同輸出電壓對應的推薦RREF電阻值。

4.9 負載瞬態響應

負載瞬態響應是指LDO對負載電流變化的響應能力。在負載從輕到重或從重到輕變化時,輸出電壓會出現相應的波動,通過合理選擇輸出電容和直流負載,可以減小這些波動。

4.10 排序

IN、BIAS和EN之間沒有排序要求,但在關機時,如果BIAS軌放電速度比IN軌快,可能會觸發錯誤的PG信號。

4.11 電源良好功能

PG引腳通過比較SNS引腳電壓和內部參考電壓來指示LDO的輸出狀態。在設計時,需要注意設置合適的上拉電阻,并避免出現錯誤的PG事件。

4.12 電流模式裕量調節

通過使用電流DAC,可以實現對輸出電壓的裕量調節,以評估電路對電源變化的容忍度。在實際應用中,需要根據設計要求選擇合適的DAC和電阻值。

4.13 電壓模式裕量調節

與電流模式裕量調節類似,電壓模式裕量調節通過使用電壓DAC來實現。同樣需要根據設計要求選擇合適的DAC和電阻值。

4.14 功率耗散

功率耗散是影響穩壓器性能和可靠性的重要因素,通過合理選擇系統電壓軌和優化熱設計,可以有效降低功率耗散,提高效率。

4.15 估算結溫

使用psi(Ψ)熱指標可以估算設備在實際應用中的結溫,這些指標與PCB的設計和銅面積有關。

4.16 TPS7N59EVM - 184熱分析

通過對TPS7N59EVM - 184的熱分析,可以了解設備在不同功率耗散下的溫度分布情況,為熱設計提供參考。

5. 典型應用案例

5.1 設計要求

以一個具體的設計為例,該應用要求輸入電壓為1.2V(±3%),偏置電壓為5V或12V,輸出電壓為0.75V(1%精度),輸出電流為10A(最大)、8A(最小),噪聲小于5μVRMS,最大負載瞬態為 - 10mV(100mA至10A),啟動時間小于15ms。

5.2 詳細設計步驟

在設計過程中,使用典型的10μF和22μF輸入和輸出電容以及4.7μF的NR/SS電容,以實現快速啟動時間、良好的噪聲和PSRR性能以及負載瞬態響應。通過計算選擇合適的RREF電阻值來設置輸出電壓,同時將PG引腳連接到地以幫助散熱。

5.3 應用曲線分析

通過對負載瞬態、噪聲和PSRR等應用曲線的分析,可以驗證設計是否滿足要求,確保設備的性能穩定可靠。

6. 電源供應與布局建議

6.1 電源供應建議

確保輸入電壓范圍為0.7V至6.0V,BIAS軌最高為12.6V,并且輸入電源應具有良好的調節性能和低阻抗。如果輸入電源存在噪聲,可以使用低ESR的額外輸入電容并增加工作裕量來改善輸出噪聲、PSRR和負載瞬態性能。

6.2 布局指南

為了獲得最佳性能,建議將所有電路組件放置在電路板的同一側,并盡可能靠近LDO引腳連接。同時,要確保輸入和輸出電容的接地返回連接盡可能靠近,以減小電感寄生效應,提高電路穩定性。

總結

TPS7N59作為一款高性能的LDO穩壓器,具有低噪聲、高精度、超低壓差等諸多優點,適用于多種對電源要求較高的應用場景。在設計過程中,需要充分考慮其各項特性和應用要點,合理選擇組件和進行布局,以確保設備的性能和可靠性。希望本文能夠對電子工程師在使用TPS7N59進行設計時提供一些有益的參考。大家在實際應用中遇到過哪些問題呢?歡迎在評論區留言討論。

-

電源管理

+關注

關注

117文章

7176瀏覽量

147998 -

LDO穩壓器

+關注

關注

0文章

183瀏覽量

17824

發布評論請先 登錄

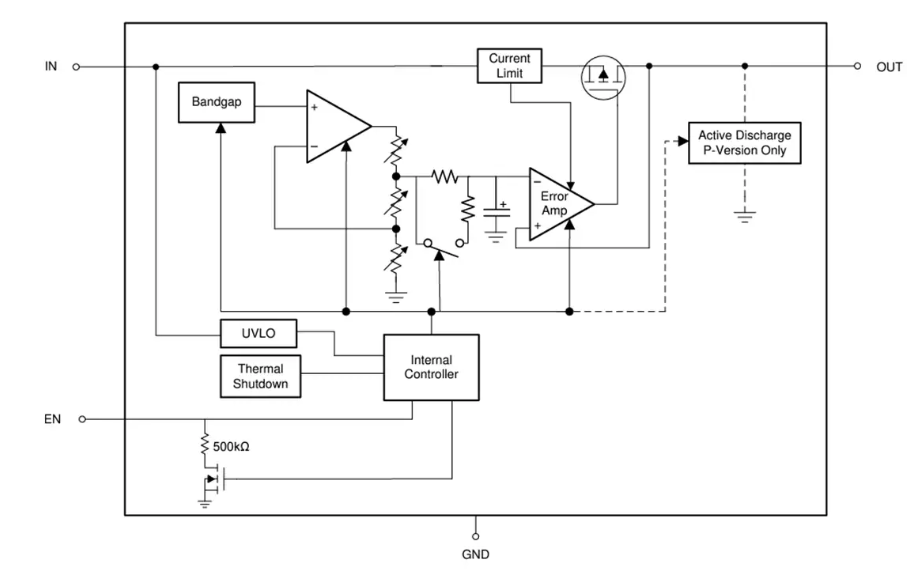

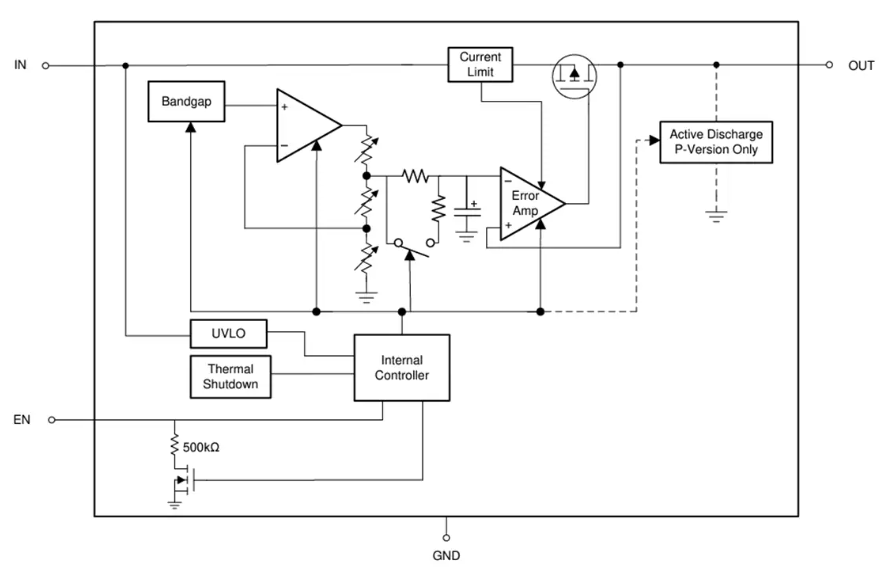

具有低噪聲輸出電壓和高紋波抑制性能LDO線性穩壓器的典型應用

1A 高精度、低噪聲 LDO 穩壓器TPS7A91數據表

2A 高精度、低噪聲 LDO 穩壓器TPS7A92數據表

500mA 高精度、低噪聲 LDO 電壓穩壓器TPS7A90數據表

超低噪聲、高 PSRR、低壓降線性穩壓器 (LDO)TPS7H1111-SP和TPS111-SEP數據表

TPS7A53A-Q1低噪聲(5.6 μVRMs)、低壓差線性穩壓器(LDO)手冊

Texas Instruments TPS7H1111超低噪聲LDO線性穩壓器數據手冊

Texas Instruments TPS7A20C低噪聲LDO線性穩壓器數據手冊

Texas Instruments TPS7A20L低噪聲、低IQ穩壓器數據手冊

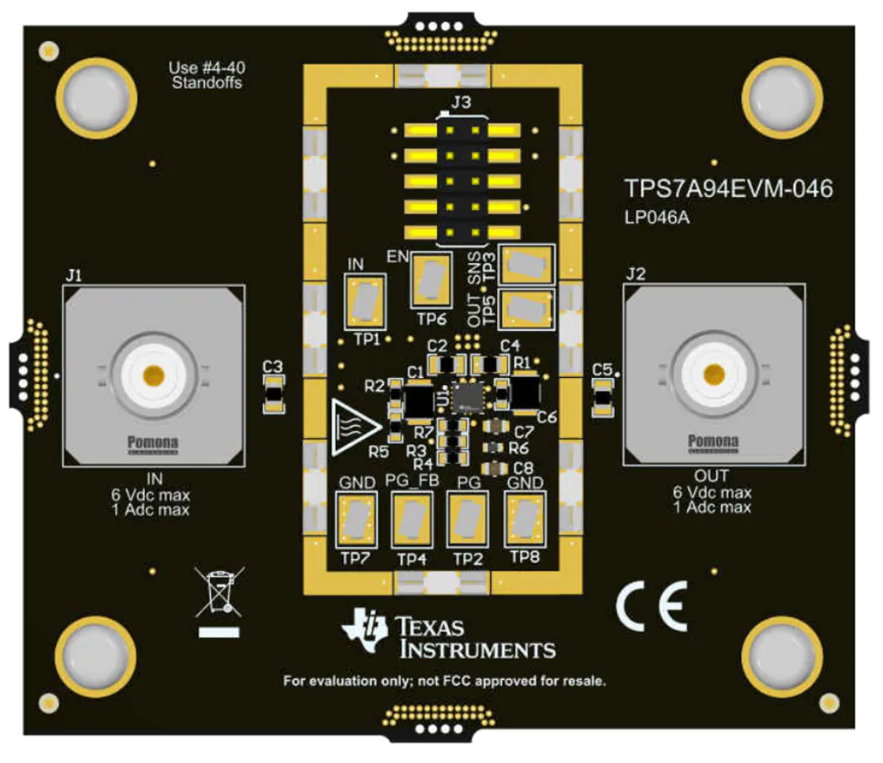

超低噪聲射頻LDO穩壓器TPS7A94評估模塊技術解析

TPS7N59:高性能低噪聲LDO穩壓器的設計與應用

TPS7N59:高性能低噪聲LDO穩壓器的設計與應用

評論